技术摘要:

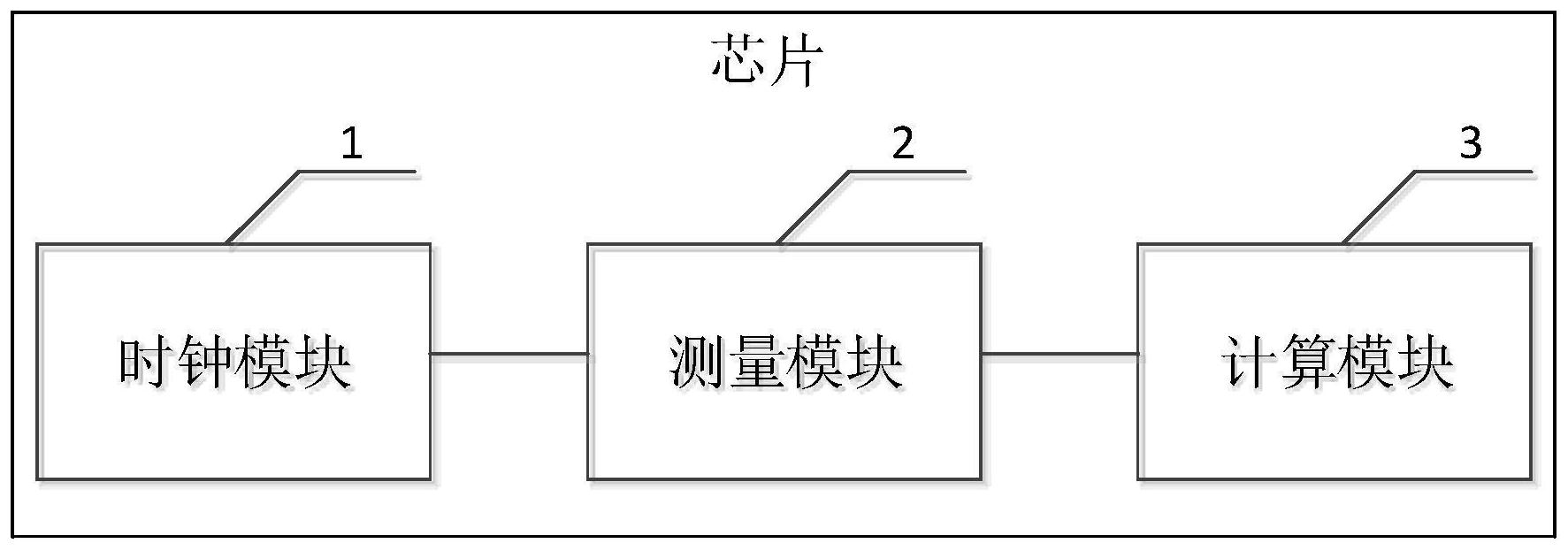

本发明公开了一种测量PWM占空比的集成电路及方法,该集成电路包括芯片及集成于芯片内部的时钟模块、测量模块及计算模块,该集成电路中,测量模块会基于基准时钟测量PWM的高电平时长及PWM的全周期时长,计算模块会根据PWM的高电平时长及PWM的全周期时长计算占空比。可见 全部

背景技术:

PWM(Pulse Width Modulation,脉冲宽度调制技术)广泛应用于测量、通信及功率 控制与变换等各种领域,其中,占空比是PWM的关键参数之一。比如在无刷电机驱动应用中, 可以直接通过调整PWM的占空比来控制无刷电机的转速。现有技术中,主要通过微处理器和 传感器相结合的方式测量占空比,但是微处理器和传感器均为分立器件,从而造成实际系 统的体积大,且可靠性也较差。

技术实现要素:

本发明的目的是提供一种测量PWM占空比的集成电路及方法,一方面,能实现对 PWM占空比的测量,另一方面,由于采用集成电路的方式,体积更小,可靠性较高。 为解决上述技术问题,本发明提供了一种测量PWM占空比的集成电路,包括芯片及 集成于所述芯片内部的时钟模块、测量模块及计算模块; 所述时钟模块用于提供基准时钟; 所述测量模块与所述时钟模块连接,用于基于所述基准时钟测量所述脉冲宽度调 制技术PWM的高电平时长及所述PWM的全周期时长; 所述计算模块与所述测量模块连接,用于根据所述PWM的高电平时长及所述PWM的 全周期时长计算占空比。 优选地,所述集成电路还包括集成于所述芯片内部的数据存储模块,用于保存所 述占空比。 优选地,所述数据存储模块为寄存器。 优选地,所述计算模块为算数逻辑单元。 优选地,所述测量模块包括: 检测模块,用于检测所述PWM的上升沿及下降沿; 与所述检测模块连接的第一计数器,用于在所述检测模块检测到所述PWM的上升 沿及所述PWM的上升沿之后的第一个下降沿的时间段内对接收到的所述基准时钟的个数进 行计数,将计数值作为所述PWM的高电平时长;在所述检测模块检测到所述PWM的上升沿及 所述PWM的上升沿之后的第一个上升沿的时间段内对接收到的所述基准时钟的个数进行计 数,将计数值作为所述PWM的全周期时长。 优选地,所述检测模块还用于根据自身检测到的所述PWM的上升沿和下降沿判断 所述PWM是否为一个完整的PWM波形; 若是,在检测到所述完整的PWM波形之后第一次检测到上升沿时生成第一触发信 号,在检测到所述完整的PWM波形之后第一次检测到下降沿时生成第二触发信号,在检测到 所述完整的PWM波形之后第二次检测到上升沿时生成第三触发信号; 4 CN 111614345 A 说 明 书 2/9 页 所述第一计数器,用于接收到所述第一触发信号时,开始对所述基准时钟的个数 进行累加计数,并在接受到第二触发信号时,将此时的计数值作为所述PWM的高电平时长并 继续计数;在接收到所述第三触发信号时,将此时的计数值作为所述PWM的全周期时长; 若否,重复根据自身检测到的所述PWM的上升沿和下降沿判断所述PWM是否为一个 完整的PWM波形的步骤。 优选地,还包括: 分别与所述时钟模块、所述检测模块及所述计算模块连接的第二计数器,用于对 接收到的所述基准时钟的个数进行计数,得到低电平计数值; 所述检测模块还用于在没有到检测高电平输入时,触发所述第二计数器清零并开 始计数,判断所述低电平计数值是否超过低电平阈值,若是,则触发所述计算模块将所述占 空比计为0。 优选地,所述检测模块还用于在检测到所述PWM的上升沿后,在接收到所述PWM的 上升沿的第一个下降沿之前,判断第一计数器的计数值是否大于全周期阈值,若是,则触发 所述计算模块将所述占空比计为1。 优选地,所述计算模块具体用于: 在每个计算周期开始时,将除数右移一位后与被除数进行比较,得到比较结果;其 中,除数为二进制的所述PWM的全周期时长,所述被除数为二进制的所述PWM的高电平时长; 其中,若右移后的所述除数小于所述被除数,则所述比较结果为1,并将所述被除 数减去右移后的所述除数的差值作为下一个计算周期的被除数,右移后的除数作为下一周 期的除数; 若右移后的所述除数不小于所述被除数,则所述比较结果为0,并将右移后的所述 除数作为下一个计算周期的除数,下一个计算周期被除数不变; 重复N次上述计算过程,得到浮点数的N个计算结果,以基于浮点数的N个计算结果 得到占空比,N为不小于2的整数。 为解决上述技术问题,本发明还提供了一种测量PWM占空比的方法,应用于集成电 路,该方法包括: 提供基准时钟; 基于所述基准时钟测量脉冲宽度调制技术PWM的高电平时长及所述PWM的全周期 时长; 根据所述PWM的高电平时长及所述PWM的全周期时长计算占空比。 本申请提供了一种测量PWM占空比的集成电路,该集成电路包括芯片及集成于芯 片内部的时钟模块、测量模块及计算模块,该集成电路中,测量模块会基于所述基准时钟测 量所述脉冲宽度调制技术PWM的高电平时长及所述PWM的全周期时长,计算模块会根据所述 PWM的高电平时长及所述PWM的全周期时长计算占空比。可见,一方面,该集成电路能实现对 PWM占空比的测量,另一方面,由于采用集成电路的方式,体积更小,可靠性较高。 本发明还提供了一种测量PWM占空比的方法,具有与上述测量PWM占空比的集成电 路相同的有益效果。 5 CN 111614345 A 说 明 书 3/9 页 附图说明 为了更清楚地说明本发明实施例中的技术方案,下面将对现有技术和实施例中所 需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施 例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获 得其他的附图。 图1为本发明提供的一种测量PWM占空比的集成电路的结构示意图; 图2为本发明提供的另一种测量PWM占空比的集成电路的结构示意图; 图3为本发明提供的一种测量PWM占空比的集成电路的工作流程原理图; 图4为本发明提供的一种测量PWM占空比的方法的过程流程图。