技术摘要:

本发明提供了一种带隙基准电路、带隙基准电压修调方法及电子装置,所述带隙基准电路包括带隙基准核心模块、自适应控制模块、预失调控制模块以及修调模块。本发明的技术方案电路结构和方法简单,能够通过遍历所有预设的预失调控制方式来对带隙基准电压进行预失调尝试, 全部

背景技术:

由于带隙基准电路(bandgap reference)可以产生与电源电压、工艺参数和温度 关系很小的参考电压,因此它广泛应用于模拟集成电路中,并做为一种稳定的参考源。由于 工艺制造的原因,各种工艺制造随机因素,例如:光刻精度,掺杂不均匀,杂质扩散浓度梯度 分布等,都会造成带隙基准电路中需要匹配的关键电路和模块的匹配精度下降。这种匹配 精度的下降,会导致带隙基准电路产生的参考电压呈现随机的分布。 图1所示为一种常见的带隙基准电路的核心电路结构。请参考图1所示,该带隙基 准电路包括PMOS管M0~ M2、运算放大器OP0、BJT三极管Q0~Q2以及电阻R0~R1。Vbg是带隙基 准电路所产生的带隙基准电压(即输出参考电压),且Vbg可以由以下公式表示: 上式中,Vbe2为BJT三极管 Q2的发射极-基极的结电压,R1、R0为电阻R1、R0的电阻值, K1为PMOS管M2与PMOS管M1的沟道宽、长比例系数,VT=kT/q,其中k为玻尔兹曼常数,T为绝对 温度,q为电子电量,K0为PMOS管M0与PMOS管M1的沟道宽、长比例系数,N为BJT三极管 Q1与 BJT三极管 Q0的发射结面积之比。 上述带隙基准电路的工艺制造中的随机因素,会导致以下参数出现随机分布(即 随机偏差):(1)PMOS管M1与PMOS管M0沟道宽、长比例系数K1出现随机分布;(2)PMOS管M2与 PMOS管M1沟道宽、长比例系数K0出现随机分布;(3)运算放大器OP0的输入/输出对管的比例 随机分布,因而产生一个随机的输入误差电压。 上述这些随机分布最终会反映到带隙基准电路所输出的带隙基准电压Vbg上,导 致Vbg产生随机偏差。 在大批量的芯片的测试数据的统计下,根据电路不同的设计方法取舍,这些随机 偏差一般会达到5%~20%。此外,在大批量的芯片的测试数据的统计下,这些随机分布会呈现 高斯分布。如果上述的需要匹配的关键电路和模块的匹配精度越低,那么统计的高斯分布 的标准方差sigma值就会越大。这种随机偏差会对芯片的性能带来负面影响,特别是一些特 殊应用场合,这些随机偏差是不可接受的。 现在常用的去除带隙基准电路中随机偏差的做法是,对每一片芯片进行测试后修 调(trimming),然而这极大的增加了芯片成本。

技术实现要素:

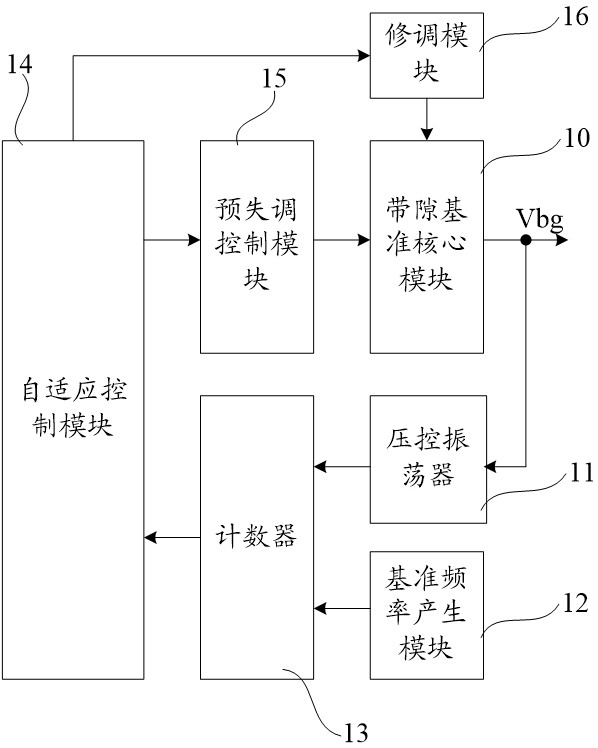

本发明的目的在于提供一种带隙基准电路、带隙基准电压修调方法及电子装置, 能够通过自适应的方法来消除带隙基准电路中的随机偏差,降低修调带隙基准电压的成本 并提高带隙基准电压的精度。 5 CN 111610814 A 说 明 书 2/13 页 为解决上述技术问题,本发明提供一种带隙基准电路,包括: 带隙基准核心模块,用于输出带隙基准电压; 自适应控制模块,用于针对所述带隙基准核心模块中的不同失配情况预设不同的预失 调控制方式,并在预失调尝试阶段遍历所有的预失调控制方式,以找到期望的中心频率或 期望的电压值,以及,在修调控制阶段,选定其中一种所述预失调控制方式并根据所述带隙 基准电压产生修调控制信号; 预失调控制模块,用于根据所述自适应控制模块输出的预失调控制方式,对所述带隙 基准核心模块所输出的带隙基准电压进行相应的预失调调节; 修调模块,用于在所述修调控制信号的控制下,对所述带隙基准核心模块所输出的带 隙基准电压进行修调,使得所述带隙基准电压所对应的频率达到或者最接近所述中心频 率,或者,使得所述带隙基准电压达到或最接近所述期望的电压值。 可选地,所述的带隙基准电路还包括: 压控振荡器,用于产生与所述带隙基准电压相对应的一稳定频率信号; 基准频率产生模块,用于产生基准频率; 计数器,用于在所述基准频率下对所述稳定频率信号进行计数,以得到相应的计数值; 所述自适应控制模块在所述预失调尝试阶段根据所有的预失调控制方式所对应的计 数值,找到期望的中心频率,并在所述修调控制阶段根据所述计数器的计数值产生相应的 修调控制信号,所述修调模块调节所述带隙基准核心模块所输出的带隙基准电压,使得所 述压控振荡器输出的稳定频率信号的频率达到或者最接近所述中心频率。 可选地,所述带隙基准核心模块包括至少两条用于产生相应电流的电流产生支 路,且其中一条所述电流产生支路还用于输出所述带隙基准电压;所述预失调控制模块包 括第一预失调控制开关,所述第一预失调控制开关连接各条所述电流产生支路,并连接所 述自适应控制模块的相应输出端,且在不同的预失调控制方式的控制下,输送到所述第一 预失调控制开关的每个输出节点的电流枝总数不变,但是构成每个输出节点的电流枝总数 的电流来源不同。 可选地,每条所述电流产生支路分别包括一个第一电流源,每个所述第一电流源 的输出端连接所述第一预失调控制开关相应的输入节点。 可选地,用于输出所述带隙基准电压的所述电流产生支路具有带隙基准电压节 点,所述修调模块包括第二电流源和修调开关,所述修调开关的第一输入端连接所述第二 电流源的输出端,所述修调开关的第二输入端连接所述第一预失调控制开关的相应的输出 节点,所述修调开关的第三输入端接入所述修调控制信号,所述修调开关的输出端连接所 述带隙基准电压节点,以输出修调后的带隙基准电压。 可选地,所述带隙基准核心模块还包括至少一个运算放大器,所述运算放大器的 同相输入端和反相输入端分别耦接所述第一预失调控制开关的相应的两个输出节点,所述 运算放大器的输出端耦接相应的所述电流产生支路的控制端,以控制所述电流产生支路所 产生的电流大小。 可选地,所述运算放大器包括输入级电路,所述输入级电路具有两个差分输入端; 所述预失调控制模块还包括第二预失调控制开关,所述第二预失调控制开关连接在所述运 算放大器的同相输入端、反相输入端与所述输入级电路的两个差分输入端之间,所述第二 6 CN 111610814 A 说 明 书 3/13 页 预失调控制开关用于在所述预失调控制方式的控制下,互换所述第一预失调控制开关的相 应的两个输出节点向所述两个差分输入端的输入。 可选地,所述输入级电路包括输入对管和第三电流源,所述第二预失调控制开关 包括第一二选一开关和第二二选一开关;所述输入对管的一个栅极作为所述输入级电路的 一个差分输入端,连接所述第一二选一开关的输出端,所述输入对管的另一个栅极作为所 述输入级电路的另一个差分输入端,连接所述第二二选一开关的输出端, 所述输入对管的 两个源极连接所述第三电流源的输出端,所述输入对管的两个漏极作为所述输入级电路的 输出端,所述第一二选一开关的控制端和所述第二二选一开关的控制端均接入所述第二预 失调控制信号,所述第一二选一开关的第一输入端和所述第二二选一开关的第二输入端均 连接所述运算放大器的同相输入端,以连接第一预失调控制开关的一个输出节点,所述第 一二选一开关的第二输入端和所述第二二选一开关的第一输入端均连接所述运算放大器 的反相输入端,以连接第一预失调控制开关的另一个输出节点。 可选地,所述运算放大器还包括输出级电路,所述输出级电路具有两个差分输出 端,所述预失调控制模块还包括第三预失调控制开关,所述第三预失调控制开关的两个输 入端分别连接所述输出级电路的两个差分输出端,所述第三预失调控制开关的输出端输入 端分别连接各个所述电流产生支路的控制端,所述第三预失调控制开关用于在所述预失调 控制方式的控制下,从所述输出级电路的两个差分输出端输出的信号中选择一个作为所述 运算放大器的最终输出。 可选地,所述预失调控制模块还包括第四预失调控制开关,所述第四预失调控制 开关的两个输入端分别连接所述输出级电路的两个差分输出端,所述第四预失调控制开关 的输出端连接所述输出级电路的控制端,所述第四预失调控制开关用于在所述预失调控制 方式的控制下,根据所述输出级电路的输出来调整所述输出级电路的输出。 基于同一发明构思,本发明还提供一种电子装置,包括本发明所述的带隙基准电 路。 基于同一发明构思,本发明还提供一种带隙基准电压修调方法,用于对一带隙基 准核心电路输出的带隙基准电压进行修调,所述带隙基准电压修调方法包括: 预失调尝试阶段:针对所述带隙基准核心模块中的不同失配情况预设不同的预失调控 制方式,并遍历所有的预失调控制方式,对所述带隙基准核心电路输出的带隙基准电压进 行不同的预失调调节,以找到期望的中心频率或期望的电压值; 修调控制阶段:选定其中一种所述预失调控制方式,并对所述带隙基准核心模块所输 出的带隙基准电压进行修调,使得所述带隙基准电压所对应的频率达到或者最接近所述中 心频率,或者,使得所述带隙基准电压达到或者最接近所述期望的电压值。 可选地,所述预失调尝试阶段包括: S11,选择一种所述预失调控制方式,以对所述带隙基准核心电路所输出的带隙基准电 压进行预失调调节; S12,产生与所述带隙基准核心电路当前输出的带隙基准电压相对应的第一稳定频率 信号; S13,采用基准频率对所述第一稳定频率信号进行计数,以得到相应的第一计数值; S14,循环执行S11~S13,直至遍历对所有的预失调控制方式; 7 CN 111610814 A 说 明 书 4/13 页 S15,根据所有的预失调控制方式所对应的第一计数值,找到期望的中心频率。 可选地,当所述带隙基准核心电路中具有多个存在失配的MOS管,且所有的所述存 在失配的MOS管所输出的电流均流入一预失调控制开关时,步骤S14中,在循环执行S11~S13 时,在不同的预失调控制方式的控制下,输送到所述预失调控制开关的每个输出节点的电 流枝总数不变,但是构成每个输出节点的电流枝总数的电流来源不同;当所述带隙基准核 心电路具有存在失配的运算放大器时,步骤S14中,在循环执行S11~S13时,不同的所述预失 调控制方式能切换所述运算放大器的两个输入端的输入,和/或,切换所述运算放大器的两 个输出端的输出。 可选地,所述修调控制阶段包括: S21,选择其中一种所述预失调控制方式作为最终的预失调控制方式; S22,在所述最终的预失调控制方式下,对所述带隙基准核心电路所输出的带隙基准电 压进行修调,以得到修调后的带隙基准电压; S23,产生与所述修调后的带隙基准电压相对应的第二稳定频率信号; S24,采用基准频率对所述第二稳定频率信号进行计数,以得到相应的第二计数值; S25,根据所述第二计数值判断所述第二稳定频率信号的频率是否达到所述中心频率, 若否,则循环执行S22~S25,若是,则此时的所述修调后的带隙基准电压为最终的带隙基准 电压。 与现有技术相比,本发明的技术方案具有以下有益效果: 1、本发明的带隙基准电路包括带隙基准核心模块、自适应控制模块、预失调控制模块 以及修调模块。自适应控制模块针对带隙基准核心电路中存在的失配情况已预设了不同的 预失调控制方式,并预失调尝试阶段能在遍历所有预失调控制方式时,对带隙基准核心电 路的带隙基准电压进行不同的预失调调节,进而找到期望的中心频率或期望的电压值,在 修调控制阶段,当最终选择其中一种预失调控制方式后,自适应控制模块可以通过修调模 块来对带隙基准核心电路的带隙基准电压进行修调,以让修调后的带隙基准电压达到或最 接近所述期望的电压值,或者让修调后的带隙基准电压所对应的频率达到或最接近中心频 率。由此,实现了对带隙基准电压进行预失调尝试和自适应调节的方法,提高了带隙基准电 压的精度电路,且电路结构简单,可以集成到芯片中制造,由此可以避免对每一芯片进行测 试后修调的工艺,因此能够降低芯片成本,即降低了修调带隙基准电压的成本。 2、进一步地,本发明的带隙基准电路还包括压控振荡器、基准频率产生模块、计数 器,由此能够通过压控振荡器将带隙基准电压转换为稳定的频率信号,并通过计数器在基 准频率产生模块产生的基准频率下对压控振荡器的输出频率进行计数,由此可以使得自适 应控制模块可以根据所有预失调控制方式所对应的计数值来快速找到期望的中心频率,由 此能够提高带隙基准电路的动态响应性能。 3、本发明的带隙基准电路修调方法,针对带隙基准核心电路中存在的失配情况已 预设了相应的预失调控制方式,进而通过遍历所有预失调控制方式的方式,来改变带隙基 准核心电路的输出,以找到期望的中心频率或期望的电压值,进而基于一种预失调控制方 式来进一步对带隙基准核心电路的输出进行修调,以使得带隙基准核心电路的输出能达到 或最接近期望的电压值,由此可以消除带隙基准电路中的运算放大器和MOS管等结构的失 调,大大提高了带隙基准电压的精度。 8 CN 111610814 A 说 明 书 5/13 页 附图说明 图1是现有的一种带隙基准电路的核心电路结构示意图。 图2是本发明一实施例的带隙基准电路的系统模块示意图。 图3是图2所示的带隙基准电路中的预失调控制模块、修调模块和带隙基准电路核 心模块的具体电路结构示意图。 图4是图2所示的带隙基准电路中的预失调控制模块连接运算放大器的具体电路 结构的一种示例示意图。 图5是图2所示的带隙基准电路中的预失调控制模块连接运算放大器的具体电路 结构的另一种示例示意图。 图6是图2所示的带隙基准电路中的预失调控制模块连接运算放大器的具体电路 结构的又一种示例示意图。 图7是本发明一实施例的带隙基准电路的带隙基准电压修调方法的流程示意图。 图8是本发明另一实施例的带隙基准电路的系统模块示意图。