技术摘要:

提供一种能够对地址进行加扰的半导体系统。根据一个实施例的半导体系统包括模块控制器和被配置为从模块控制器接收逻辑地址的多个半导体芯片。该半导体系统还包括多个加扰电路,其为多个半导体芯片中的每个半导体芯片提供加扰电路,所述多个加扰电路被配置为接收逻辑地 全部

背景技术:

通常,半导体存储器件可以包括被划分为多个组的多个存储单元。存储单元可以 按所述组来被控制。存储单元组可以被称为存储单元阵列或MAT。控制块可以布置在存储单 元阵列之间的边界处。存储单元阵列可以由控制块来单独地控制。 可以在与控制块相邻的存储单元(在下文中,被称为相邻单元)与远离控制块的存 储单元(在下文中,被称为远单元)之间产生信号传输特性之间的差异。特别地,在使用相变 材料作为开关元件和储存介质的交叉点阵列中,可能在相邻单元中频繁产生错误。 与此同时,半导体集成电路器件的错误比特位测试可以对半导体芯片单元、存储 体单元或MAT单元执行。可以对半导体芯片、存储体和MAT同时执行错误比特位测试。当测试 相邻单元时,与其他区域相比,相邻单元中的错误率可能会显著地增大。尽管考虑到存储体 和MAT,相邻单元区域中的错误可能不会达到令人担忧的程度,但是误差率的瞬时增大可能 导致半导体芯片、存储体和MAT的低成品率。

技术实现要素:

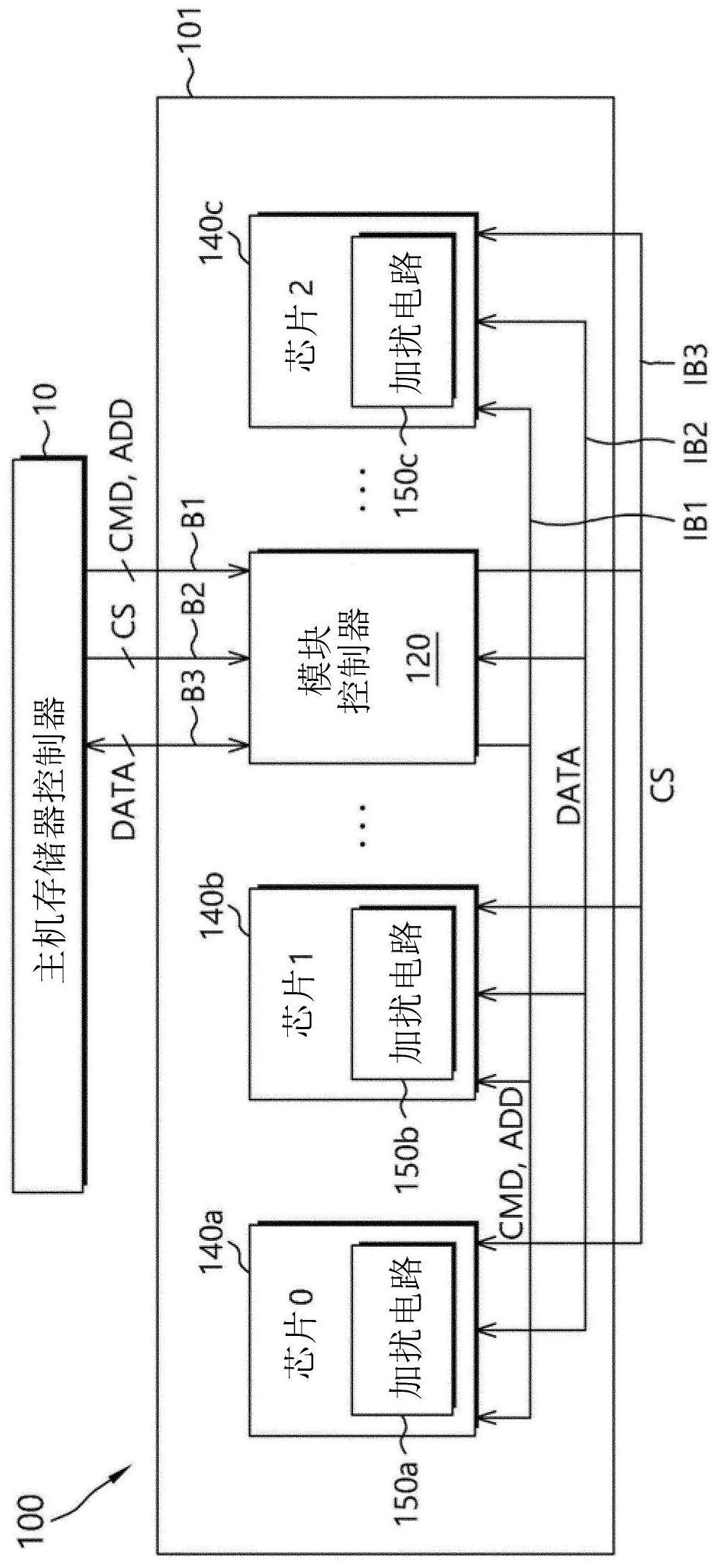

根据本公开的一个实施例,半导体系统包括模块控制器和被配置为从模块控制器 接收逻辑地址的多个半导体芯片。该半导体系统还包括多个加扰电路,其为多个半导体芯 片中的每个半导体芯片提供加扰电路,所述多个加扰电路被配置为接收逻辑地址并且针对 多个半导体芯片输出对应物理地址。多个加扰电路中的每个加扰电路被配置为接收相同的 逻辑地址并且输出与由多个加扰电路的其他加扰电路输出的物理地址不同的对应物理地 址。 根据本公开的另一个实施例,一种半导体系统包括模块基板和安装在模块基板上 的多个半导体芯片。该半导体系统还包括模块控制器,该模块控制器被配置为向每个半导 体芯片提供逻辑地址和地址比特位测试命令。该半导体系统还包括加扰电路,其为每个半 导体芯片提供加扰电路,该加扰电路被配置为基于地址比特位测试命令来将逻辑地址转换 为物理地址。加扰电路被配置为针对被给定相同逻辑地址的每个半导体芯片产生不同的物 理地址。 4 CN 111599401 A 说 明 书 2/6 页 附图说明 从下面结合附图的详细描述中,将更清楚地理解本公开的主题的上述和其他方 面、特征和优点,其中: 图1是示出根据一个实施例的半导体模块的框图; 图2是示出根据一个实施例的加扰电路的框图; 图3是示出图2的行加扰电路的电路图; 图4是示出图2的列加扰电路的电路图; 图5、图6和图7是示出根据一个实施例的行地址加扰操作的示图; 图8、图9和图10是示出根据一个实施例的列地址加扰操作的示图;以及 图11A、图11B和图11C是示出根据半导体芯片的位置的比特位错误率的曲线图。