技术摘要:

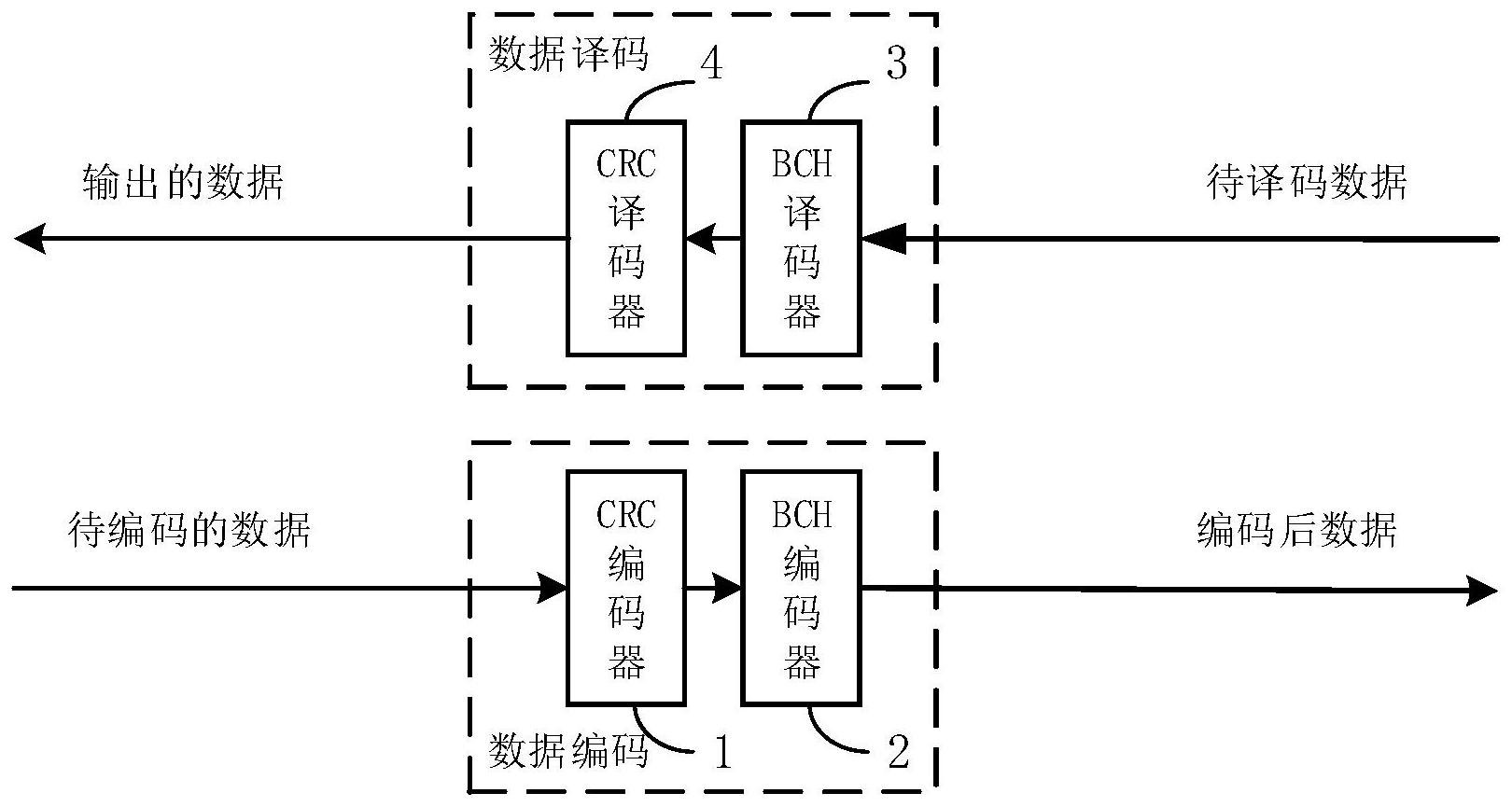

本发明公开了一种差错控制编码ECC系统,包括循环冗余码校验CRC编码器、BCH编码器、BCH译码器和CRC译码器;CRC编码器连接BCH编码器,BCH译码器连接CRC译码器,BCH编码器与BCH译码器建立通信连接;CRC编码器用于对待编码数据进行CRC编码,获得CRC码;BCH编码器用于对CRC 全部

背景技术:

随着数字技术的不断发展,目前社会正处于一个大数据的时代,大量数据需要进 行可靠的存储和传输,这就需要差错控制编码(ECC)技术的支持,以保证数据在传输和存储 过程中较高的正确率。现有的ECC系统通常基于BCH编码技术,BCH码是在1959年由Bose、 Chaudhuri及Hocquenghem各自独立发现的二元线性循环码,是一种得到广泛应用的线性分 组码,它具有多比特纠错能力,其硬件电路实现相对简单;人们可以根据需求的纠错能力, 构造具有特定纠错范围的BCH码的ECC系统。 BCH编码数据在存储或传输过程中会产生错误,除此之外,BCH编码、译码过程本身 也存在一定的误码率,对于大数据传输中的ECC系统,BCH码的误码率导致数据出错的次数 会随着数据量的增加而显著增多;当数据中的错误数据量超出了该BCH码的纠错能力范围 时,经过BCH译码电路译码后的数据可能会出现更多的错误,而此时BCH译码电路本身并没 有可以检测出数据的出错量是否溢出纠错范围的情况,且对超出纠错能力的数据无法实现 正确纠错。虽然在设计BCH码时,已经综合考虑了纠错能力设计与信息传输效率(码率)、硬 件资源占用之间的矛盾,尽可能的确定出最佳的纠错能力设计,但在BCH编码后的数据存储 或传输过程中的不确定因素,会导致BCH编码后的数据随机出现大量突发性的软错误,容易 超过常用的BCH码的纠错能力设计,导致解码后的数据中存在错误,而在BCH解码过程中并 不能检测或确定出这一问题的存在;此时若继续增加BCH码的纠错能力,则将消耗大量硬件 资源;而维持原先纠错能力设计,则可能输出错误数据;而在系统级应用中,错误数据的输 出可能会直接导致系统出错,导致事故和经济损失。

技术实现要素:

本发明提供了一种差错控制编码ECC系统及包括ECC系统的存储器设备,以解决或 者部分解决现有的基于BCH码技术的ECC系统无法判断待解码数据中的错误量是否超过了 BCH码的纠错能力设计,造成解码后的数据准确度存疑,影响系统稳定的技术问题。 为解决上述技术问题,本发明提供了一种差错控制编码ECC系统,包括循环冗余码 校验CRC编码器、BCH编码器、BCH译码器和CRC译码器;CRC编码器连接BCH编码器,BCH译码器 连接CRC译码器,BCH编码器与BCH译码器建立通信连接; CRC编码器用于对待编码数据进行CRC编码,获得CRC码; BCH编码器用于对CRC码进行BCH编码,获得BCH码,并将BCH码发送至BCH译码器; BCH译码器用于接收BCH码并进行译码,获得BCH译码数据; CRC译码器用于对BCH译码数据进行CRC译码,获得CRC译码数据和CRC校验结果, CRC校验结果用于判断BCH译码数据中是否存在错误数据。 4 CN 111597072 A 说 明 书 2/9 页 可选的,ECC系统还包括ECC控制器,ECC控制器与CRC译码器建立通信连接; ECC控制器用于从CRC译码器中获取CRC校验结果,并根据CRC校验结果,判断BCH译 码数据中是否存在错误数据。 进一步的,当CRC校验结果为校验正确结果时,ECC控制器判断BCH译码数据中不存 在错误数据,ECC控制器输出数据正确状态信号,并控制CRC译码器将CRC译码数据发出。 进一步的,当CRC校验结果为校验错误结果时,ECC控制器判断BCH译码数据中存在 错误数据,ECC控制器控制CRC译码器删除CRC译码数据; ECC控制器发出数据重读信号,以使BCH译码器重新接收BCH码并进行译码,CRC译 码器重新对BCH译码数据进行CRC译码,ECC控制器重新根据CRC校验结果,判断BCH译码数据 中是否存在错误数据。 可选的,在ECC控制器连续发出n次数据重读信号后,判断BCH译码数据中仍然存在 错误数据时,ECC控制器输出数据错误状态信号,并控制CRC译码器将CRC译码数据发出;其 中,n≥2且为正整数。 如上述的技术方案,CRC编码器用于将待编码数据分为m块第一信息序列,m≥2且 为正整数;对m块第一信息序列进行CRC编码,生成m块CRC子码;将m块CRC子码合并为CRC码; CRC译码器用于将BCH码分块,获得m块第二信息序列;对m块第二信息序列进行CRC 译码,获得m块CRC译码子数据和m个CRC校验结果;其中,CRC译码子数据的信息长度与CRC子 码的信息长度相同;将m块CRC译码子数据合并为CRC译码数据; ECC控制器根据m个CRC校验结果中是否包括一个以上的校验错误结果,判断BCH译 码数据中是否存在错误数据。 基于前述技术方案相同的发明构思,本发明还提供了一种存储器设备,包括差错 控制编码ECC系统和存储器,ECC系统包括CRC编码器、BCH编码器、BCH译码器和CRC译码器; BCH编码器连接在CRC编码器与存储器之间,BCH译码器连接在CRC译码器与存储器之间; CRC编码器用于对待编码数据进行CRC编码,获得CRC码; BCH编码器用于对CRC码进行BCH编码,获得BCH码,并将BCH码发送至存储器; BCH译码器用于从存储器中读取BCH码并进行译码,获得BCH译码数据; CRC译码器用于对BCH译码数据进行CRC译码,获得CRC译码数据和CRC校验结果, CRC校验结果用于判断BCH译码数据中是否存在错误数据。 可选的,存储器设备还包括ECC控制器,ECC控制器与CRC译码器建立通信连接; ECC控制器用于从CRC译码器中获取CRC校验结果,并根据CRC校验结果,判断BCH译 码数据中是否存在错误数据。 进一步的,ECC控制器与存储器建立通信连接; 当CRC校验结果为校验错误结果时,ECC控制器判断BCH译码数据中存在错误数据, ECC控制器控制CRC译码器删除CRC译码数据; ECC控制器向存储器发送数据重读信号;存储器根据数据重读信号,重新读取BCH 码并向BCH译码器发送重读后的BCH码,BCH译码器重新对BCH码进行译码,CRC译码器重新对 BCH译码数据进行CRC译码,ECC控制器重新根据CRC校验结果,判断BCH译码数据中是否存在 错误数据。 可选的,在ECC控制器连续发出n次数据重读信号后,判断BCH译码数据中仍然存在 5 CN 111597072 A 说 明 书 3/9 页 错误数据时,ECC控制器输出数据错误状态信号,并控制CRC译码器将CRC译码数据发出;其 中,n≥2且为正整数。 通过本发明的一个或者多个技术方案,本发明具有以下有益效果或者优点: 本发明提供了一种基于BCH与CRC的二级编码和译码的ECC系统,通过在编码阶段 时先进行CRC编码再进行BCH编码,译码阶段时先进行BCH译码再进行CRC译码,以增加很小 的编译码复杂度和电路成本,使数据在译码阶段能够通过CRC校验及时检测BCH解码后的数 据中是否含有错误数据,从而进一步确定待BCH解码的数据中的数据错误量是否溢出了BCH 码纠错能力,以保证输出数据的可靠性和系统的稳定性。 上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段, 而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够 更明显易懂,以下特举本发明的