技术摘要:

本发明实施例公开了一种用于极化编码的方法、装置和设备,能够降低系统的存储开销。该方法包括:获取N个极化信道的可靠性的度量值,其中,N=2n,n和N为正整数;按照度量值从小到大或从大到小的顺序,对N个极化信道的序号进行排序,得到最大母码序列,最大母码序列满足 全部

背景技术:

通信系统通常采用信道编码提高数据传输的可靠性,保证通信的质量。极化 (Polar)码是理论上证明可以取得香农容量,且具有简单的编码和译码方法的编码方式。 P o l a r码是一种线性块码。其生成矩阵为G N ,其编码过程为 其中 , 是一个二进制的行矢量, 码长N=2n,其中,n为正整数。 是F2的克罗内克乘积,定义为 Polar码的编码过程中, 中的一部分比特用来携带信息,称为信息比特,这些信 息比特的序号的集合记作A。另外的一部分比特置为收发端预先约定的固定值,称之为固定 比特,其序号的集合用A的补集Ac表示。不失一般性,这些固定比特通常被设为0。实际上,只 需要收发端预先约定,固定比特序列可以被任意设置。从而,Polar码的编码比特序列可通 过如下方法得到: 这里 为 中的信息比特集合, 为长度K的行矢量,即 |·|表示集合中元素的数目,即K表示集合A中元素的数目, 是矩阵GN中由集 合A中的索引对应的那些行得到的子矩阵。 是一个K×N的矩阵。在CRC辅助的增强SC 译码算法下,Polar码可以获取优于LDPC和Turbo码的FER性能。 Polar码编码的关键取决于码长M和信息比特集合A的确定。已有的Polar码编码方 案中,信息比特集合A的确定都不能通过简单的计算得到。因此,现有技术中大多采用离线 计算存储的方式来确定,即,编码器和译码器预先存储多个母码序列与码长、码率的对应关 系表。在进行Polar码编码时,根据所需的码率、码长从中选择对应的母码序列。 现有技术中,为了支持系统要求的所有码长和码率的组合,需要存储大量的母码 序列。因此,系统的存储开销极大。

技术实现要素:

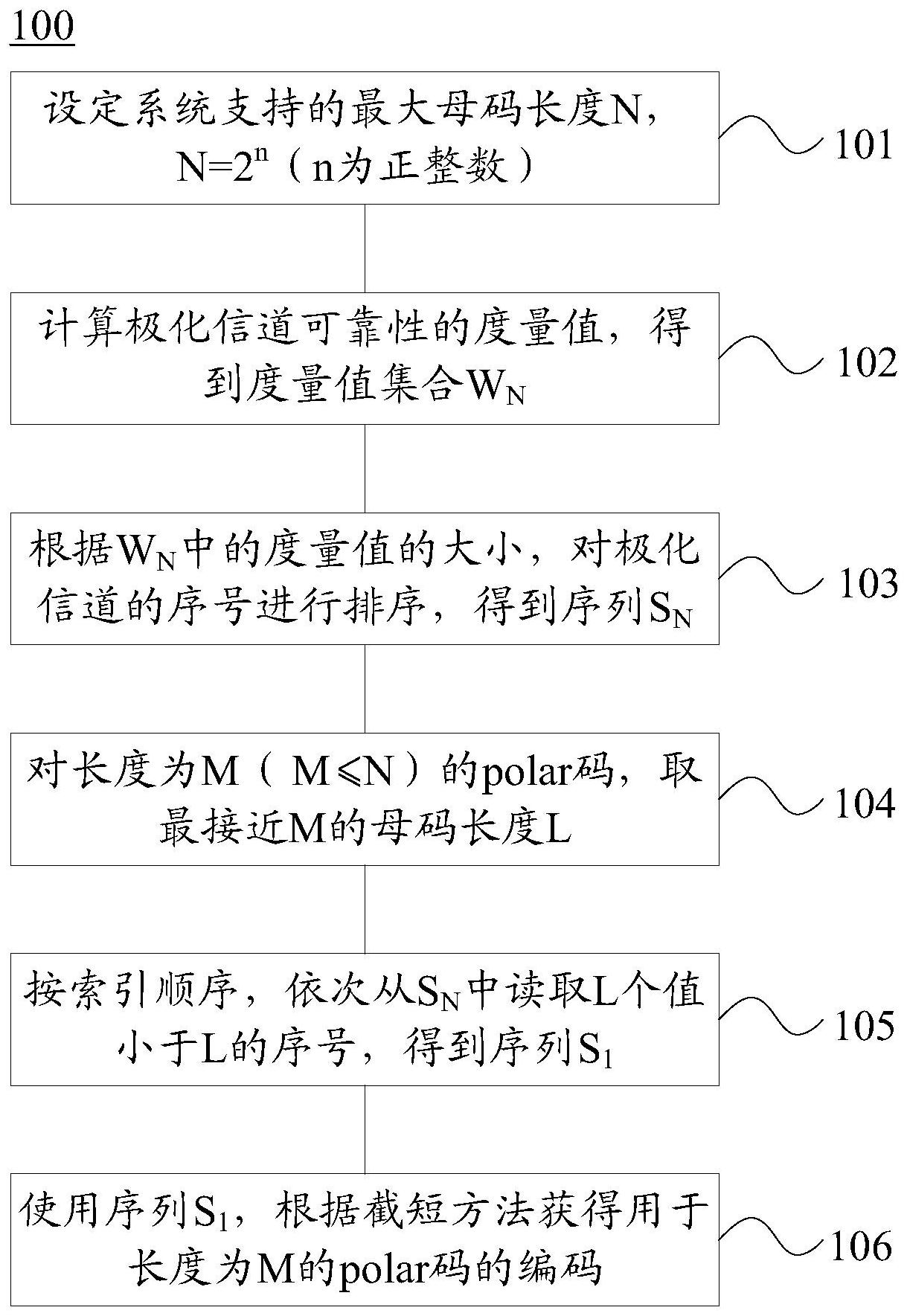

本申请提供一种用于极化编码的方法、装置和设备,能够降低系统的存储开销。 第一方面,本申请提供了一种用于极化编码的方法,该方法包括:获取N个极化信 道的可靠性的度量值,其中,N=2n,n和N为正整数;按照度量值从小到大或从大到小的顺 序,对N个极化信道的序号进行排序,得到最大母码序列,该最大母码序列满足性质:若从最 大母码序列中读取码长为Z的第一序列,第一序列中包括的Z个序号在第一序列中的排序与 Z个序号在最大母码序列中的排序一致,其中,Z=2z,z≤n,z为正整数;存储该最大母码序 列。 4 CN 111614361 A 说 明 书 2/140 页 应理解,最大母码序列是指系统所能支持的最大长度的序列,并且,最大母码序列 的长度N=2n,n为正整数。第一序列是指从最大母码序列中读取的包括任意码长(最大长度 为N)的序列。 在现有技术中,系统需要一个母码长度存储一个序列。并且,在母码长度相同的情 况下,不同的码率对应不同的序列,因此,系统需要存储所有码长、码率组合对应的序列,采 用这样的存储方式,硬件系统的存储开销是极大的。 在本发明实施例中,仅存储系统所能支持的最大母码序列(即,仅存储一个序列)。 在进行Polar码编码时,从最大母码序列中读取所需长度的母码序列,再基于极化码打孔的 方法进行速率匹配和编码即可。与现有技术相比,系统需要存储的母码序列的数量减少,进 而可以降低系统的存储开销。 在一种可能的实现方式中,该方法还包括:根据目标Polar码的码长M,从最大母码 序列中确定第二序列,第二序列用于作为目标Polar码编码时的母码序列,其中,第二序列 中包括L个序号,该L个序号在第二序列中的排序和该L个序号在最大母码序列中的排序一 致,其中,M≤L≤N,M和L为正整数。 应理解,第二序列是针对需要获取的Polar码(即,目标Polar码)而言的。对于一个 给定的目标Polar码的码长M,从最大母码序列中读取的作为目标Polar码编码时的母码序 列的序列,即为第二序列。 还应理解,上述L=2b,b≤n,b为正整数。 在一种可能的实现方式中,根据目标Polar码的码长M,从最大母码序列中确定第 二序列,包括:根据目标Polar码的码长M,确定目标Polar码的母码码长L;从最大母码序列 中依次读取小于L的序号,得到第二序列。 需要说明的是,在本发明实施例中,极化信道的序号从0开始,因此,N个极化信道 的序号范围为0至N-1。 可以理解的是,上述第一序列泛指从最大母码序列中读取的序列。这里,第二序列 是指针对目标Polar码的码长为M时,从最大母码序列中读取的用于作为目标Polar码的母 码的序列。 在一种可能的实现方式中,根据所述目标Polar码的码长M,确定目标Polar码的母 码码长L,包括:当M=2m时,L=M;当M≠2m时, 其中,m为正整数,符号 表示向 上取整。 在一种可能的实现方式中,存储该最大母码序列,包括:根据最大母码序列的长度 和预设规则,计算表示最大母码序列中的序号时需要使用的比特的数目S;计算使用(S-1) 个比特所能表示的最大序列长度Q;将最大母码序列中序号小于所述Q的序号依次排列得到 的序列确定为基础序列;将最大母码序列中大于或等于所述Q的序号划分为 个偏 移序列,每个偏移序列中包括的序号的数目与基础序列中包括的序号的数目相同,且每个 偏移序列中的第i个序号与基础序列中的第i个序号对应,其中,0≤i≤Q-1,i为非负整数; 使用S个比特存储最大母码序列中属于基础序列中的每个序号,该S个比特包括第一比特和 多个第二比特,该第一比特用于指示当前位置存储的序号属于基础序列,该多个第二比特 用于指示当前位置所存储的序号的大小;使用S个比特存储最大母码序列中属于偏移序列 5 CN 111614361 A 说 明 书 3/140 页 的每个序号,该S个比特包括第三比特和多个第四比特,该第三比特用于指示当前位置存储 的序号属于偏移序列,该多个第四比特用于指示当前位置所存储的序号的与基础序列中对 应位置所存储的序号的偏移倍数,其中,偏移倍数为当前位置存储的序号与基础序列中对 应位置的序号之间的差值除以基础序列的长度,该第一比特与该第三比特相异。 需要说明的是,在本发明实施例中,确定存储最大母码序列中的序号所需要使用 的比特数目S时,是基于最大母码序列的长度N和预设规则计算得到的。在本发明实施例中, 预设规则可以理解为系统预先配置的关系式N=22S-2,其中,N为最大母码序列长度,S为表 示最大母码序列中的每个序号时所使用的比特数。基于上述关系式,对于任意长度的最大 母码序列,都可以计算出使用本发明实施例提供的压缩存储的方法进行存储时,需要使用 的比特数目。 因此,在系统仅需要存储一个最大母码序列,能够降低系统存储开销的基础上,对 最大母码序列采用本发明实施例提出的压缩存储的方法进行存储,可以减少表示最大母码 序列中的每个序号时使用的比特数目,因而,可以进一步降低系统的存储开销。 在一种可能的实现方式中,获取N个极化信道的可靠性的度量值,包括: 根据如下关系式获取该N个极化信道的可靠性的度量值: 其中,N=2n,n为正整数,i=Bn-1Bn-2… .B0,Bn-1 Bn-2….B0是i的二进制表示,Bn-1为最高位,B0为最低位,Bj∈{0,1},Wi用于表征第i个极化信 道的可靠性。 应理解,极化权重可以作为衡量极化信道可靠性的参数。因此,在本发明实施例 中,在计算极化信道的可靠性时,可选地,可以采用上述公式计算得到N个极化信道的极化 权重。一个极化信道的极化权重越大,代表这个极化信道的可靠性越高。 在一种可能的实现方式中,获取N个极化信道的可靠性的度量值,包括: 使用密度进化或者高斯近似获取N个极化信道的错误概率。一个极化信道的错误 概率越低,代表这个极化信道的可靠性越高。根据错误概率对极化信道进行排序,并对排序 后的序列中不满足本发明实施例中最大母码序列所应满足的性质的极化信道的序号的顺 序进行调整,从而得到本发明实施例的最大母码序列。 在一种可能的实现方式中,该方法还包括:将第二序列作为目标Polar码的母码序 列,根据截短的方法获取该目标Polar码。 需要说明的是,这里,截短(英文名称:Shorten)为Polar码打孔方式中的一种。 第二方面,本申请提供了一种用于极化编码的装置,用于执行第一方面或第一方 面的任意可能的实现方式中的方法。具体地,该装置包括用于执行第一方面或第一方面的 任意可能的实现方式中的方法的单元。 第三方面,本申请提供了一种用于极化编码的设备。具体地,该设备包括:存储器、 处理器和网络接口,其中,存储器、处理器和网络接口通过总线系统相互连接。该存储器用 于存储指令,该处理器用于执行该存储器存储的指令,当该指令被执行时,该处理器通过该 网络接口执行第一方面或第一方面的任意可能的实现方式中的方法。 第四方面,本申请提供一种计算机可读介质,用于存储计算机程序,该计算机程序 6 CN 111614361 A 说 明 书 4/140 页 包括用于执行第一方面或第一方面的任意可能的实现方式中的方法的指令。 在本发明实施例中,系统仅存储所能支持的最大母码序列(即,存储一个序列),在 进行极化码编码时,再从最大母码序列中读取所需长度的母码序列,能够降低系统的存储 开销。 附图说明 为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例中所需要使 用的附图作简单地介绍,显而易见地,下面所描述的附图仅仅是本发明的一些实施例,对于 本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他 的附图。 图1是本发明实施例的用于极化编码的方法100的示意性流程图。 图2示出了根据本发明实施例的从最大母码序列中读取任意码长的序列的示意 图。 图3是根据本发明实施例的存储最大母码序列的一种形式。 图4是采用直接存储的方式存储最大母码序列的示意图。 图5是根据本发明实施例的存储最大母码序列的另一种形式。 图6是根据本发明实施例的用于极化编码的装置的示意性框图。 图7是根据本发明实施例的用于极化编码的设备的示意性结构图。