技术摘要:

本发明公开一种半导体封装产品的制造方法及半导体封装产品,包括在芯片以及内脚上进行上胶操作,于上胶操作前将芯片的点胶面与内脚的点胶面高度差设置为±0.05㎜,于芯片以及内脚上进行的上胶操作采用钢网印刷的方式一次进行。通过调整引线框架设计,搭配固定的芯片厚度 全部

背景技术:

功率半导体模块就是按一定功能、模式的组合体,功率半导体模块是大功率电子 电力器件按一定的功能组合再灌封成一体。功率半导体模块可根据封装的元器件的不同实 现不同功能,功率半导体模块配用风冷散热可作风冷模块,配用水冷散热可作水冷模块等。 功率半导体封装现在越来越多的选择铜桥取代金属导线,以适应更高功率的应用 需求。这种芯片需要源极面积越大越好,所以会尽量缩小栅极面积,目前市面上应用于铜桥 焊接的最小栅极尺寸已做到0.3㎜×0.3㎜,并且有进一步缩小的趋势。 现有铜桥焊接工艺中多采用在芯片上方的源极和栅极进行传统的气动点锡工艺, 该工艺通过气压控制出锡量,传统点锡工艺可以应用在芯片点锡表面比管脚点锡表面低或 高的设计中,在引线框架一定的情况下,芯片厚度不受限制,其具有巨大优势。 但是传统的点胶焊接铜桥的工艺在栅极为0.3㎜×0.3㎜时已经无法满足使用要 求,原因如下: 1.锡膏内有锡粉颗粒,在点锡针筒直径小于0.4㎜时会出现针筒堵塞,针筒堵塞后 无法出胶形成焊接导致开路; 2.把点锡针筒的直径设置在0.4㎜或以上时,其点出的锡直径至少为0.5㎜,点锡 太多会导致焊接铜桥后短路。 因此现在亟需提供一种半导体封装产品的制造方法,用于实现小栅极尺寸的半导 体封装产品的生产加工。

技术实现要素:

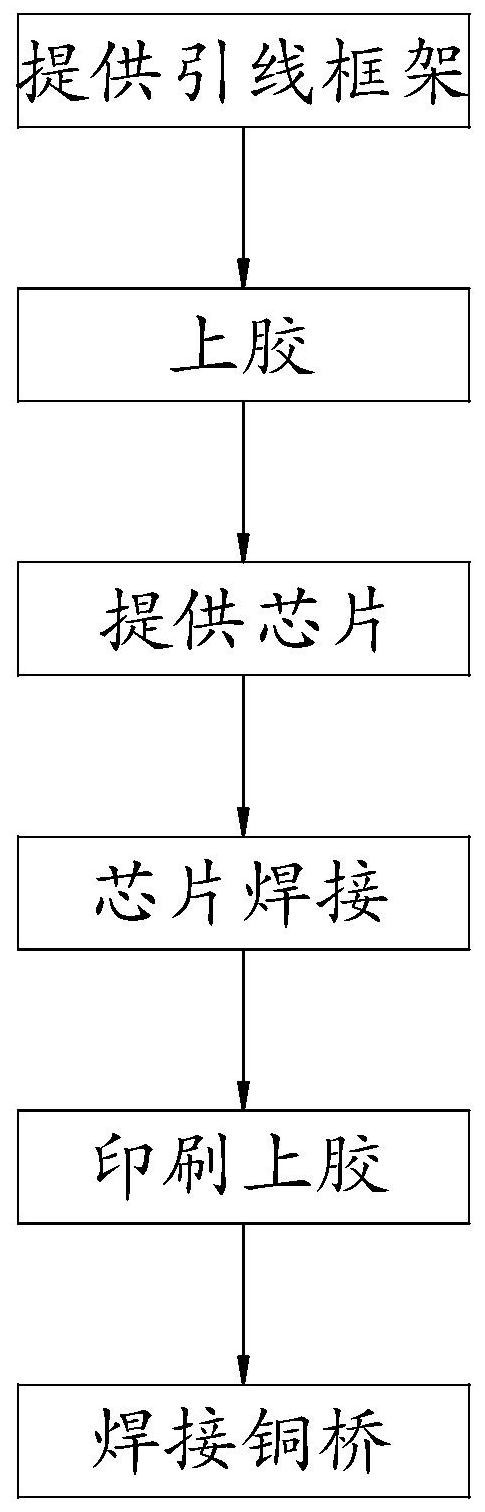

本发明实施例的目的在于:提供一种半导体封装产品的制造方法,其能够避免出 现点胶工艺中出现的针孔堵塞无法出胶无法焊接导致开路,或针孔过大导致出较量大产品 短路的问题。 本发明实施例的另一个目的在于:提供注意半导体封装产品,其栅极尺寸小,能够 满足高功率半导体产品的使用要求。 为达上述目的,本发明采用以下技术方案: 提供一种半导体封装产品的制造方法,包括在芯片以及内脚上进行上胶操作,其 特征在于,于所述上胶操作前将所述芯片的点胶面与所述内脚的点胶面高度差设置为± 0.05㎜,于所述内脚的所述在芯片以及内脚上进行的上胶操作采用钢网印刷的方式一次进 行。 作为所述的半导体封装产品的制造方法的一种优选的技术方案,其具体包括以下 步骤: 3 CN 111599699 A 说 明 书 2/5 页 S1、提供引线框架,提供具有芯片焊接区以及引脚区的引线框架; S2、上胶,在所述芯片焊接区以及所述引脚区进行上胶操作; S3、提供芯片,提供与所述引线框架尺寸相对应的芯片; S4、芯片焊接,将上述芯片焊接在所述引线框架上的芯片焊接区; S5、印刷上胶,在所述芯片的点胶面以及所述内脚的点胶面进行上胶操作,所述上 胶操作采用钢网印刷的方式进行; S6、焊接铜桥,采用铜桥连接所述芯片与所述内脚。 作为所述的半导体封装产品的制造方法的一种优选的技术方案,所述引线框架包 括芯片焊接区以及引脚区,所述引脚区与所述芯片焊接区的高度差为所述芯片的高度。 作为所述的半导体封装产品的制造方法的一种优选的技术方案,步骤S2所述上胶 采用点胶工艺或钢网印刷工艺进行。 作为所述的半导体封装产品的制造方法的一种优选的技术方案,步骤S5中所述印 刷上胶所用印刷胶材为锡膏。 作为所述的半导体封装产品的制造方法的一种优选的技术方案,所述钢网印刷中 采用钢网的厚度为0.05㎜-0.10㎜。 作为所述的半导体封装产品的制造方法的一种优选的技术方案,所述钢网印刷中 采用钢网上的开口尺寸可达0.25㎜×0.25㎜。 另一方面,提供一种半导体封装产品,其采用如上所述的半导体封装产品的制造 方法制造而成。 作为所述的半导体封装产品的一种优选的技术方案,包括芯片及引线框架,所述 引线框架包括框架本体和引脚,所述框架本体上具有用于焊接芯片的芯片焊接区,所述芯 片焊接在所述芯片焊接区,焊接芯片后所述芯片远离所述引线框架的表面与所述引脚的点 胶面之间的表面高度差为±0.05㎜。 作为所述的半导体封装产品的一种优选的技术方案,所述芯片远离所述引线框架 的表面具有源极以及栅极,所述源极和所述栅极分别通过铜桥与所述引脚连接。 本发明的有益效果为:通过调整引线框架设计,搭配固定的芯片厚度,保证芯片上 锡表面和管脚上锡表面的高度差在±0.05㎜以内,利用钢网在印刷时具有的贴合性(可变 形)来填补这个高度差,从而可以实现采用平面钢网印刷工艺一次性印刷出芯片表面的锡 膏和管脚上的锡膏;将钢网的厚度设置为0.05㎜至0.10㎜,钢网上的开窗尺寸在0.25㎜× 0.25㎜,从而保证栅极的锡膏印刷尺寸符合小尺寸栅极要求,克服气动点锡的缺陷。 附图说明 下面根据附图和实施例对本发明作进一步详细说明。 图1为本发明实施例所述半导体封装产品的制造方法流程图。 图2为本发明实施例所述引线框架结构示意图。 图3为图2所示结构剖视图。 图4为本发明实施例所述引线框架点锡膏后结构示意图。 图5为图4所示结构剖视图。 图6为本发明实施例所述引线框架焊接芯片后结构示意图。 4 CN 111599699 A 说 明 书 3/5 页 图7为图6所示结构剖视图。 图8为本发明实施例所述在芯片及引脚上印刷锡膏后结构示意图。 图9为图8所示结构剖视图。 图10为本发明实施例所述焊接铜桥后结构示意图。 图11为图10中A-A向剖视图。 图12为图10中B-B向剖视图。 图中: 100、引线框架;110、引脚;200、芯片;210、源极;220、栅极;300、锡膏;400、铜桥。