技术摘要:

本发明提供了一种转移管的垂直栅的形成方法,包括:提供衬底;在所述衬底上形成沟槽;在所述沟槽内和所述衬底上形成至少两层隔离层和至少两层栅极,所述隔离层和所述栅极间隔形成,第一层隔离层覆盖所述沟槽的底部、所述沟槽的侧壁以及部分所述衬底的表面,最后一层栅 全部

背景技术:

CMOS图像传感器在过去十几年得到了飞速发展,现已广泛应用于手机、电脑、数码 照相机等领域。为了迎合市场需求,在单位面积内集成更多像素单元,CMOS图像传感器的像 素尺寸已经从5.6mm逐渐缩小至1.0mm。可是,像素尺寸的缩小不能简单等价于缩小光电二 极管(Photodiode)各方向的尺寸,这是由于光电二极管有效满阱容量(FWC)的限制。如果尺 寸太小,导致不能存储足够的电子,那么图像质量会严重退化。 通常CMOS图像传感器的一个有源像素单元包含位于P型衬底100中的一个P /N / P-光电二极管200(PD,Photo Diode)和若干晶体管,以4T结构CMOS图像传感器为例,四个晶 体管具体包括转移管300(TX,Transfer)、源极跟随管400(SF,Source Follow)、复位管500 (RST,Reset)和行选择管600(RS,Row Select)。图1示出了4T结构CMOS图像传感器的示意 图。其基本工作原理是这样的:光照前,打开复位管500和转移管300,将光电二极管200区域 的原有的电子释放;在光照时,关闭所有晶体管,在光电二极管200空间电荷区产生电荷;读 取时,打开转移管300,将存储在PD区的电荷传输到浮动扩散节点700(FD,Floating Diffusion),传输后,转移管关闭,并等待下一次光照的进入。在浮动扩散节点700上的电荷 信号随后用于调整源极跟随管400,将电荷转变为电压,并通过行选择管600将电流输出到 模数转换电路中。 其中,在转移管300关闭进行感光的过程中,P-N结捕获太阳光产生电子和空穴,光 生电子在P-N结内建电场的作用下,向顶部积聚,在转移管300打开时,经过表面沟道传输至 浮动扩散节点700,进而被读取,为了增加电子转移的速度和效率,将转移管的栅极做成垂 直栅极的可以将沟道延伸至光电二极管深处。电子传输沟道由平面沟道变为立体沟道,电 子的传输通道倍增,光生电子传输速率大幅增加,而且沟道的深入能够降低二极管内的电 子残留,提升光生电子的利用率,最终提升光电二极管的满阱容量。随着像素尺寸的减小, 以及为了改善电子残留,垂直栅极的在持续加深,垂直栅极越深,图像质量越好。然而,随着 垂直栅极的加深,想要使得垂直栅极的掺杂离子变得均匀的难度在增大,现有的通过额外 退火的方式也不能达到完全均匀的掺杂。

技术实现要素:

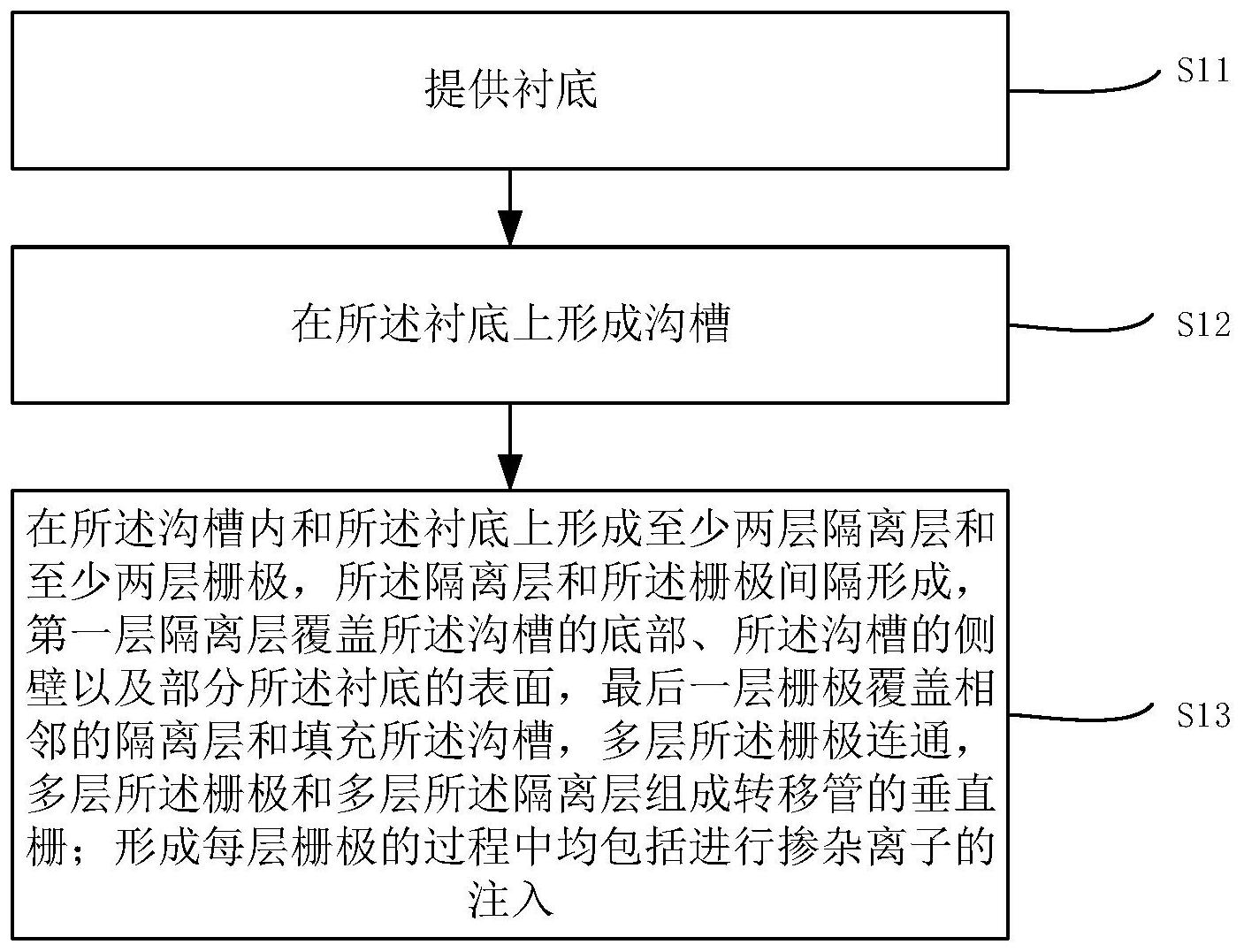

本发明的目的在于提供一种转移管的垂直栅及CMOS传感器的形成方法,可以使得 形成的栅极内的掺杂离子的浓度更加均匀,防止在向栅极施加电压后,导致低浓度掺杂离 子区域的掺杂离子耗尽使转移管的速度降低的问题产生,从而提高CMOS传感器的性能。 为了达到上述目的,本发明提供了一种转移管的垂直栅的形成方法,包括: 提供衬底; 4 CN 111584532 A 说 明 书 2/5 页 在所述衬底上形成沟槽; 在所述沟槽内和所述衬底上形成至少两层隔离层和至少两层栅极,所述隔离层和 所述栅极间隔形成,第一层隔离层覆盖所述沟槽的底部、所述沟槽的侧壁以及部分所述衬 底的表面,最后一层栅极覆盖相邻的隔离层和填充所述沟槽,多层所述栅极连通,多层所述 栅极和多层所述隔离层组成转移管的垂直栅;形成每层栅极的过程中均包括进行掺杂离子 的注入。 可选的,在所述的转移管的垂直栅的形成方法中,在所述沟槽内和所述衬底上形 成两层隔离层和两层栅极,两层隔离层分别是第一隔离层和第二隔离层,两层栅极分别是 第一栅极和第二栅极,所述第一层隔离层覆盖所述沟槽的底部、所述沟槽的侧壁以及部分 所述衬底的表面,所述第一栅极覆盖所述第一隔离层,所述第二隔离层覆盖位于所述沟槽 底部和所述沟槽侧壁的所述第一栅极以及部分覆盖位于所述衬底上的所述第一栅极,所述 第二栅极覆盖所述第二隔离层和所述第二隔离层未覆盖的所述第一栅极,所述第一栅极和 所述第二栅极连通。 可选的,在所述的转移管的垂直栅的形成方法中,在所述沟槽内和所述衬底上形 成两层隔离层和两层栅极的方法包括: 形成覆盖所述沟槽底部、所述沟槽侧壁和所述衬底表面的第一隔离层; 在所述第一隔离层上形成覆盖所述第一隔离层的第一多晶硅层,并且向所述第一 多晶硅层注入掺杂离子形成第一栅极; 在所述第一栅极上形成覆盖位于所述沟槽底部和所述沟槽侧壁的所述第一栅极 以及部分覆盖位于所述衬底上的所述第一栅极的第一隔离层; 在所述第二隔离层上形成覆盖所述第二隔离层和所述第二隔离层未覆盖的所述 第一栅极的第二多晶硅层,并且向所述第二多晶硅层注入掺杂离子形成第二栅极。 可选的,在所述的转移管的垂直栅的形成方法中,在形成所述第二栅极之后,所述 转移管的垂直栅的形成方法还包括:在所述第二栅极上依次形成第三隔离层和控制栅。 可选的,在所述的转移管的垂直栅的形成方法中,所述第一隔离层、所述第二隔离 层和所述第三隔离层的材料均为氧化物。 可选的,在所述的转移管的垂直栅的形成方法中,所述第一隔离层的厚度为65埃 ~85埃;所述第二隔离层的厚度为50埃~80埃。 可选的,在所述的转移管的垂直栅的形成方法中,所述第一多晶硅层的厚度小于 所述第二多晶硅层的厚度。 可选的,在所述的转移管的垂直栅的形成方法中,第一多晶硅层的厚度为100埃~ 300埃;第二多晶硅层的厚度为700埃~900埃埃。 可选的,在所述的转移管的垂直栅的形成方法中,向所述第一多晶硅层和所述第 二多晶硅层注入的离子相同。 本发明还提供了一种垂直栅CMOS传感器的形成方法,包括: 在该衬底上形成P阱以及位于P阱中横向间隔的两个N 区; 在所述衬底中形成光电二极管,与所述光电二极管相邻的一个所述N 区形成浮动 扩散点; 在所述光电二极管与所述浮动扩散点之间形成具有转移管的垂直栅的形成方法 5 CN 111584532 A 说 明 书 3/5 页 而制成的垂直栅的转移管,所述垂直栅的深度延伸至所述光电二极管所在的深度; 形成位于所述两个N 区之间的复位管。 在本发明提供的一种转移管的垂直栅及CMOS传感器的形成方法中,形成了多层栅 极,每层栅极的形成过程中,均会进行掺杂离子的注入,最后形成的多个栅极连通作为转移 管的垂直栅,即形成垂直栅的过程中分开进行了多次掺杂离子注入,可以使得转移管的垂 直栅内的掺杂离子的浓度更加均匀,防止在向垂直栅施加电压后,导致低浓度掺杂离子区 域的掺杂离子耗尽使转移管的速度降低的问题产生,从而提高CMOS传感器的性能。 附图说明 图1是4T结构CMOS图像传感器的示意图; 图2现有技术的转移管的垂直栅的结构示意图; 图3是本发明实施例的转移管的垂直栅的形成方法的流程图; 图4至图8是本发明实施例的转移管的垂直栅的形成方法的结构示意图; 图9为转移管的垂直栅的示意图; 图中:10-衬底、20-垂直栅、100-垂直栅、110-衬底、120-沟槽、130-第一隔离层、 140-第一栅极、151-氧化物层、152-第二隔离层、160-第二栅极。