技术摘要:

一种半导体结构及其形成方法,半导体结构包括:衬底,所述衬底上具有若干鳍部;多个存储单元,各所述存储单元包括横跨所述鳍部的栅极,以及位于所述栅极两侧的所述鳍部内的源漏掺杂区;凹槽,位于相邻所述存储单元之间的所述衬底内;隔离叠层,填充满所述凹槽,所述隔 全部

背景技术:

在半导体制造中,随着集成电路特征尺寸持续减小,MOSFET的沟道长度也相应不 断缩短。然而,随着器件沟道长度的缩短,器件源极与漏极之间的距离也随之缩短,导致栅 极对沟道的控制能力随之变差,造成短沟道效应(SCE:short-channel effects)更容易发 生。 鳍式场效应晶体管(FinFET)在抑制短沟道效应方面具有突出的表现,FinFET的栅 极至少可以从两侧对鳍部进行控制,因而与平面MOSFET相比,FinFET的栅极对沟道的控制 能力更强,能够很好的抑制短沟道效应。 但是,现有技术的半导体器件的沟道应力仍有待改进。

技术实现要素:

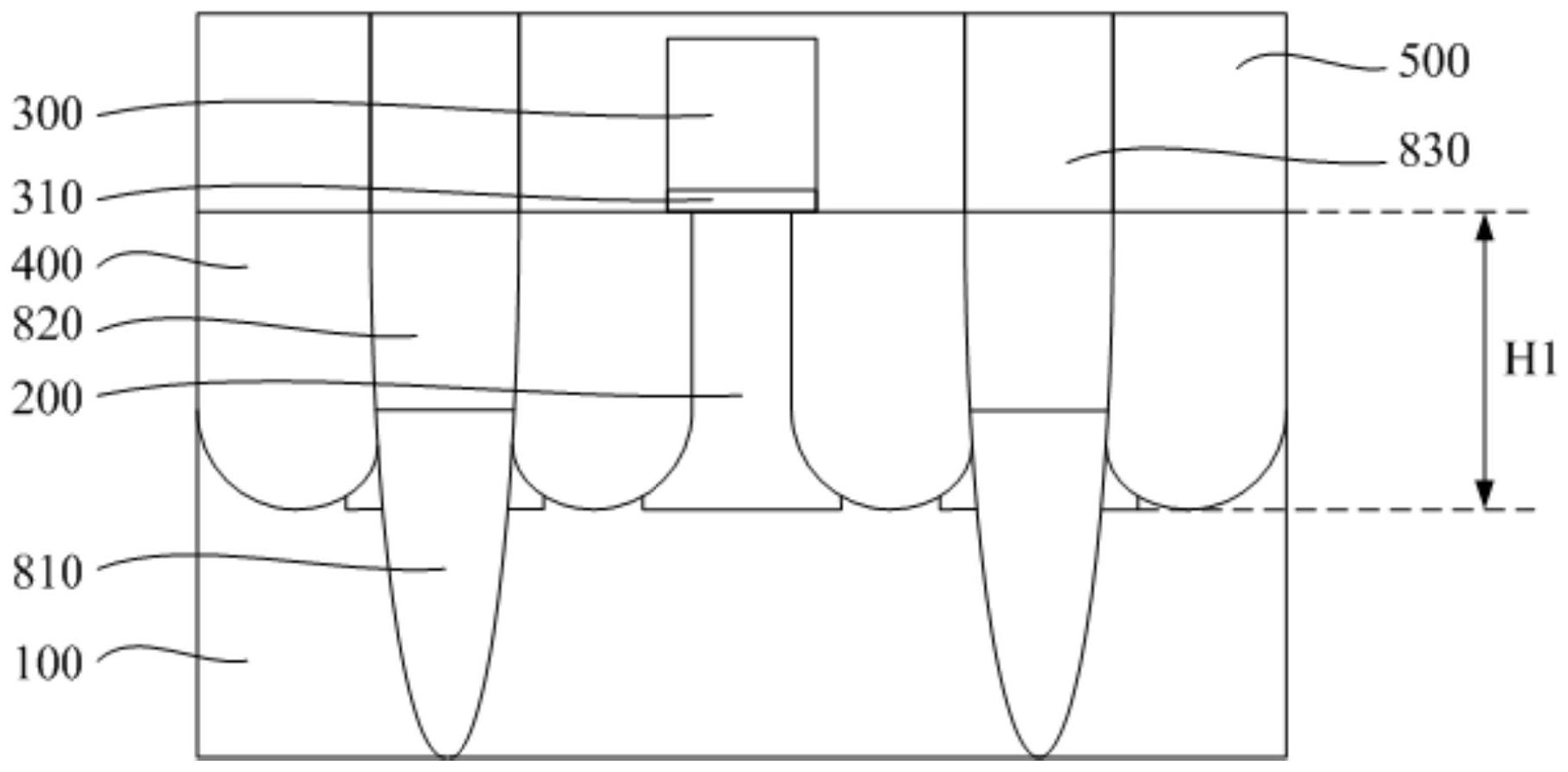

本发明解决的问题是提供一种半导体结构及其形成方法,有助于提高所述源漏掺 杂区对沟道的应力。 为解决上述问题,本发明提供一种半导体结构,包括:衬底,所述衬底上具有若干 鳍部;多个存储单元,各所述存储单元包括横跨所述鳍部的栅极,以及位于所述栅极两侧的 所述鳍部内的源漏掺杂区;凹槽,位于相邻所述存储单元之间的所述衬底内;隔离叠层,填 充满所述凹槽,所述隔离叠层包括若干个膜层,所述隔离叠层中位于所述凹槽最底部的所 述膜层的硬度最小。 可选的,各所述存储单元还包括:位于所述源漏掺杂区上的介质层,所述介质层覆 盖所述栅极的顶部和侧壁,所述凹槽贯穿所述介质层厚度。 可选的,所述膜层的数量为两个或三个。 可选的,当所述膜层的数量为两个时,所述隔离叠层包括第一膜层及位于所述第 一膜层上的第二膜层。 可选的,当所述膜层的数量为三个时,由所述凹槽的底部至顶部,依次为第一膜 层、第二膜层和第三膜层。 可选的,所述第一膜层的材料为氧化硅。 可选的,所述第二膜层的材料为氮化硅或非晶碳。 可选的,所述第三膜层的硬度大于所述第一膜层的硬度,且所述第三膜层的硬度 小于所述第二膜层的硬度。 可选的,所述第三膜层的材料为氮化硅或非晶碳。 可选的,所述第一膜层及所述第二膜层的厚度总和为所述鳍部厚度的3倍至5倍。 可选的,所述第一膜层厚度为所述鳍部厚度的1倍至1.2倍。 可选的,所述第三膜层厚度为所述鳍部厚度的1.5倍至2倍。 4 CN 111725208 A 说 明 书 2/6 页 可选的,所述鳍部厚度为50nm~70nm。 可选的,沿平行于所述鳍部延伸方向,所述凹槽的宽度为30nm~50nm。 相应的,本发明还提供一种半导体结构形成方法,包括:提供衬底,所述衬底上具 有若干鳍部;形成多个存储单元,各所述存储单元包括横跨所述鳍部的栅极,以及位于所述 栅极两侧的所述鳍部内的源漏掺杂区;在相邻所述存储单元之间的所述衬底内形成凹槽; 形成填充满所述凹槽的隔离叠层,所述隔离叠层包括若干个膜层,所述隔离叠层中位于所 述凹槽最底部的所述膜层的硬度最小。 可选的,形成所述存储单元的工艺中,还包括:在相邻所述存储单元间的所述鳍部 上形成临时栅极,所述临时栅极与所述栅极间隔排列。 可选的,形成所述凹槽的工艺包括:刻蚀去除所述临时栅极及位于所述临时栅极 底部的所述鳍部及衬底,形成所述凹槽。 与现有技术相比,本发明的技术方案具有以下优点: 由于在相邻所述存储单元之间的凹槽内具有隔离叠层,且各所述存储单元包括横 跨鳍部的栅极,以及位于所述栅极两侧的所述鳍部内的源漏掺杂区,因此所述源漏掺杂区 位于所述隔离叠层与所述鳍部之间。所述隔离叠层包括若干个膜层,其中,位于所述凹槽最 底部的所述膜层的硬度最小,其余所述膜层的硬度较大,有助于抵挡所述源漏掺杂区对所 述隔离叠层的应力释放,使得所述源漏掺杂区对沟道区域具有较强的挤压作用,从而可提 高所述源漏掺杂区对沟道的应力。 附图说明 图1是本发明半导体结构一实施例中的结构示意图; 图2至图7是本发明半导体结构形成方法一实施例中各步骤对应的结构示意图。