技术摘要:

本发明实现具备适于层间绝缘膜的耐压检查的构造的半导体集成电路。电压施加区域(13)与电压施加用焊盘(11)通过将密封圈(14)与中继区域利用通孔(16)进行连接,从而形成相互绝缘的、分别不同的耐压测定用布线,上述分别不同的耐压测定用布线通过向电压施加区域(13)与电压 全部

背景技术:

以往,半导体工艺的小型化牵引着电子设备的小型化、低价化。然而,另一方面,若 在单位面积中被装入的晶体管数增大,则将晶体管间连接的布线条数也增大,因此若仅是 布线宽度、布线间隔的缩小,空间不足,需要布线的多层化。当前,布线的多层化达到10层以 上。 伴随着这样的布线的多层化,由布线层间的绝缘耐压不良引起的半导体集成电路 的故障的可能性也变高。层间膜厚由于制造偏差、负载效应,在晶圆面内进一步在半导体集 成电路内也产生偏差。根据情况不同,有时层间膜厚以偏离管理值的程度变薄。当对那样的 层间膜厚比假设薄的区域施加了高电场的情况下,即使层间的电位差为规格范围内,也担 心发生层间膜绝缘破坏。 由于层间膜绝缘破坏而使半导体集成电路不正常动作,在最坏的情况下,也有时 发生由电位反转引起的闩锁,成为冒烟、着火的原因。因此,在半导体集成电路制造后,需要 通过进行内部的布线层的层间绝缘膜的耐压检查,来对担心发生层间膜绝缘破坏的产品进 行筛选。 例如,专利文献1所公开的技术通过在单个的晶圆的所有半导体集成电路形成区 域形成层间耐压试验专用的布线层,从而能够在每个该形成区域进行半导体集成电路的层 间耐压试验。 另外,专利文献2所公开的技术通过在具有多层布线构造的半导体装置中,在芯片 上的动作电路区域的外侧的区域设置层间耐压不良检测用的区域(监控元件),从而能够进 行半导体装置的层间耐压试验。 现有技术文献 专利文献专利文献1:日本特开平5-166911号公报 专利文献2:日本特开平6-85025号公报

技术实现要素:

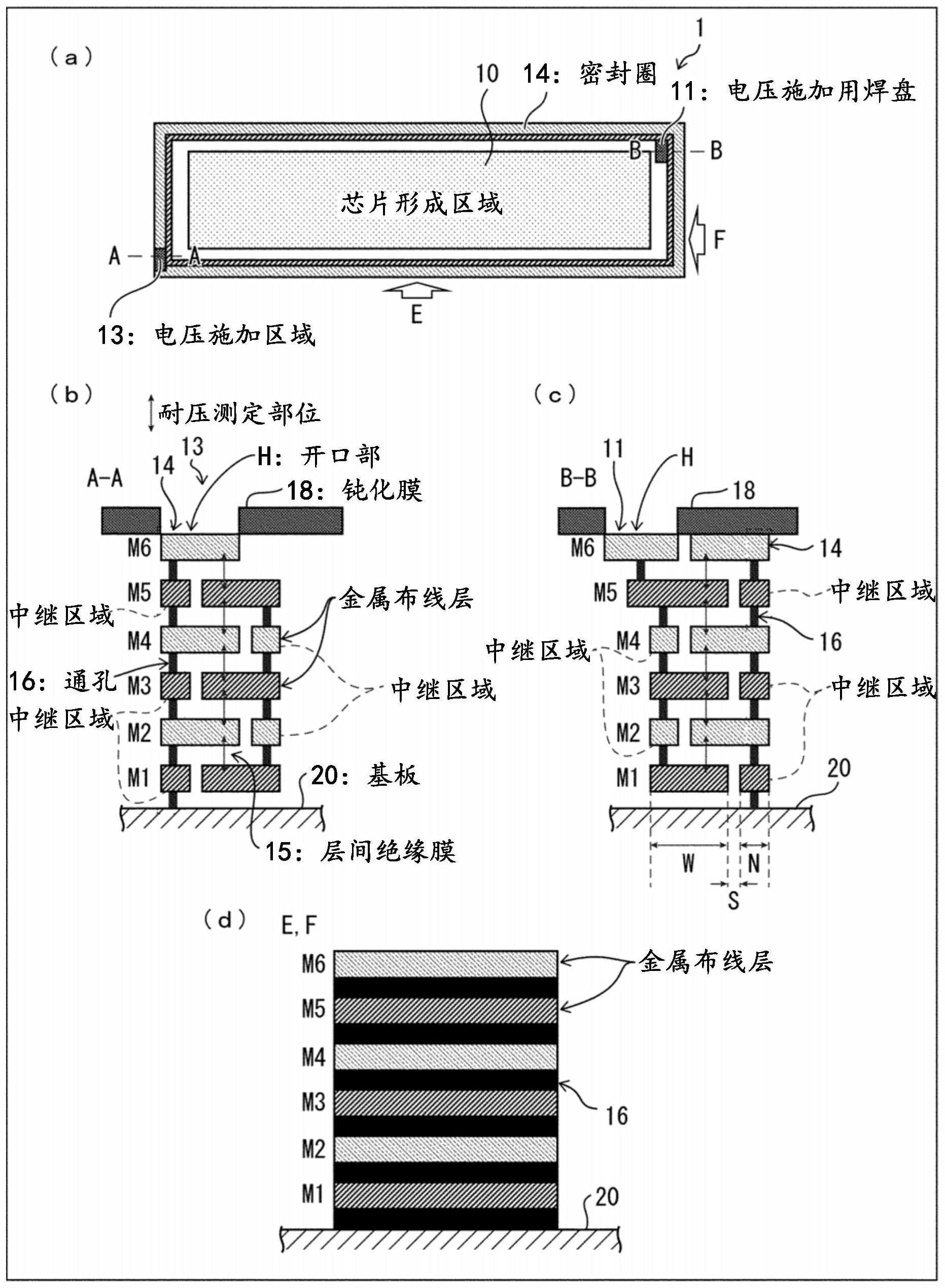

本发明所要解决的技术问题 然而,在专利文献1所公开的技术中,用于层间耐压试验的专用的布线层由于仅设 置于半导体集成电路的一部分,因此存在如下问题,即:为不易检测伴随着半导体集成电路 内的层间膜厚偏差的层间膜薄膜化作为原因的绝缘耐压不良的构造,为不适于层间绝缘膜 的耐压检查的构造。 另外,在专利文献2所公开的技术中,存在如下问题,即:在多层布线构造中,不易 分别实施各层间膜的绝缘耐压不良的检测,为不适于层间绝缘膜的耐压检查的构造。 3 CN 111599794 A 说 明 书 2/9 页 本发明的一个方式是鉴于上述的问题所做出的,其目的在于实现具备适于层间绝 缘膜的耐压检查的构造的半导体集成电路等。 解决问题的方案 (1)本发明的一个实施方式为一种半导体集成电路,其具备:芯片形成区域,其具 有层叠有多个布线层的层叠构造;多个密封圈,它们以包围上述芯片形成区域的外侧的方 式配置,并具有与上述芯片形成区域相同的层叠构造,上述多个密封圈由金属布线构成;多 个中继区域,它们配置在上述芯片形成区域的外侧,并具有与上述芯片形成区域相同的层 叠构造,上述多个中继区域由金属布线构成;多个通孔,它们形成在相互邻接的上述布线层 之间;以及电压施加区域及电压施加用焊盘,它们设置于上述多个布线层中的、在表面上形 成有上述芯片形成区域及上述密封圈的处于最远离基板的位置的布线层,上述电压施加区 域与上述电压施加用焊盘通过将上述密封圈与上述中继区域利用上述通孔连接,而形成相 互绝缘的、分别不同的耐压测定用布线,上述分别不同的耐压测定用布线通过向上述电压 施加区域与上述电压施加用焊盘之间施加电压,而能够向设置于相互邻接的上述布线层且 绝缘的密封圈间施加电压。 (2)在上述(1)的结构的基础上,对于本发明的某一实施方式的半导体集成电路而 言,还具备第二电压施加用焊盘,通过连接上述电压施加用焊盘的耐压测定用布线和连接 上述电压施加区域的耐压测定用布线施加电压的、在设置于相互邻接的上述布线层且绝缘 的密封圈间形成的层间绝缘膜的厚度与通过连接上述第二电压施加用焊盘的耐压测定用 布线和连接上述电压施加区域的耐压测定用布线施加电压的、在设置于相互邻接的上述布 线层且绝缘的密封圈间形成的层间绝缘膜的厚度不同。 (3)在上述(1)或(2)的结构的基础上,对于本发明的某一实施方式的半导体集成 电路而言,形成于上述多个布线层中的特定的布线层的密封圈或者中继区域与形成于其他 布线层的密封圈或者中继区域相比较具有向上述芯片形成区域的一侧突出的突出区域。 (4)本发明的某一实施方式为一种耐压试验方法,其中,在上述(1)的半导体集成 电路中,向上述电压施加区域与上述电压施加用焊盘之间施加电压,之后,测定在上述电压 施加区域与上述电压施加用焊盘之间流动的漏电流。 (5)本发明的某一实施方式为一种耐压试验方法,其中,在上述(2)的半导体集成 电路中,向上述电压施加区域与上述电压施加用焊盘之间施加电压,之后,测定在上述电压 施加区域与上述电压施加用焊盘之间流动的漏电流,向上述电压施加区域与上述第二电压 施加用焊盘之间施加电压,之后,测定在上述电压施加区域与上述第二电压施加用焊盘之 间流动的漏电流。 发明效果 由于密封圈以包围半导体集成电路的外侧的方式被较大范围地设置,因此通过以 在密封圈的各布线层间产生电位差的方式施加电压,从而能够进行考虑到半导体集成电路 内的层间膜厚的偏差的层间耐压试验。因此,能够实现具备适于层间绝缘膜的耐压检查的 构造的半导体集成电路。 附图说明 图1的(a)是本发明的第一实施方式所涉及的半导体集成电路的俯视图,(b)是上 4 CN 111599794 A 说 明 书 3/9 页 述半导体集成电路的A-A截面的剖视图,(c)是上述半导体集成电路的B-B截面的剖视图, (d)是上述半导体集成电路的E及F侧面的侧视图。 图2是表示上述半导体集成电路所具备的密封圈的构造的俯视图。 图3的(a)是本发明的第二实施方式所涉及的半导体集成电路的俯视图,(b)是上 述半导体集成电路的A-A截面的剖视图,(c)是上述半导体集成电路的B-B截面的剖视图, (d)是上述半导体集成电路的C-C截面的剖视图,(e)是上述半导体集成电路的E及F侧面的 侧视图。 图4是表示上述半导体集成电路所具备的密封圈的构造的俯视图。 图5是在特定的布线层具有防水功能的情况下的上述半导体集成电路的侧视图。