技术摘要:

本发明提供了一种半导体器件的制造方法,具体包括:提供衬底,上述衬底上形成有对应于密集区晶体管的第一栅极结构和对应于空旷区晶体管的第二栅极结构,上述第一栅极结构高于上述第二栅极结构;在上述第二栅极结构的上方形成缓冲层,上述缓冲层的上表面与上述第一栅极 全部

背景技术:

自从早年德州仪器的Jack Kilby博士发明了集成电路之时起,科学家和工程师已 经在半导体器件和工艺方面作出了众多发明和改进。近50年来半导体尺寸已经有了明显的 降低,这导致了不断增长的处理速度和不断降低的功耗。迄今为止,半导体的发展大致遵循 着摩尔定律,摩尔定律大意是指密集集成电路中晶体管的数量约每两年翻倍。现在,半导体 工艺正在朝着20nm以下发展,其中一些公司正在着手14nm工艺。这里只是提供一个参考,硅 原子约为0.2nm,这意味着通过20nm工艺制造出的两个独立组件之间的距离仅仅约为一百 个硅原子。半导体器件制造因此变得越来越具有挑战性,并且朝着物理上可能的极限推进。 随着集成电路的发展,器件尺寸越来越小,集成度越来越高。现行先进逻辑芯片工 艺中,存在各种密集度不同的组件设计,有可能引发工艺制造上芯片中各器件间的严重负 载效应(loading effect)。由于严重负载效应,存密集区器件和空旷区器件存在各种差异, 这会导致在一些需要对存密集区器件和空旷区器件进行同步操作的工艺中,对存密集区器 件或空旷区器件造成不同程度的负面影响,从而导致产品良率的下降。 有鉴于此,亟需要一种半导体器件的制造方法,能够有效地缓解由于芯片上器件 分布不均匀导致的严重负载效应,避免因为芯片上各个区域密集程度不同而导致器件性能 的下降,从而能够有效地提高半导体器件的性能和产品良率。

技术实现要素:

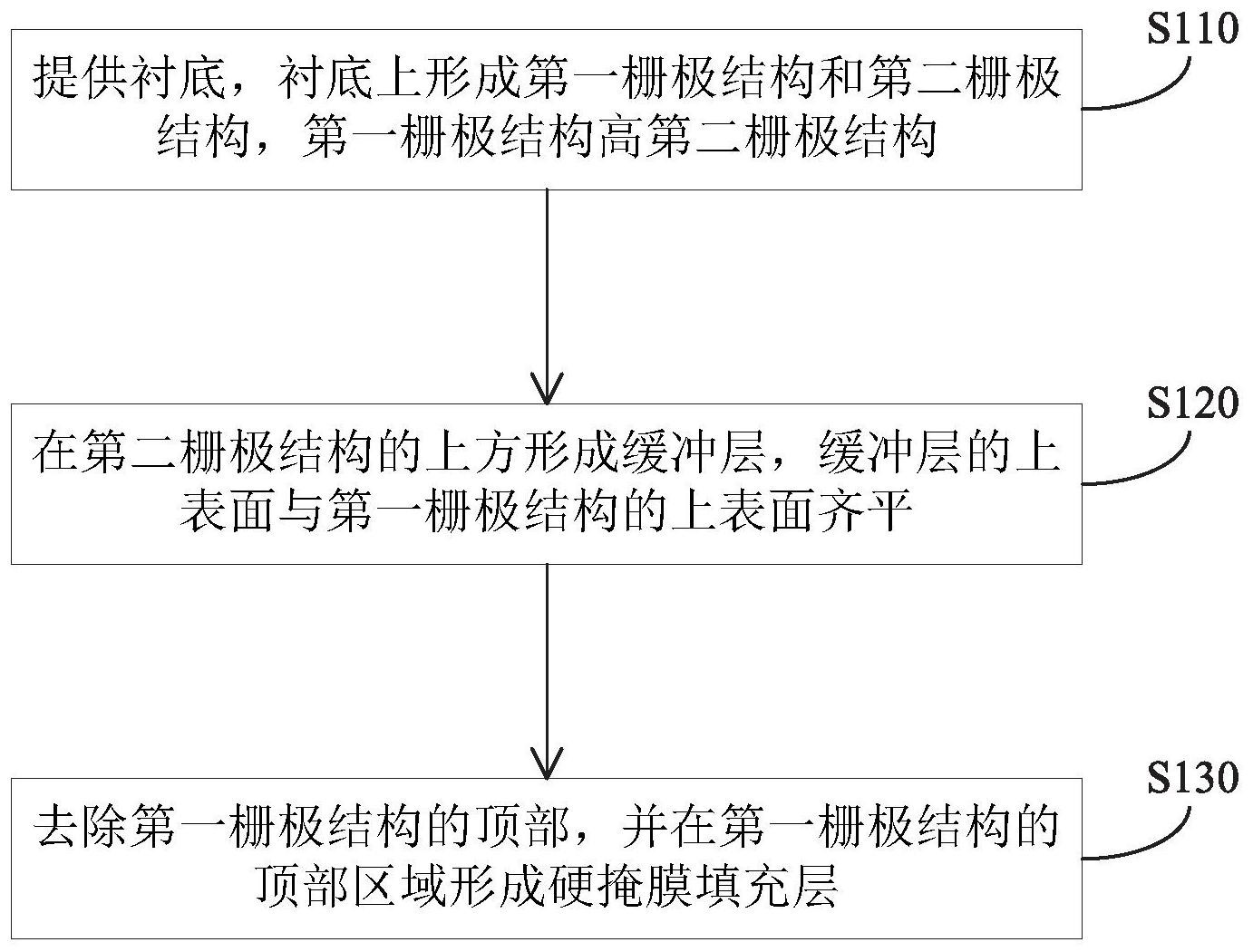

以下给出一个或多个方面的简要概述以提供对这些方面的基本理解。此概述不是 所有构想到的方面的详尽综览,并且既非旨在指认出所有方面的关键性或决定性要素亦非 试图界定任何或所有方面的范围。其唯一的目的是要以简化形式给出一个或多个方面的一 些概念以为稍后给出的更加详细的描述之序。 为了解决上述问题,本发明提供了一种半导体器件的制造方法,具体包括: 提供衬底,上述衬底上形成有对应于密集区晶体管的第一栅极结构和对应于空旷 区晶体管的第二栅极结构,上述第一栅极结构高于上述第二栅极结构; 在上述第二栅极结构的上方形成缓冲层,上述缓冲层的上表面与上述第一栅极结 构的上表面齐平;以及 去除上述第一栅极结构的顶部,并在上述第一栅极结构的顶部区域形成硬掩膜填 充层。 在上述的实施例中,通过在第二栅极结构的上方形成缓冲层,使得第二栅极结构 在后续的制造过程中与第一栅极结构具有相同的高度,能够有效地严重负载效应。并且,所 形成的缓冲层还能够在后续去除第一栅极结构顶部的过程中作为第二栅极结构的保护层, 4 CN 111599756 A 说 明 书 2/10 页 从而能够保护第二栅极结构的顶部不会被误去除。 在上述制造方法的一实施例中,可选的,形成上述缓冲层进一步包括: 在上述第一栅极结构和上述第二栅极结构的上方沉积覆盖上述第一栅极结构和 上述第二栅极结构的缓冲介质层;以及 以上述第一栅极结构的上表面为停止层平坦化上述缓冲介质层,以重新暴露上述 第一栅极结构的上表面,并保留上述第二栅极结构的上方的缓冲介质层为上述缓冲层。 在上述的实施例中,通过在第一栅极结构和第二栅极结构的上方形成覆盖第一栅 极结构和上述第二栅极结构的缓冲介质层,也就是说,形成在第二栅极结构上方的缓冲介 质层的高度高于第一栅极结构的上表面后,能够以第一栅极结构的上表面作为刻蚀停止层 来对缓冲介质层进行平坦化,从而能够使得第二栅极结构上方的缓冲层的上表面与第一栅 极结构的上表面齐平。 在上述制造方法的一实施例中,可选的,上述第一栅极结构的两侧形成有第一层 间介质层,上述第一层间介质层的上表面与上述第一栅极结构的上表面齐平; 上述第二栅极结构的两侧形成有第二层间介质层,上述第二层间介质层的上表面 与上述第二栅极结构的上表面齐平;以及 所沉积的缓冲介质层还覆盖上述第一层间介质层和上述第二层间介质层。 在上述制造方法的一实施例中,可选的,上述缓冲介质层、上述第一层间介质层和 上述第二层间介质层均为氧化物。 在上述制造方法的一实施例中,可选的,利用高密度等离子体工艺、高深宽比工艺 或等离子体增强工艺沉积上述缓冲介质层。 在上述制造方法的一实施例中,可选的,上述第一栅极结构进一步包括密集区晶 体管栅极以及由内向外依次位于上述密集区晶体管栅极两侧的第一侧墙和第二侧墙; 去除上述第一栅极结构的顶部进一步包括: 去除上述密集区晶体管栅极及其两侧的第一侧墙的顶部; 在上述第一栅极结构的顶部区域形成硬掩膜填充层进一步包括: 在上述密集区晶体管栅极及其两侧的第一侧墙的顶部区域形成硬掩膜填充层。 在上述制造方法的一实施例中,可选的,在上述密集区晶体管栅极及其两侧的第 一侧墙的顶部区域形成硬掩膜填充层进一步包括: 在去除上述密集区晶体管栅极及其两侧的第一侧墙的顶部后被上述第二侧墙包 围的凹槽中沉积凸起于上述凹槽的硬掩膜介质层;以及 平坦化上述硬掩膜介质层,以去除凸起于上述凹槽的硬掩膜介质层,并保留上述 凹槽内的硬掩膜介质层为上述硬掩膜填充层。 在上述制造方法的一实施例中,可选的,沉积上述硬掩膜介质层还包括: 在上述缓冲层的上表面同步地沉积硬掩膜介质层;以及 以上述缓冲层的上表面为停止层同步地平坦化上述缓冲层上方的硬掩膜介质层, 以去除上述缓冲层上方的硬掩膜介质层。 在上述制造方法的一实施例中,可选的,上述硬掩膜介质层为氮化物。 在上述制造方法的一实施例中,可选的,上述密集区晶体管栅极为金属栅极;和/ 或 5 CN 111599756 A 说 明 书 3/10 页 上述第二栅极结构中的空旷区晶体管栅极为金属栅极。 在上述制造方法的一实施例中,可选的,上述第一栅极结构的栅极宽度小于0.24 微米,上述第二栅极结构的栅极宽度大于0.24微米。 根据本发明所提供的半导体器件的制造方法,通过在图形空旷区域的器件上表面 形成缓冲层的方式,能够有效地缓解由于芯片上器件分布不均匀导致的严重负载效应。同 时,所形成的缓冲层还能够在后续作为图形空旷区域器件的保护层,能够改善空旷区晶体 管的栅极结构上表面在经历自对准氮化硅工艺后的氮化硅残留问题,从而能够有效地改善 器件的性能,提高产品良率。 附图说明 在结合以下附图阅读本公开的实施例的详细描述之后,能够更好地理解本发明的 上述特征和优点。在附图中,各组件不一定是按比例绘制,并且具有类似的相关特性或特征 的组件可能具有相同或相近的附图标记。 图1示出了本发明的一方面所提供的制造方法的流程图。 图2-图5示出了现有技术中自对准氮化硅工艺过程中的器件结构示意图。 图6-图11示出了本发明所提供的制造方法对应自对准氮化硅工艺过程中的器件 结构示意图。 附图标记 100 衬底 200 鳍型结构 300 层间介质层 320 缓冲介质层 322 缓冲层 400 第一栅极结构 420 密集区晶体管栅极 422 栅极层 440 第一侧墙 460 第二侧墙 500 第二栅极结构 520 空旷区晶体管栅极 522 栅极层 540 第一侧墙 560 第二侧墙 600 硬掩膜填充层 620 硬掩膜介质层