技术摘要:

本公开的实施例公开了一种阵列基板及其制备方法、显示装置,涉及显示技术领域,通过保护图案阻挡氢原子由间隔区域侵入有源层,避免有源层出现负偏压温度光照阈值电压漂移恶化及导体化的现象,优化了薄膜晶体管的特性。阵列基板包括衬底、栅极、有源层、源极、漏极、第 全部

背景技术:

在液晶显示领域中,薄膜晶体管(Thin Film Transistor,简称TFT)的有源层可使 用稳定性能、加工性能优异的硅系材料,例如非晶硅(a-Si)材料。 目前,随着液晶显示领域的发展,以金属氧化物(例如,铟镓锌氧化物(Indium Gallium Zinc Oxide,简称IGZO))作为薄膜晶体管的有源层,逐渐受到人们的关注。金属氧 化物薄膜晶体管相较于非晶硅薄膜晶体管具有较高的迁移率,但金属氧化物的稳定性较 差,易受氢或氧原子的影响,导致薄膜晶体管的阈值电压发生漂移。

技术实现要素:

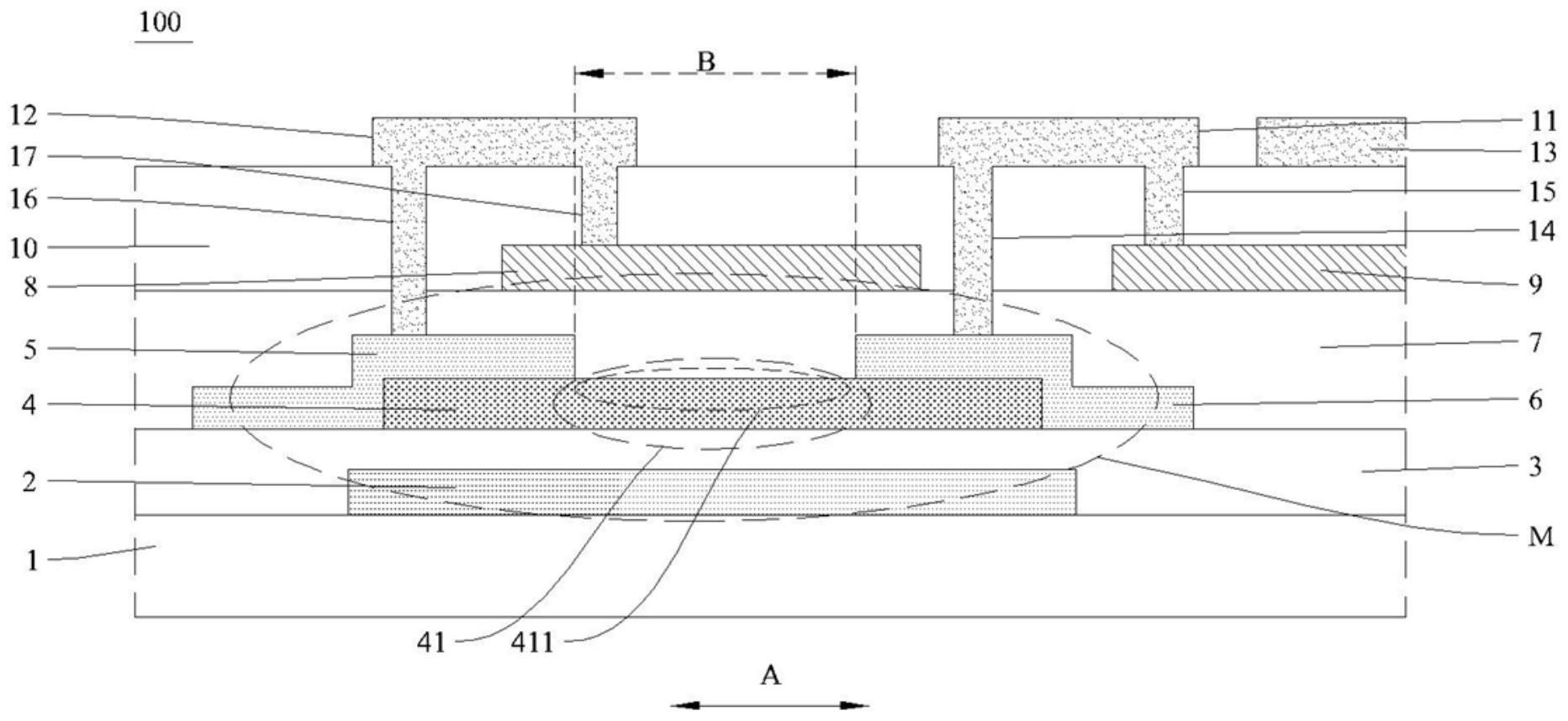

本公开一些实施例的目的在于提供一种阵列基板及其制备方法、显示装置,以在 不增加构图工艺次数的前提下,实现在源极与漏极之间的间隔区域的上方设置保护图案, 利用保护图案阻挡氢原子由间隔区域侵入有源层,优化薄膜晶体管的特性。 为达到上述目的,本公开一些实施例提供了如下技术方案: 第一方面,提供了一种阵列基板。所述阵列基板包括:衬底,依次设置于所述衬底 一侧的栅极和有源层,设置于所述有源层远离所述衬底一侧的源极和漏极,覆盖所述源极、 所述漏极和所述有源层的第一钝化层,以及设置于所述第一钝化层远离所述衬底一侧的保 护图案和像素电极。其中,沿平行于所述衬底的方向,所述源极与所述漏极间隔设置,二者 之间具有间隔区域。所述源极和所述漏极分别与所述有源层耦接。所述保护图案和所述像 素电极材料相同且同层设置。所述像素电极与所述源极或所述漏极耦接。所述保护图案在 所述衬底上的正投影,覆盖所述间隔区域在所述衬底上的正投影。所述保护图案被配置为, 阻挡氢原子由所述间隔区域侵入所述有源层。 本公开实施例所提供的阵列基板中,通过在第一钝化层远离衬底的一侧设置保护 图案,并且使保护图案在衬底上的正投影,覆盖薄膜晶体管的源极和漏极之间的间隔区域 在衬底上的正投影,即在前述间隔区域的上方设置保护图案,保护图案可以阻挡在保护图 案之后形成膜层的过程中氢原子由间隔区域侵入有源层,从而避免了由此引起的有源层出 现负偏压温度光照阈值电压漂移恶化及导体化的现象,优化了薄膜晶体管的特性。 并且,由于保护图案和像素电极材料相同且同层设置,因此保护图案的制作步骤 可兼容于像素电极的制作步骤中,无需额外增加用于制作保护图案的步骤,即不会增加阵 列基板的构图次数。 在一些实施例中,所述阵列基板还包括:覆盖所述保护图案和所述像素电极的第 二钝化层,以及设置于所述第二钝化层远离所述衬底一侧的第一连接电极。其中,所述第一 钝化层和所述第二钝化层中设置有贯通二者的第一过孔,所述第一过孔用于暴露所述源极 或所述漏极的至少一部分。所述第二钝化层中设置有第二过孔,所述第二过孔用于暴露所 4 CN 111725242 A 说 明 书 2/10 页 述像素电极的至少一部分。所述第一连接电极通过所述第一过孔与所述源极或所述漏极耦 接,且所述第一连接电极通过所述第二过孔与所述像素电极耦接。 在一些实施例中,所述阵列基板还包括:设置于所述第二钝化层远离所述衬底一 侧的公共电极。所述公共电极与所述第一连接电极材料相同且同层设置。 在一些实施例中,所述阵列基板还包括:设置于所述第二钝化层远离所述衬底一 侧的第二连接电极。所述第二连接电极被配置为,与提供电压信号的电路或电极耦接,以向 所述保护图案传输所述电压信号。 在一些实施例中,所述第一钝化层和所述第二钝化层中设置有贯通二者的第三过 孔,所述第三过孔用于暴露所述源极或所述漏极的至少一部分。所述第二钝化层中设置有 第四过孔,所述第四过孔用于暴露所述保护图案的至少一部分。所述第二连接电极通过所 述第三过孔与所述源极或所述漏极耦接,且所述第二连接电极通过所述第四过孔与所述保 护图案耦接。 在一些实施例中,所述第一钝化层的材料包括氧化硅。所述第二钝化层的材料包 括氮化硅。 在一些实施例中,所述有源层的材料包括氧化铟镓锌;所述保护图案的材料包括 金属氧化物导电材料。 第二方面,提供了一种显示装置,包括如上所述的阵列基板。 本公开实施例所提供的显示装置所能实现的有益效果,与如上所述的阵列基板所 能达到的有益效果相同,在此不做赘述。 第三方面,提供了一种阵列基板的制备方法,包括:提供衬底,在所述衬底的一侧 依次形成栅极和有源层。在所述有源层远离所述衬底的一侧形成源极和漏极;沿平行于所 述衬底的方向,所述源极与所述漏极间隔设置,二者之间具有间隔区域;所述源极和所述漏 极分别与所述有源层耦接。在所述源极、所述漏极和所述有源层远离所述衬底的一侧形成 第一钝化层。采用一次构图工艺,在所述第一钝化层远离所述衬底的一侧形成保护图案和 像素电极;所述像素电极与所述源极或所述漏极耦接;所述保护图案在所述衬底上的正投 影覆盖所述间隔区域在所述衬底上的正投影,所述保护图案被配置为阻挡氢原子由所述间 隔区域侵入所述有源层。 本公开实施例所提供的阵列基板的制备方法所能实现的有益效果,与如上所述的 阵列基板所能达到的有益效果相同,在此不做赘述。 在一些实施例中,所述采用一次构图工艺,在所述第一钝化层远离所述衬底的一 侧形成保护图案和像素电极,包括:采用溅射工艺,在所述第一钝化层远离所述衬底的一侧 形成导电薄膜,溅射过程中通入氧气。采用一次构图工艺,对所述导电薄膜进行图案化,形 成保护图案和像素电极。 附图说明 为了更清楚地说明本公开中的技术方案,下面将对本公开一些实施例中所需要使 用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例的附 图,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。此外,以下描述 中的附图可以视作示意图,并非对本公开实施例所涉及的产品的实际尺寸、方法的实际流 5 CN 111725242 A 说 明 书 3/10 页 程、信号的实际时序等的限制。 图1为本公开一些实施例提供的一种阵列基板的像素架构图; 图2为本公开一些实施例提供的一种阵列基板的俯视图; 图3为图2中P-P'处的局部剖面图; 图4为本公开一些实施例提供的另一种阵列基板的俯视图; 图5为图4中Q-Q'处的局部剖面图; 图6为本公开一些实施例提供的一种显示装置的局部剖面图; 图7为本公开一些实施例提供的阵列基板的一种制备方法的流程图; 图8为本公开一些实施例提供的制备方法中制备栅极和有源层的步骤图; 图9为本公开一些实施例提供的制备方法中制备源极和漏极的步骤图; 图10为本公开一些实施例提供的制备方法中制备第一钝化层的步骤图; 图11~图12为本公开一些实施例提供的制备方法中制备保护图案和像素电极的 步骤图; 图13为本公开一些实施例提供的制备方法中制备第二钝化层的步骤图; 图14为本公开一些实施例提供的制备方法中制备各个过孔的步骤图; 图15~图16为本公开一些实施例提供的制备方法中制备第一连接电极、第二连接 电极和公共电极的步骤图。