技术摘要:

本发明公开了一种存储器装置及其操作方法,该存储器装置,包括复合记忆单元的阵列。此些复合记忆单元的至少一个包含第一类型的第一存储单元、第二类型的第二存储单元、第一单元间数据路径连接第一存储单元至第二存储单元、及第一数据路径控制开关。第一数据路径控制开 全部

背景技术:

神经网络是受生物神经系统处理信息的方式所启发的信息处理示例。随着大型训 练数据集和复杂学习演算法的可用性,神经网络促进了例如计算机视觉、语音识别、和自然 语言处理等众多领域的重大进步。 神经网络中的基本计算单元是神经元。神经元接收来自其他神经元或来自外部来 源的输入并计算输出。图1绘示示例性神经网络100。神经网络100包含按层排列的多个神经 元。神经网络100包括输入神经元的输入层102(也即,提供输入数据的神经元)、隐藏神经元 的三个隐藏层106、108、及110(也即,执行计算并将信息从输入神经元传输到输出神经元、 及输出神经元的输出层104(也即,提供输出数据的神经元)。相邻层中的神经元具有连接在 它们之间的突触层。例如,突触层112连接输入层102和隐藏层106中的神经元,突触层114连 接隐藏层106和108中的神经元,突触层116连接隐藏层108和110中的神经元,而突触层118 连接隐藏层110和输出层104中的神经元。所有这些连接具有与它们相关联的权重。例如,隐 藏层106中的神经元122、124和126分别通过与权重w1132、w2134、和w3136的连接而连接到 隐藏层108中的神经元128。隐藏层108中的神经元128的输出可以根据来自隐藏层106中的 神经元122、124和126的输入(x1、x2和x3)以及连接中的权重w1、132、w2134、和w3136而被计 算为函数。此函数可表达如下: 在上面的乘积和(sum-of-product)表达式中,每个乘积项是可变输入xi和权重wi 的乘积。权重wi可以在此些项之间变化,例如对应于可变输入xi的系数。相仿地,也可以计 算隐藏层中其他神经元的输出。隐藏层110中的两个神经元的输出用作输出层104中的输出 神经元的输入。 神经网络可用于学习最能代表大量数据的图案。靠近输入层的隐藏层学习高级通 用模式,而靠近输出层的隐藏层学习更多数据特定图案。训练是神经网络从训练数据中学 习的阶段。在训练期间,基于训练期的结果为突触层中的连接分配权重。推断(inference) 是使用训练过的神经网络来推断/预测输入数据并基于预测产生输出数据的阶段。 卷积神经网络是一种神经网络,其在输入层之后包括一个或多个卷积隐藏层,然 后接续一个或多个完全连接的隐藏层。卷积神经网络最常用于分析2D数据,例如图像内的 物件识别。在卷积隐藏层中,可以通过在整个图像中滑动权重矩阵并重复相同的点积运算 来计算输入图像的区域和权重矩阵之间的点积。卷积隐藏层用于检测输入图像的高级特征 (high-level feature)。最后一个卷积隐藏层的输出是第一个完全连接的隐藏层的输入。 完全连接的隐藏层中的每个神经元系连接到相邻完全连接的隐藏层中的每个神经元。完全 5 CN 111581141 A 说 明 书 2/11 页 连接的隐藏层的目的是使用在卷积隐藏层中检测到的特征的非线性组合来对输入图像中 的物件进行分类。 存储器内计算(in-memory computing)是一种将存储器内计算装置中的存储单元 用于数据处理和存储器储存的方法。神经网络或卷积神经网络可被实现在存储器内计算装 置中。乘积和函数的权重可以储存在存储器内计算装置的存储单元中。乘积和函数可以实 现为存储器内计算装置中的电路运作,其中阵列的存储单元的电特性实现此函数。 在具有易失性存储单元(例如,SRAM)的存储器内计算装置中,执行乘积和运算所 花费的时间可能是短的,且运作可具有高推断准确性。然而,将权重从储存乘积和所需的权 重的其他存储单元加载于易失性存储单元之中可能要花费很长的时间。再者,以易失性存 储单元执行乘积和运算可能导致高功耗。 在具有非易失性存储单元的存储器内计算装置中,存储单元中的装置可变性、不 准确性的读取和写入运作、及其他非理想装置特性,可导致非易失性存储器中所储存的权 重的波动。储存权重的波动,特别是在使用可重新编程的非易失性存储器装置(例如浮动栅 存储器、相变化存储器、电阻性存储器等)的存储器内计算装置中的波动,这样的特性将会 导致存储器内计算装置的神经网络输出更不精准的结果。 因此,有需要提供一种具有更高推断准确性的存储器内计算装置,其可以执行快 速且低功率的乘积和运算。

技术实现要素:

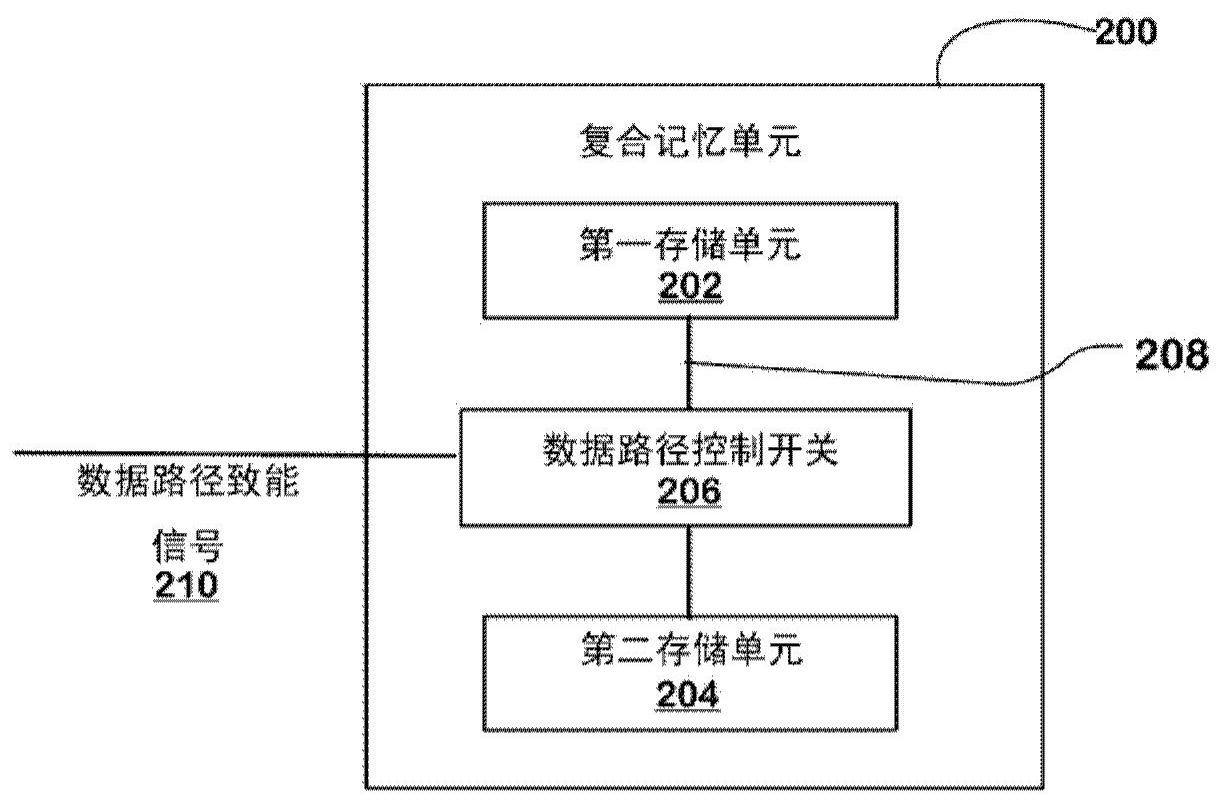

本文描述了一种集成电路,其包括实现神经网络的存储器内计算装置。在一些实 施例中,存储器内计算装置可以实现卷积神经网络。存储器内计算装置具有复合记忆单元 的阵列。每个复合记忆单元包括第一类型的第一存储单元、第二类型的第二存储单元、将第 一存储单元连接到第二存储单元的第一单元内数据路径、及第一数据路径控制开关。第一 单元内数据路径将第一存储单元的载流端连接到第二存储单元的载流端。第一数据路径控 制开关回应于数据传输致能信号,从而致能第一存储单元及第二存储单元之间通过第一单 元间数据路径(intra-unit data path)的数据传输。 第一类型的存储单元可以是易失性存储单元(例如,SRAM),而第二类型的存储单 元可以是非易失性存储单元(例如,浮动栅存储器、相变化存储器、电阻性存储器、磁阻存储 器、铁电存储器等)。复合记忆单元阵列中的第一存储单元被配置用于快速且更准确的乘积 和运算。复合记忆单元阵列中的第二存储单元被配置为储存神经网络的突触层的权重。复 合记忆单元阵列中的第二存储单元还可以被配置为储存乘积和运算的结果。 阵列中复合记忆单元的成列(row)的第一存储单元和第二存储单元分别耦接到一 组第一字线和一组第二字线。阵列中复合记忆单元的成行(column)的第一存储单元和第二 存储单元分别耦接到一组第一位线和一组第二位线。复合记忆单元的成行中的第二存储单 元耦接到一组第一来源线。复合记忆单元阵列还可包括信号控制电路电性耦接到此组第一 字线、此组第二字线、此组第一位线、此组第二位线和此组第一来源线。信号控制电路还可 以将数据传输致能信号致能并传送到复合记忆单元阵列中的第一数据路径控制开关。 在存储器内计算装置的一些实施例中,每个复合记忆单元还可包括第二类型的第 三存储单元。第二单元内数据路径可以将第一存储单元连接到第三存储单元。回应于数据 6 CN 111581141 A 说 明 书 3/11 页 传输致能信号,第二数据路径控制开关致能第一存储单元和第三存储单元之间通过第二单 元内数据路径的数据传输。 还描述了在复合记忆单元中存储单元之间传输数据的方法、使用复合记忆单元执 行乘积和运算的方法、及实现所述方法的控制电路。 通过阅读随附附图、详细说明和权利要求,可以看出本公开的其他方面和优点。 为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附图 式详细说明如下。 附图说明 将参照图1-13提供本技术实施例的详细说明。 图1绘示示例神经网络的示意图。 图2绘示具有第一存储单元及第二存储单元的复合记忆单元的第一示例示意图。 图3绘示具有第一存储单元、第二存储单元、及第三存储单元的复合记忆单元的第 二示例示意图。 图4绘示具有SRAM的第一存储单元及1T-1R电阻性存储器的第二存储单元的复合 记忆单元的示意图。 图5绘示在复合记忆单元中以第一存储单元执行乘积和的示例方法的示意图。 图6绘示在复合记忆单元中以第二存储单元执行乘积和的示例方法的示意图。 图7绘示在复合记忆单元中将数据从第二存储单元传输至第一存储单元的示例方 法的示意图。 图8绘示在复合记忆单元中将数据从第一存储单元传输至第二存储单元的示例方 法的示意图。 图9绘示具有SRAM的第一存储单元及1T-1R电阻性存储器的第二及第三存储单元 的复合记忆单元的示意图。 图10绘示在复合记忆单元中在第一存储单元及第三存储单元之间传输数据的示 例方法的示意图。 图11绘示具有SRAM的第一存储单元及1T-1R电阻性存储器的第二存储单元的复合 记忆单元的示意图。 图12绘示具有SRAM的第一存储单元及1T-1R电阻性存储器的第二及第三存储单元 的复合记忆单元的示意图。 图13绘示具有复合记忆单元的阵列的示例性存储器内计算存储器装置的简易芯 片方块图。 【附图标记说明】 100:神经网络 112、114、116、118:突触层 122、124、126、128:神经元 132、134、136:权重 102:输入层 106、108、110:隐藏层 7 CN 111581141 A 说 明 书 4/11 页 104:输出层 200、300、400、900、1102、1104、1106、1108、1202、1204、1206、1208:复合记忆单元 202、302、402、902:第一存储单元 204、304、404、904:第二存储单元 206、308、310、406、950、952:数据路径控制开关 208、312、316、418、916、918:单元内数据路径 210:数据路径致能信号 306、906:第三存储单元 314、318:数据传输致能信号 407、907:反相器 409、411、909、911:通道栅晶体管 410、910:第一字线 412、912:第一位线 414、914:第一位元补偿线 422、920、922:导电路径 428、910、928:第二字线 430、930:第二位线 434、934:第一来源线 440、940、1125、1225:列译码器和驱动器电路 442、944、1152、1162、1272、1282:行译码器和驱动器电路 500、600、700、800、1000:示例方法 510~530、610~630、710~730、810~830、1010~1020:流程步骤 926:第三位线 936:第二来源线 1100、1200、1302:阵列 1110、1112、1114、1116、1214、1216:共同字线 1130、1132:共同导电路径 1118、1120、1218、1220:共同第一位线 1126、1128、1226、1228、1258、1260:共同第一来源线 1140、1142:共同第一补偿位线 1122、1124、1222、1224:共同第二位线 1210、1212:共同第一字线 1230、1231、1232、1233:共同导电路径 1254、1256:共同第三位线 1250、1252:共同第一位元补偿线 1300:存储器内计算装置 1304:控制器 1305:数据总线 1312:偏压安排状态机 8 CN 111581141 A 说 明 书 5/11 页 1390:缓冲器电路 1393:输入/输出电路