技术摘要:

一种用于闪存的抹除方法,所述闪存具有记忆块,每一记忆块是切分成多个内存扇区,所述抹除方法的步骤将叙述如下。抹除与验证流程根据内存扇区使能信号来被依序执行于所述记忆块上或记忆块的内存扇区。过抹除校正与验证流程根据所述内存扇区使能信号来被依序执行于所述 全部

背景技术:

闪存包括各别的金属氧化半导体(Metal-Oxide-Semiconductor,MOS)场效晶体管 记忆胞,其中每一个记忆胞包括源极,漏极,漂浮闸以及控制闸。为了作为记忆块抹除全部 的晶体管记忆胞,为了读取晶体管记忆胞,为了验证晶体管记忆胞是经过抹除的(over- erased),或是为了验证晶体管记忆胞没有被过抹除等目的,各种不同的电压会被施加在控 制闸上来将晶体管记忆胞编程为二进制的1或是0。 来自过抹除晶体管记忆胞的漏电流这种不想要的效果将叙述如下。在一般闪存 中,大量的晶体管记忆胞,例如512个晶体管记忆胞的漏极连接到每一条位线。如果大量的 晶体管记忆胞在位在线汲取背景漏电流,所述位在线的总漏电流可能会超过记忆胞的读取 电流。这会使得所述位在线的任何晶体管记忆胞都无法被读取,因此造成所述闪存无法运 作。 为了克服上述的问题,过抹除校正与验证流程与后过抹除校正与验证流程执行于 晶体管记忆胞上,使得经过过抹除的晶体管记忆胞的位线的漏电流可以获得解决。然而,一 些经过抹除的晶体管记忆胞可能会在过抹除校正与验证流程以及后过抹除校正与验证流 程被执行后改变成欠抹除的(under-erased)晶体管记忆胞。 参考图1,图1为一种传统抹除方法的流程图。传统抹除方法是用来使欠抹除的晶 体管记忆胞在过抹除校正与验证流程以及后过抹除校正与验证流程被执行后经由执行步 骤S15来被抹除。传统抹除方法执行于闪存中其包括内存管理器件以及内存模块,其中所述 内存模块包括多个记忆块,且每一个记忆块包括多个晶体管记忆胞。 在图1中,在步骤S11,内存管理器件会验证并预编程内存模块的全部晶体管记忆 胞。接着,在步骤S12,内存管理器件会验证并抹除全部的晶体管记忆胞成为记忆块,也就是 说,抹除单元是一记忆块。这边要注意,在传统抹除方法中,有两次抹除与验证流程要被执 行,其中步骤S11是第一次抹除与验证流程,而步骤S15是第二次抹除与验证流程。 接着,为了避免经过过抹除的晶体管记忆胞有漏电流而造成闪存无法运作,在步 骤S13,当验证结果显示至少一过抹除晶体管记忆胞存在于记忆块上时,内存管理器件会验 证内存模块的全部晶体管记忆胞并且执行过抹除校正(over-erase correction)于内存模 块的经过过抹除的晶体管记忆胞上。接着,在步骤S14,内存管理器件对内存模块的晶体管 记忆胞执行后过抹除校正与验证流程。 然后,步骤S15会被执行,内存管理器件会验证并且抹除全部的晶体管记忆胞作为 记忆块,以在过抹除校正与验证流程与后过抹除校正与验证流程被执行后校正欠抹除的晶 体管记忆胞的阈值电压,并且使得欠抹除的晶体管记忆胞被抹除。这边要注意,如果步骤 S15的验证结果显示记忆块不应所述被抹除的(也就是记忆块没有经过抹除),传统抹除方 法终止;否则(也就是记忆块是经过抹除的),步骤S13至S15会再执行一次。 5 CN 111599399 A 说 明 书 2/7 页 虽然欠抹除的晶体管记忆胞的阈值电压可以在过抹除校正与验证流程与后过抹 除校正与验证流程被执行后被校正,传统抹除方法的执行循环(do-loop)可能会被需要,而 且在周期的前后可能需要步骤S15的抹除时间,因此使得传统抹除方法极度耗时。 为了减少传统抹除方法的运行时间,另一种传统抹除方法被提出来。参考图2,图2 为另一种传统抹除方法的流程图。图2的传统抹除方法被执行于上述的闪存中,特别是,一 种过抹除校正旗标是用来决定是否抹除与验证流程应所述再次被执行。 在步骤S21,内存管理器件会验证并且预编程内存模块的全部晶体管记忆胞。接 着,在步骤S22,抹除与验证流程与过抹除校正与验证流程被内存管理器件所执行,过抹除 校正旗标是用来决定是否要再次执行抹除与验证流程,使得欠抹除的晶体管记忆胞的阈值 电压可以在过抹除校正与验证流程被执行后被校正。接着,在步骤S23,内存管理器件对内 存模块的晶体管记忆胞执行后过抹除校正与验证流程,然后接着传统抹除方法终止。 步骤S22包括步骤S221至S224,步骤S221至S224的细节将详述如下。在步骤S221, 内存管理器件会验证并且抹除全部的晶体管记忆胞作为记忆块,特别来说,为了达到抹除 的目的,如果所述验证结果显示所述记忆块应所述被抹除,所述内存管理器件会使得至少 一抹除脉冲注入至所述记忆块的晶体管记忆胞。在步骤S221,如果所述记忆块是经过抹除 的,内存管理器件将抹除旗标(以下简称为ERS旗标)设为逻辑真值(也就是数值“1”)。接着, 在步骤S222,所述内存管理器件检查ERS旗目标数值。如果所述ERS旗标为逻辑真值,步骤 S223接着会被执行;否则(也就是ERS旗标为逻辑伪值或“0”),步骤S23接着会被执行。 在步骤S223,内存管理器件会验证内存模块的全部晶体管记忆胞并且当验证结果 显示至少一过抹除晶体管记忆胞存在于所述记忆块上时,通过执行至少一过抹除校正脉冲 (也就是注入过抹除校正脉冲至晶体管记忆胞)来执行过抹除校正于内存模块的经过过抹 除的晶体管记忆胞上。在步骤S223,如果过抹除校正被执行于所述记忆块上,内存管理器件 将过抹除校正旗标设为逻辑真值(也就是数值“1”)。接着,在步骤S224,内存管理器件检查 过抹除校正旗目标数值。如果过抹除校正旗标为逻辑真值,接着再次执行步骤S221;否则 (也就是过抹除校正旗标为逻辑伪值或“0”),接着执行步骤S23。 通过使用过抹除校正旗标,图2的传统抹除方法可以在周期前节省抹除时间(也就 是通过过抹除校正旗标来决定是否要执行步骤S221)。然而,抹除与验证流程(步骤S221)与 过抹除校正与验证流程(步骤S223)之间的执行循环仍然被需要,图2的传统抹除方法的运 行时间并无法有效地被缩减。

技术实现要素:

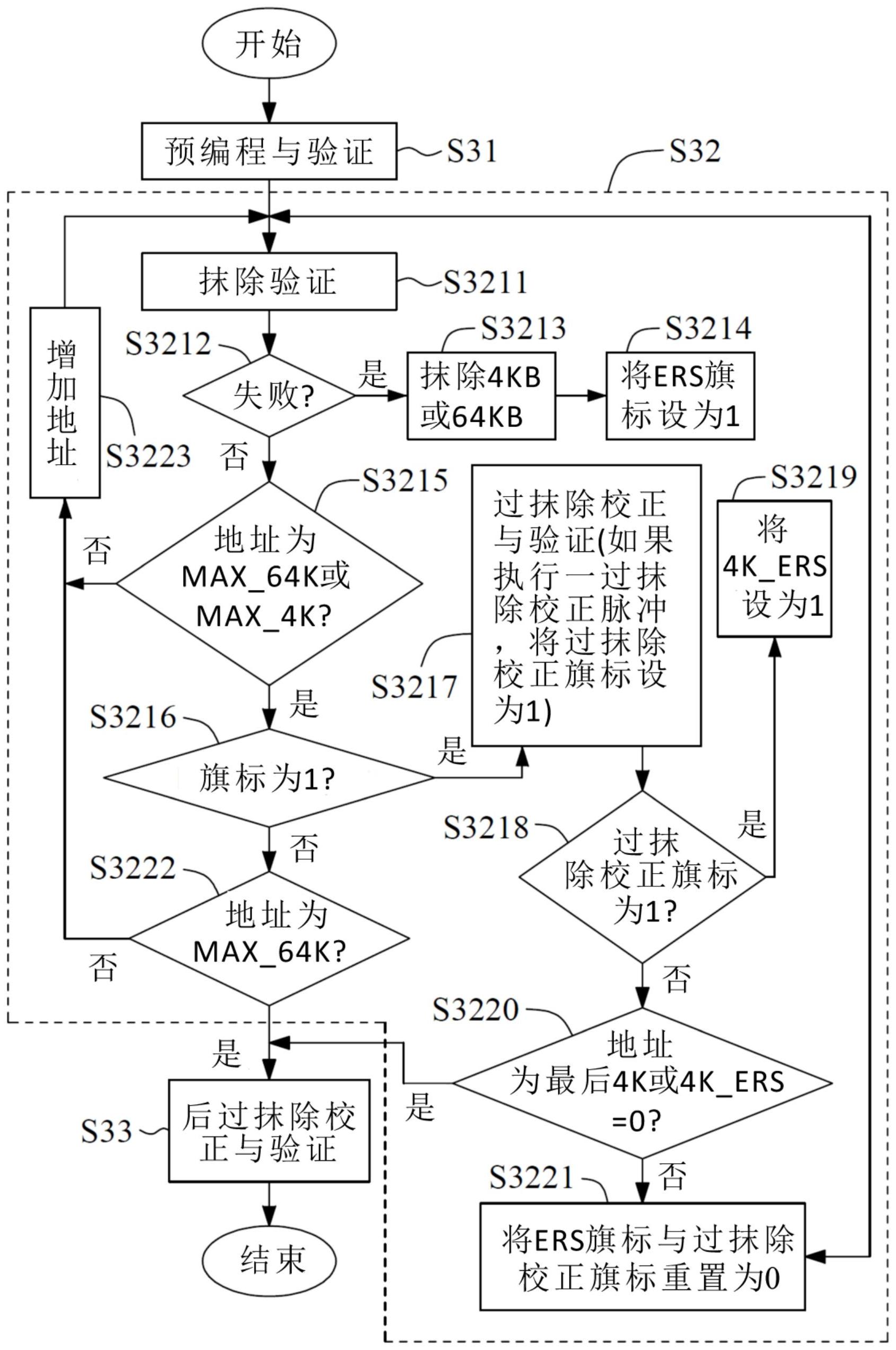

本申请的一个目的为提供一种用于闪存中的抹除方法,且所述抹除方法具有一种 自我检查的算法来于过抹除校正被执行后,防止欠抹除的晶体管记忆胞的存在。同时,在慢 与快晶体管记忆胞不会位于内存扇区的多条位线(例如16位)的同一条位在线的假设前提 下,所述抹除与验证流程与所述过抹除校正与验证流程之间的执行循环(do-loop)可以被 消除。 本申请的另一个目的在于提供一种闪存其可以执行上述抹除方法,且所述闪存具 有与所述抹除方法相似的优点。 为达到至少上述之目标,本申请提供用于闪存中的抹除方法,所述闪存包括切分 6 CN 111599399 A 说 明 书 3/7 页 成多个内存扇区的至少一记忆块。所述抹除方法包括步骤:执行抹除与验证流程于所述记 忆块上,并且如果所述记忆块是经过抹除的,将抹除旗标设为逻辑真值;执行过抹除校正与 验证流程于所述记忆块上,如果所述抹除旗标为逻辑真值,将过抹除校正旗标设为逻辑真 值且如果过抹除校正被执行于所述记忆块上,将内存扇区使能信号为设为有效,然后接着 将所述抹除旗标与所述过抹除校正旗标两者皆重置为逻辑伪值;当所述内存扇区使能信号 被设为有效时,依序执行所述抹除与验证流程于记忆块的内存扇区上,并且如果至少一所 述内存扇区是经过抹除的,将所述抹除旗标设为逻辑真值;以及当所述内存扇区使能信号 被设为有效且所述抹除旗标被设为逻辑真值时,依序执行所述过抹除校正与验证流程于记 忆块的内存扇区上,如果所述过抹除校正被执行于至少一所述内存扇区上,将所述过抹除 校正旗标设为逻辑真值,然后接着将所述抹除旗标与所述过抹除校正旗标两者皆重置为逻 辑伪值。 在本申请的一实施例中,所述至少一记忆块包括多个记忆块,且所述抹除与验证 流程是被依序执行于所述记忆块上,其中地址是用来指示所述记忆块或所述内存扇区,在 验证结果显示所述记忆块没有欠抹除的晶体管记忆胞,且如果至少一所述记忆块是经过抹 除的,将所述抹除旗标设为逻辑真值后,所述地址是增加记忆块偏置值(block offset)。 在本申请的一实施例中,如果所述抹除旗标为逻辑真值,所述过抹除校正与验证 流程是被依序执行于所述记忆块上,如果过抹除校正被执行于至少一所述记忆块上,将所 述过抹除校正旗标设为逻辑真值且将所述内存扇区使能信号设为有效,然后接着所述抹除 旗标与所述过抹除校正旗标两者皆被重置为逻辑伪值。 在本申请的一实施例中,所述抹除与验证流程执行于所述地址指示的记忆块的内 存扇区上,在验证结果显示所述记忆块的内存扇区没有欠抹除的晶体管记忆胞,且如果至 少一记忆块的内存扇区是经过抹除的,将所述抹除旗标设为逻辑真值后,所述地址增加扇 区偏置值。 在本申请的一实施例中,在所述抹除与验证流程于所述记忆块上被执行于所述记 忆块上之前,预编程与验证流程被执行于所述记忆块上。 在本申请的一实施例中,当所述记忆块或所述内存扇区没有欠抹除的晶体管记忆 胞且所述抹除旗标为逻辑伪值,或所述记忆块没有过抹除的晶体管记忆胞且所述内存扇区 使能信号没有被设为有效,或所述内存扇区没有过抹除的晶体管记忆胞且所述内存扇区使 能信号被设为有效时,后过抹除校正与验证流程被执行于所述记忆块上。 为达到至少上述目标,本申请提供一种用在闪存包括记忆块中的抹除方法,且每 一所述记忆块被切分成多个内存扇区。所述抹除方法包括步骤:根据内存扇区使能信号来 依序执行抹除与验证流程于所述记忆块上或记忆块的内存扇区,并如果至少一所述记忆块 或至少一所述内存扇区是经过抹除的,将抹除旗标设为逻辑真值;以及如果所述抹除旗标 为逻辑真值,根据所述内存扇区使能信号来依序执行过抹除校正与验证流程于所述记忆块 上或记忆块的内存扇区,如果过抹除校正被执行于至少一所述记忆块上或至少一记忆块的 内存扇区,将过抹除校正旗标设为逻辑真值并将所述内存扇区使能信号设为有效,然后接 着将所述抹除旗标与所述过抹除校正旗标两者皆重置为逻辑伪值。 在本申请的一实施例中,当所述内存扇区使能信号没有被设为有效时,所述抹除 与验证流程被依序执行于所述记忆块上,且所述过抹除校正与验证流程被依序执行于所述 7 CN 111599399 A 说 明 书 4/7 页 记忆块上;当所述内存扇区使能信号被设为有效时,所述抹除与验证流程被依序执行于所 述内存扇区上,且所述过抹除校正与验证流程被依序执行于所述内存扇区上。 为达到至少上述目标,本申请提供一种闪存包括内存模块以及内存管理器件电性 连接于所述内存模块,其中所述内存模块包括至少一记忆块切分成多个内存扇区。所述内 存管理器件是用来执行上述抹除方法。 总结来说,所述抹除方法所述闪存根据所述本申请实施例提供的抹除方法与闪存 可以在过抹除校正被执行后,检查所述内存扇区是否具有至少一欠抹除的晶体管记忆胞, 并且如果所述内存扇区具有至少一欠抹除的晶体管记忆胞,抹除所述内存扇区,以使得在 所述过抹除校正被执行后,自我检查的算法可以被执行来预防欠抹除晶体管记忆胞的发 生。此外,所述自我检查的算法会验证并且抹除所述内存。 附图说明 本申请的特征点将于附图中以特定参照标示使其突出,其中: 图1(现有技术)为一种传统抹除方法的流程图; 图2(现有技术)另一种传统抹除方法的流程图;以及 图3为本申请用于闪存中的抹除方法的一实施例的流程图。 【附图标记列表】 S11~S15 步骤 S21~S23 步骤 S221~S224 步骤 S31~S33 步骤 S3211~S3223 步骤