技术摘要:

本发明公开了一种制作非对称低中压器件的方法及非对称低中压器件,其中方法包括:在非对称低中压器件的衬底区形成N阱和P阱;在N阱上方的衬底区的上表面制作闸极,闸极与P阱无重合区域;从P阱上方的衬底区的上表面打开窗口,并大角度注入第一掺杂离子形成第一掺杂区;从 全部

背景技术:

6V~8V Asym-DEMOS(非对称低中压器件)在SWITCH(转换器)以及LDO(低压差线性 稳压器)领域有很大的应用需求。图1中示出的是一典型的Asym-DEMOS的剖面图,其沟道区 域由5V NMOS(N型金属氧化物半导体)的P阱11构成,衬底区的上表面的闸极13与P阱11的重 合的P阱区域为沟道,沟道的的长度为L,漂移区由5V PMOS(P型金属氧化物半导体)的N阱12 构成。 因为穿通电压与击穿电压都起着限制着晶体管最高工作电压的作用,P阱11与N阱 12的击穿电压为16V(伏)左右,Asym-DEMOS的VDD(操作电压)在10V以内,低于16V的击穿电 压,可保证Asym-DEMOS工作在正常电压范围内而不会击穿。 又因为受限于5V COMS穿通电压(punch-through)的要求,Asym-DEMOS器件的沟道 长度L最低范围为0.5-0.6um(微米),无法再根据器件做进一步缩小,这就限制了导通电阻 的进一步改善,导致电阻较大,从而导致Asym-DEMOS的性能不高。

技术实现要素:

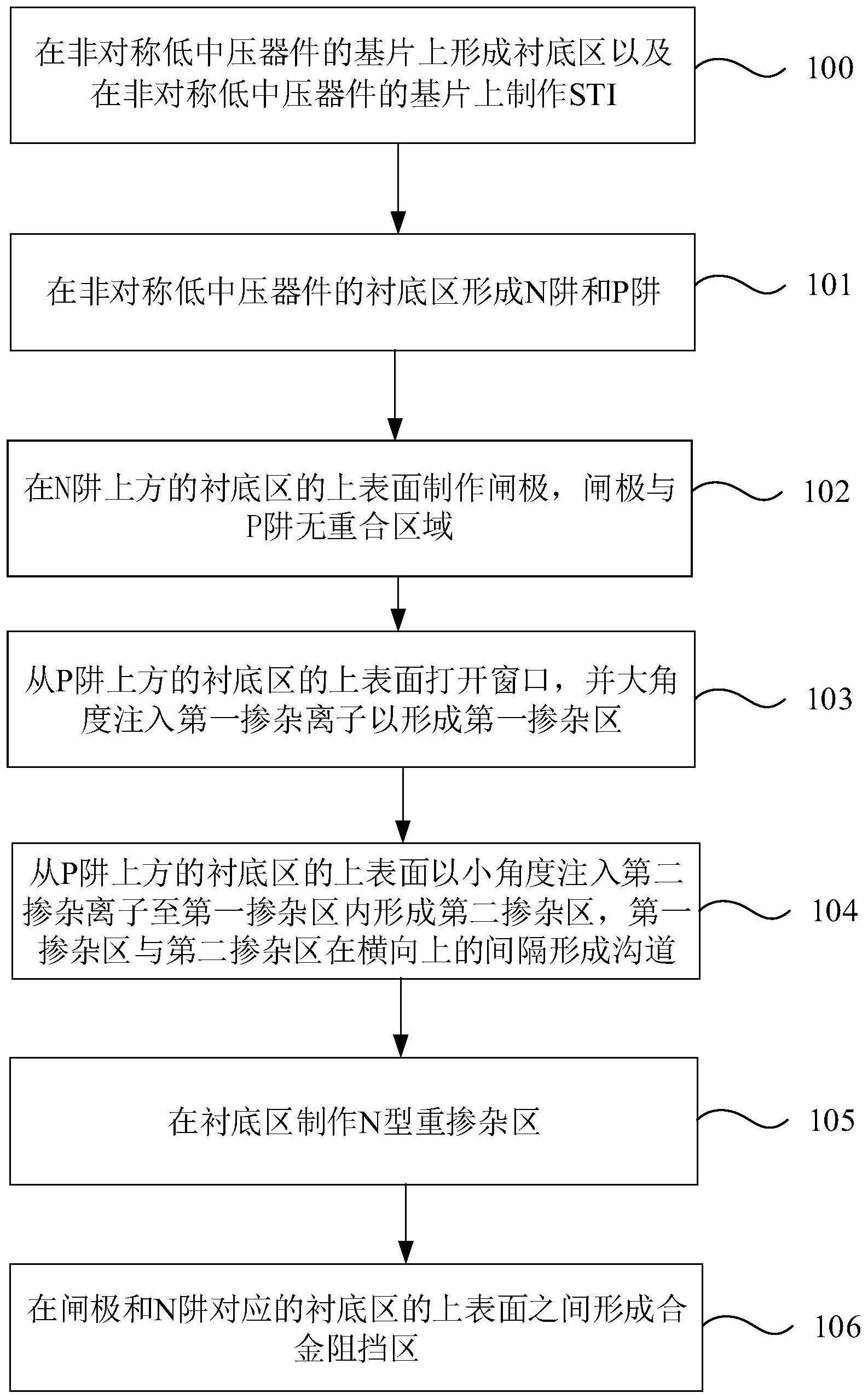

本发明要解决的技术问题是为了克服现有技术中Asym-DEMOS的导通电阻较大,导 致Asym-DEMOS的性能不高的缺陷,提供一种制作非对称低中压器件的方法及非对称低中压 器件。 本发明是通过下述技术方案来解决上述技术问题: 提供一种制作非对称低中压器件的方法,所述方法包括: 在非对称低中压器件的衬底区形成N阱和P阱; 在所述N阱上方的所述衬底区的上表面制作闸极,所述闸极与所述P阱无重合区 域; 从所述P阱上方的所述衬底区的上表面打开窗口,并大角度注入第一掺杂离子形 成第一掺杂区; 从所述P阱上方的所述衬底区的上表面以小角度注入第二掺杂离子至所述第一掺 杂区内形成第二掺杂区,所述第一掺杂区与所述第二掺杂区在横向上的间隔形成沟道。 较佳地,所述从所述P阱上方的所述衬底区的上表面以小角度注入第二掺杂离子 的步骤之后还包括: 在所述衬底区制作N型重掺杂区。 较佳地,在所述衬底区制作N型重掺杂区的步骤之后还包括: 在所述闸极和所述N阱对应的所述衬底区的上表面之间形成合金阻挡区。 较佳地,在所述非对称低中压器件的衬底区形成N阱和P阱步骤之前还包括: 3 CN 111613533 A 说 明 书 2/3 页 在所述非对称低中压器件的基片上形成衬底区以及在所述非对称低中压器件的 基片上制作STI。 较佳地,所述第一掺杂离子为硼离子,所述硼离子的掺杂浓度为1.8E12/立方厘米 ~2.2E12/立方厘米。 较佳地,在所述大角度注入第一掺杂离子以形成沟道的步骤中,所述大角度注入 的角度范围为27~33度。 较佳地,所述沟道的长度范围为0.05~0.3微米。 较佳地,所述第二掺杂离子为砷离子,所述砷离子的掺杂浓度为5.5E14/立方厘米 ~6.1E14/立方厘米。 较佳地,所述小角度注入的角度范围为0~10度。 提供一种非对称低中压器件,所述非对称低中压器件包括: 衬底区; 位于所述衬底区中的N阱和P阱; 位于所述N阱上方的闸极,所述闸极与所述P阱无重合区域; 位于所述P阱上方第一掺杂区; 位于所述第一掺杂区内的第二掺杂区,所述第一掺杂区与所述第二掺杂区在横向 上的间隔形成沟道。 本发明的积极进步效果在于: 本发明通过在第一掺杂区和第二掺杂区间形成的沟道,与传统的非对称低中压器 件中的沟道相比,沟通长度变短,与传统的非对称低中压器件中的沟道相比,沟通长度变 短,从而有效地降低导通电阻,进而进一步提高Asym-DEMOS的性能。 附图说明 图1为本发明的现有技术的非对称低中压器件的结构示意图。 图2为本发明的实施例1的制作非对称低中压器件的方法的流程示意图。 图3为本发明的实施例1的制作非对称低中压器件的方法中的步骤100的示意图。 图4为本发明的实施例1的制作非对称低中压器件的方法中的步骤101的示意图。 图5为本发明的实施例1的制作非对称低中压器件的方法中的步骤102的示意图。 图6为本发明的实施例1的制作非对称低中压器件的方法中的步骤103的示意图。 图7为本发明的实施例1的制作非对称低中压器件的方法中的步骤104的示意图。 图8为本发明的实施例1的制作非对称低中压器件的方法中的步骤105的示意图。 图9为本发明的实施例1的制作非对称低中压器件的方法中的步骤106的示意图。