技术摘要:

本发明公开了一种三维(3D)体声波(BAW)谐振器,包括:压电膜阵列,包括在衬底与盖帽层之间垂直且水平分布的多个压电膜,垂直方向上相邻压电膜之间具有多个第一空腔,水平的第一方向上相邻压电膜之间具有共用的第二空腔,水平的第二方向上相邻压电膜之间具有共用的第三空 全部

背景技术:

在无线通讯中,射频滤波器作为过滤特定频率信号的中介,用于减少不同频段的 信号干扰,在无线收发器中实现镜像消除、寄生滤波和信道选择等功能。随着4GLTE网络的 部署和市场的增长,射频前端的设计朝着小型化、低功耗和集成化的方向发展,市场对滤波 性能的要求也越来越高。由于薄膜体声波谐振器(FilmBulkAcousticResonator,简称 “FBAR”,也称“体声波”,BulkAcousticWave,简称“BAW”,)具有尺寸小、工作频率高、功耗低、 品质因数(Q值)高、直接输出频率信号、与CMOS工艺兼容等特点,目前已经成为射频通讯领 域重要的器件被广泛应用。 FBAR是制作在衬底材料上的电极——压电膜——电极的三明治结构的薄膜器件。 FBAR的结构有空腔型、布拉格反射型(SMR)和背面刻蚀型。其中空腔型FBAR相对SMR型Q值要 高,损耗要小,机电耦合系数要高;相对于背面刻蚀型FBAR不需要去掉大面积的衬底,机械 强度较高。因此,空腔型FBAR是集成于CMOS器件上的首选。 然而,由于制造复杂,现有的BAW滤波器和体声谐振器(BAR)被制造为独立的平面 型或二维(2D)布局的装置。也就是说,BAW滤波器和体声谐振器(BAR)并未被提供为与其他 的CMOS、BIiCMOS、SiGe HBT和/或无源器件集成的结构,从而,导致更高的制造成本和增加 的制造工艺。 此外,作为独立器件的2D BAW谐振器体积、面积均较大,集成度较低,难以与其驱 动电路采用CMOS工艺制造在相同芯片上,更难以与FinFET、NAND存储器等3D器件一起集成。 而如果采用3D封装技术将多个2D BAW谐振器层叠在一起,虽然能有效提高集成度,但是每 个芯片均需要采用接合(bonding)、背面研磨减薄(grinding)以及穿硅通孔(TSV)技术以减 小封装高度,工艺复杂且需要极高的对准精度,制造成本高。此外,这种3D封装还存在布线 复杂、寄生阻抗大的问题。

技术实现要素:

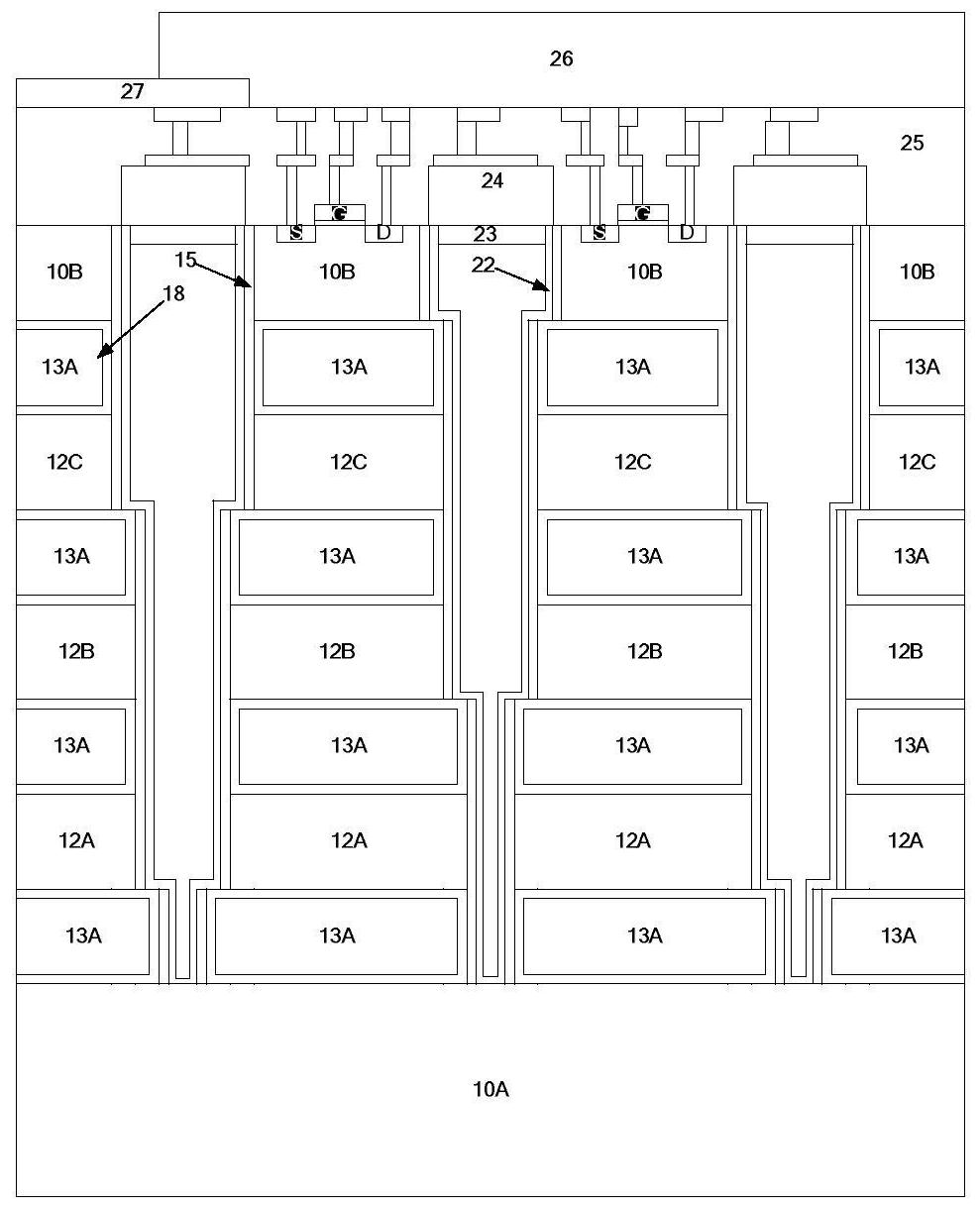

因此,本发明的目的在于提供一种克服以上技术障碍的3D BAW谐振器及其制备方 法。 本发明提供了一种三维(3D)体声波(BAW)谐振器,包括: 压电膜阵列,包括在衬底与盖帽层之间垂直且水平分布的多个压电膜,垂直方向 上相邻压电膜之间具有多个第一空腔,水平的第一方向上相邻压电膜之间具有共用的第二 空腔,水平的第二方向上相邻压电膜之间具有共用的第三空腔; 多个电极层,至少覆盖每个第一空腔的顶面和底面; 电极互连层,沿第三空腔侧面依次连接所述多个电极层。 4 CN 111555728 A 说 明 书 2/8 页 其中,多个第一空腔沿第二方向的宽度从上至下增大,并优选地任意两个相邻第 一空腔仅有一侧对齐;任选地,第二空腔沿第一方向的宽度相等;任选地,第三空腔包括沿 第二方向宽度不等的多个子部分,并优选地任意两个相邻子部分深度不同。 其中,每个第一空腔与共用的第三空腔之间具有电极层、第一隔离层和电极互连 层;任选地,每个第一空腔与共用的第二空腔之间具有第二隔离层和第一密闭层。 其中,衬底和/或盖帽层材料选自体Si、绝缘体上硅(SOI)、体Ge、GeOI、GaN、GaAs、 SiC、InP、GaP,并优选地衬底与盖帽层材料相同;任选地,电极层和/或电极互连层材料为选 自Mo、W、Ru、Al、Cu、Ti、Ta、In、Zn、Zr、Fe、Mg的金属单质、这些金属的合金、这些金属的导电 氧化物或导电氮化物、以及其任意组合;任选地,压电膜的材料为ZnO、AlN、BST、BT、PZT、 PBLN、PT;任选地,第一隔离层和/或第二隔离层的材料为SiOx、SiOC、SiOC、SiOF、SiFC、BSG、 PSG、PBSG或其任意组合,并优选地第一隔离层和第二隔离层材料相同;任选地,第一密闭层 材料为氧化钛、氧化钽、氧化铪、氧化钨。 其中,盖帽层中具有驱动晶体管,通过层间绝缘层中的再布线层电连接至电极互 连层,并优选地通过钝化层中的焊垫电连接至导电凸块;任选地,第三空腔顶部具有第二密 闭层,优选地第二密闭层材料为氮化硅。 本发明还提供了一种三维(3D)体声波(BAW)谐振器制造方法,包括以下步骤: 在衬底上形成交替层叠的多个牺牲层和多个压电层; 在顶部的牺牲层上形成盖帽层,并在盖帽层上形成硬掩模; 依次刻蚀前述各个层直至暴露衬底,形成沿第一方向延伸的多个第一开口; 在每个开口中形成填充层; 刻蚀直至暴露衬底,形成沿第二方向延伸的多个第二开口; 通过第二开口去除多个牺牲层,留下的相邻压电层之间具有多个第一空腔; 通过第二开口至少在第一空腔的顶面和底面形成多个电极层; 在第一开口中形成依次连接多个电极层的电极互连层。 其中,多个第一空腔沿第二方向的宽度从上至下增大,并优选地任意两个相邻第 一空腔仅有一侧对齐;任选地,第二开口沿第一方向的宽度相等;任选地,第一开口包括沿 第二方向宽度不等的多个子部分,并优选地任意两个相邻子部分深度不同。 其中,在每个第一空腔与第一开口之间形成电极层、第一隔离层和电极互连层;任 选地,在每个第一空腔与第二开口之间形成第二隔离层和第一密闭层。 其中,衬底和/或盖帽层材料选自体Si、绝缘体上硅(SOI)、体Ge、GeOI、GaN、GaAs、 SiC、InP、GaP,并优选地衬底与盖帽层材料相同;任选地,电极层和/或电极互连层材料为选 自Mo、W、Ru、Al、Cu、Ti、Ta、In、Zn、Zr、Fe、Mg的金属单质、这些金属的合金、这些金属的导电 氧化物或导电氮化物、以及其任意组合;任选地,牺牲层材料为选自SiGe、SiGeC、SiGeSn、 SiGaN、SiGaP、SiGaAs、InSiN、InSiP、InSiAs、InSiSb、SiInGaAs的半导体材料,或者是选自 无定形碳、石墨烯、氧化石墨烯的非半导体材料;任选地,压电膜的材料为ZnO、AlN、BST、BT、 PZT、PBLN、PT;任选地,第一隔离层和/或第二隔离层的材料为SiOx、SiOC、SiOC、SiOF、SiFC、 BSG、PSG、PBSG或其任意组合,并优选地第一隔离层和第二隔离层材料相同;任选地,第一密 闭层材料为氧化钛、氧化钽、氧化铪、氧化钨。 其中,形成电极互连层之后,在盖帽层中形成驱动晶体管,在驱动晶体管上方形成 5 CN 111555728 A 说 明 书 3/8 页 层间绝缘层和再布线层以电连接至电极互连层,并优选地在再布线层之上形成钝化层和焊 垫以电连接至导电凸块;任选地,在第一开口顶部形成第二密闭层,优选地第二密闭层材料 为氮化硅。 依照本发明的3D BAW谐振器及其制造方法,采用CMOS兼容工艺制造了其中多个空 腔包围压电膜的立体谐振器,减小了体积、增加了集成度,降低了成本。 本发明所述目的,以及在此未列出的其他目的,在本申请独立权利要求的范围内 得以满足。本发明的实施例限定在独立权利要求中,具体特征限定在其从属权利要求中。 附图说明 以下参照附图来详细说明本发明的技术方案,其中: 图1A显示了根据本发明实施例的谐振器制造工艺的平视图,图1B显示了沿图1A的 B-B’线的剖面图,图1C显示了沿图1A的A-A’线的剖面图; 图2A显示了根据本发明实施例的谐振器制造工艺的平视图,图2B显示了沿图2A的 B-B’线的剖面图,图2C显示了沿图2A的A-A’线的剖面图; 图3A显示了根据本发明实施例的谐振器制造工艺的平视图,图3B显示了沿图3A的 B-B’线的剖面图,图3C显示了沿图3A的A-A’线的剖面图; 图4A显示了根据本发明实施例的谐振器制造工艺的平视图,图4B显示了沿图4A的 B-B’线的剖面图,图4C显示了沿图4A的A-A’线的剖面图; 图5A显示了根据本发明实施例的谐振器制造工艺的平视图,图5B显示了沿图5A的 B-B’线的剖面图,图5C显示了沿图5A的A-A’线的剖面图; 图6A显示了根据本发明实施例的谐振器制造工艺的平视图,图6B显示了沿图6A的 B-B’线的剖面图,图6C显示了沿图6A的A-A’线的剖面图; 图7A显示了根据本发明实施例的谐振器制造工艺的平视图,图7B显示了沿图7A的 B-B’线的剖面图,图7C显示了沿图7A的A-A’线的剖面图; 图8A显示了根据本发明实施例的谐振器制造工艺的平视图,图8B显示了沿图8A的 B-B’线的剖面图,图8C显示了沿图8A的A-A’线的剖面图; 图9A显示了根据本发明实施例的谐振器制造工艺的平视图,图9B显示了沿图9A的 B-B’线的剖面图,图9C显示了沿图9A的A-A’线的剖面图; 图10A显示了根据本发明实施例的谐振器制造工艺的平视图,图10B显示了沿图 10A的B-B’线的剖面图,图10C显示了沿图10A的A-A’线的剖面图; 图11A显示了根据本发明实施例的谐振器制造工艺的平视图,图11B显示了沿图 11A的B-B’线的剖面图,图11C显示了沿图1A的A-A’线的剖面图; 图12A显示了根据本发明实施例的谐振器制造工艺的平视图,图12B显示了沿图 12A的B-B’线的剖面图,图12C显示了沿图12A的A-A’线的剖面图; 图13A显示了根据本发明实施例的谐振器制造工艺的平视图,图13B显示了沿图 13A的B-B’线的剖面图,图13C显示了沿图13A的A-A’线的剖面图; 图14A显示了根据本发明实施例的谐振器制造工艺的平视图,图14B显示了沿图 14A的B-B’线的剖面图,图14C显示了沿图14A的A-A’线的剖面图; 图15A显示了根据本发明实施例的谐振器制造工艺的平视图,图15B显示了沿图 6 CN 111555728 A 说 明 书 4/8 页 15A的B-B’线的剖面图,图15C显示了沿图1A的A-A’线的剖面图; 图16A显示了根据本发明实施例的谐振器制造工艺的平视图,图16B显示了沿图 16A的B-B’线的剖面图,图16C显示了沿图16A的A-A’线的剖面图; 图17A显示了根据本发明实施例的谐振器制造工艺的平视图,图17B显示了沿图 17A的B-B’线的剖面图,图17C显示了沿图17A的A-A’线的剖面图; 图18A显示了根据本发明实施例的谐振器制造工艺的平视图,图18B显示了沿图 18A的B-B’线的剖面图,图18C显示了沿图18A的A-A’线的剖面图; 图19A显示了根据本发明实施例的谐振器制造工艺的平视图,图19B显示了沿图 19A的B-B’线的剖面图,图19C显示了沿图19A的A-A’线的剖面图; 图20A显示了根据本发明实施例的谐振器制造工艺的平视图,图20B显示了沿图 20A的B-B’线的剖面图,图20C显示了沿图20A的A-A’线的剖面图; 图21A显示了根据本发明实施例的谐振器制造工艺的平视图,图21B显示了沿图 21A的B-B’线的剖面图,图21C显示了沿图21A的A-A’线的剖面图; 图22A显示了根据本发明实施例的谐振器制造工艺的平视图,图22B显示了沿图 22A的B-B’线的剖面图,图22C显示了沿图22A的A-A’线的剖面图; 图23A显示了根据本发明实施例的谐振器制造工艺的平视图,图23B显示了沿图 23A的B-B’线的剖面图,图23C显示了沿图23A的A-A’线的剖面图; 图24A显示了根据本发明实施例的谐振器制造工艺的平视图,图24B显示了沿图 24A的B-B’线的剖面图,图24C显示了沿图24A的A-A’线的剖面图; 图25显示了根据本发明实施例的谐振器制造工艺的剖视图; 图26显示了根据本发明实施例的谐振器制造工艺的剖视图; 图27显示了根据本发明实施例的谐振器制造工艺的剖视图;以及 图28显示了图27的局部放大图。