技术摘要:

本申请涉及芯片验证技术领域,公开了用于监控时钟信号的方法和装置:响应于检测到时钟信号序列中的当前时钟信号的半周期与预设的时钟信号半周期的差值不小于第一预设值,将与当前时钟信号相邻的时序在后的第一预设数量个时钟信号作为待检测时钟信号,获取待检测时钟信 全部

背景技术:

现有技术中,时钟电路的设计对于IC(Integrated Circuit,集成电路)芯片设计 来说尤为重要,稳定且规范的时钟信号是保证芯片电路高效和稳定的前提。在芯片前端验 证过程中,监测时钟电路输出的稳定性非常重要。 目前在IC设计的仿真过程中,主要通过assertion的方式对输出时钟进行监测,即 采用assertion去检测时钟信号的输出,如果发现时钟的周期与预期的时钟周期不同,即报 错。

技术实现要素:

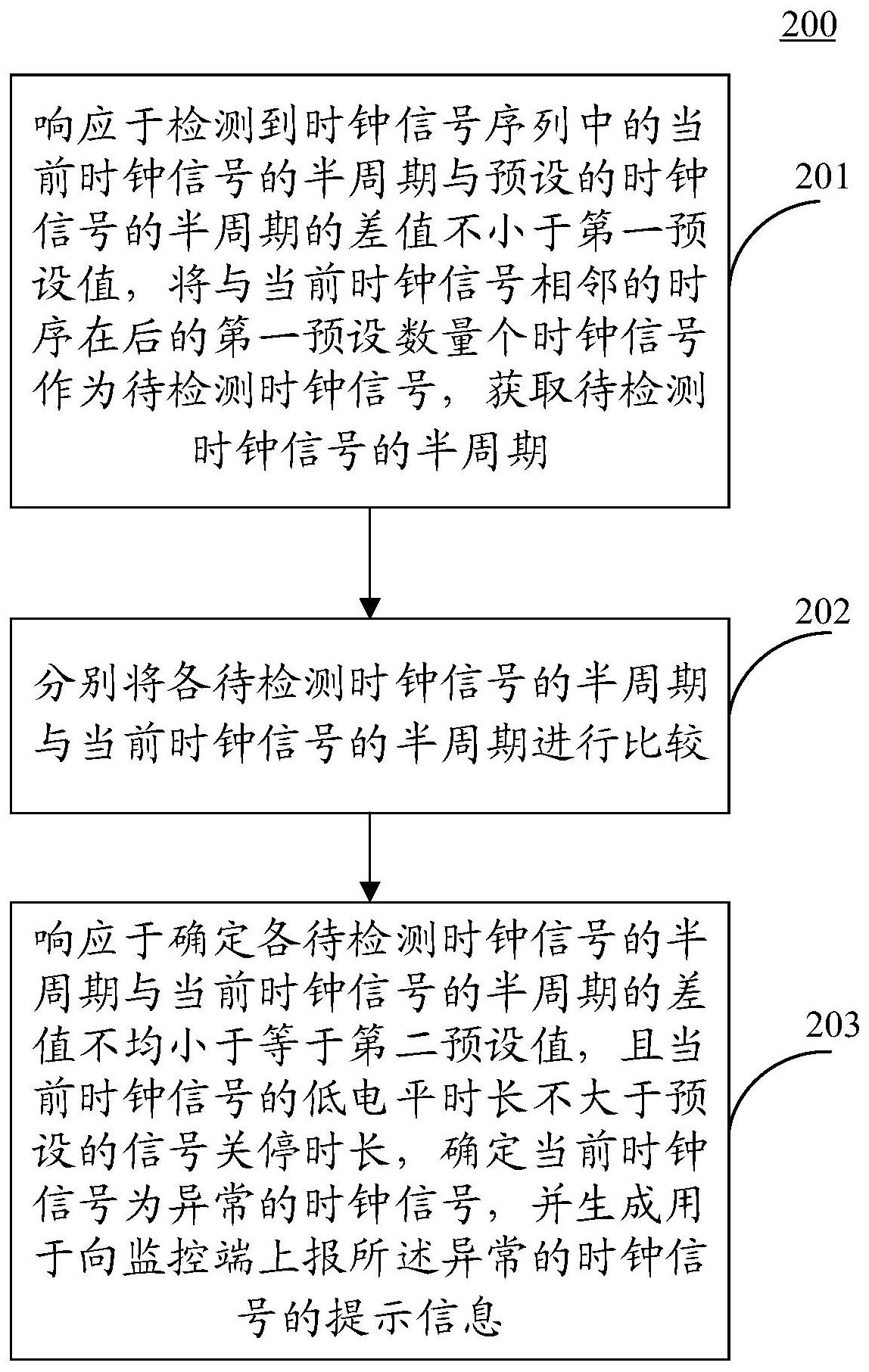

本申请实施例提供了一种用于监控时钟信号的方法、装置、设备以及存储介质。 第一方面,本申请实施例提供了一种用于监控时钟信号的方法,该方法包括:响应 于检测到时钟信号序列中的当前时钟信号的半周期与预设的时钟信号的半周期的差值不 小于第一预设值,将与当前时钟信号相邻的时序在后的第一预设数量个时钟信号作为待检 测时钟信号,获取待检测时钟信号的半周期;分别将各待检测时钟信号的半周期与当前时 钟信号的半周期进行比较;响应于确定各待检测时钟信号的半周期与当前时钟信号的半周 期的差值不均小于等于第二预设值,且当前时钟信号的低电平时长不大于预设的信号关停 时长,确定当前时钟信号为异常的时钟信号,并生成用于向监控端上报异常的时钟信号的 提示信息。 在一些实施例中,该方法还包括:响应于确定各待检测时钟信号的半周期与当前 时钟信号的半周期的差值均小于等于第二预设值,则确定当前时钟信号的周期发生了变更 并记录当前时钟信号的周期;检测是否存在预先接收到的时钟信号周期变更指令,时钟信 号周期变更指令包括要求变更的时钟信号周期;响应于存在预先接收到的时钟信号周期变 更指令,且要求变更的时钟信号周期与所述当前时钟信号的周期的差值小于等于第三预设 值,确定当前时钟信号的周期变更为合法变更。 在一些实施例中,该方法还包括:响应于不存在预先接收到的时钟信号周期变更 指令,确定当前时钟信号的周期变更不合法,并生成用于向监控端上报非法时钟周期变更 的提示信息。 在一些实施例中,该方法还包括:响应于确定各待检测时钟信号的半周期与当前 时钟信号的半周期的差值不均小于等于第二预设值,且当前时钟信号的低电平时长大于预 设的信号关停时长、在当前时钟信号之前接收到关停信号的指令,则确定当前时钟信号为 关停信号。 在一些实施例中,第一预设值基于与当前时钟信号相邻的时序在前的第二预设数 4 CN 111611768 A 说 明 书 2/10 页 量个时钟信号的周期的平均值确定。 第二方面,本申请实施例提供了一种用于监控时钟信号的装置,该装置包括:获取 模块,被配置成响应于检测到时钟信号序列中的当前时钟信号的半周期与预设的时钟信号 的半周期的差值不小于第一预设值,将与当前时钟信号相邻的时序在后的第一预设数量个 时钟信号作为待检测时钟信号,获取待检测时钟信号的半周期;比较模块,被配置成分别将 各待检测时钟信号的半周期与当前时钟信号的半周期进行比较;生成模块,被配置成响应 于确定各待检测时钟信号的半周期与当前时钟信号的半周期的差值不均小于等于第二预 设值,且当前时钟信号的低电平时长不大于预设的信号关停时长,确定所述当前时钟信号 为异常的时钟信号,并生成用于向监控端上报所述异常的时钟信号的提示信息。 在一些实施例中,该装置还包括:确定模块,被配置成响应于确定各所述待检测时 钟信号的半周期与当前时钟信号的半周期的差值均小于等于第二预设值,则确定当前时钟 信号的周期发生了变更并记录当前时钟信号的周期;检测模块,被配置成检测是否存在预 先接收到的时钟信号周期变更指令,所述时钟信号周期变更指令包括要求变更的时钟信号 周期;变更模块,被配置成响应于存在预先接收到的时钟信号周期变更指令,且要求变更的 时钟信号周期与所述当前时钟信号的周期的差值小于等于第三预设值,确定当前时钟信号 的周期变更为合法变更。 在一些实施例中,该装置还包括:提示模块,被配置成响应于不存在预先接收到的 时钟信号周期变更指令,确定当前时钟信号的周期变更不合法,并生成用于向监控端上报 非法时钟周期变更的提示信息。 在一些实施例中,该装置还包括:关停模块,被配置成响应于确定各所述待检测时 钟信号的半周期与当前时钟信号的半周期的差值不均小于等于第二预设值,且当前时钟信 号的低电平时长大于预设的信号关停时长、在当前时钟信号之前接收到关停信号的指令, 则确定当前时钟信号为关停信号。 在一些实施例中,第一预设值基于与当前时钟信号相邻的时序在前的第二预设数 量个时钟信号的周期的平均值确定。 第三方面,本申请实施例提供了一种电子设备,该电子设备包括一个或多个处理 器;存储装置,其上存储有一个或多个程序,当一个或多个程序被该一个或多个处理器执 行,使得一个或多个处理器实现如第一方面的任一实施例的用于监控时钟信号的方法。 第四方面,本申请实施例提供了一种计算机可读介质,其上存储有计算机程序,该 程序被处理器执行时实现如第一方面的任一实施例的用于监控时钟信号的方法。 本申请通过响应于检测到时钟信号序列中的当前时钟信号的半周期与预设的时 钟信号半周期的差值不小于第一预设值,将与当前时钟信号相邻的时序在后的第一预设数 量个时钟信号作为待检测时钟信号,获取待检测时钟信号的半周期;分别将各待检测时钟 信号的半周期与当前时钟信号的半周期进行比较;响应于确定各待检测时钟信号的半周期 与当前时钟信号的半周期的差值不均小于等于第二预设值,且当前时钟信号的低电平时长 不大于预设的信号关停时长,确定当前时钟信号为异常的时钟信号,并生成用于向监控端 上报异常的时钟信号的提示信息,有效排除了当前时钟信号的正常频率变更及时钟关停的 情况,进而有效提高了对异常的时钟信号进行监控的准确性和即时性。 应当理解,本部分所描述的内容并非旨在标识本公开的实施例的关键或重要特 5 CN 111611768 A 说 明 书 3/10 页 征,也不用于限制本公开的范围。本公开的其他特征将通过以下的说明书而变得容易理解。 附图说明 图1是本申请可以应用于其中的示例性系统架构图; 图2是根据本申请的用于监控时钟信号的方法的一个实施例的流程图; 图3是根据本申请的用于监控时钟信号的方法的一个应用场景的示意图; 图4是根据本申请的用于监控时钟信号的方法的又一个实施例的流程图; 图5是根据本申请的用于监控时钟信号的方法的另一个实施例的流程图; 图6是根据本申请的用于监控时钟信号的装置的一个实施例的示意图; 图7是适于用来实现本申请实施例的服务器的计算机系统的结构示意图。