技术摘要:

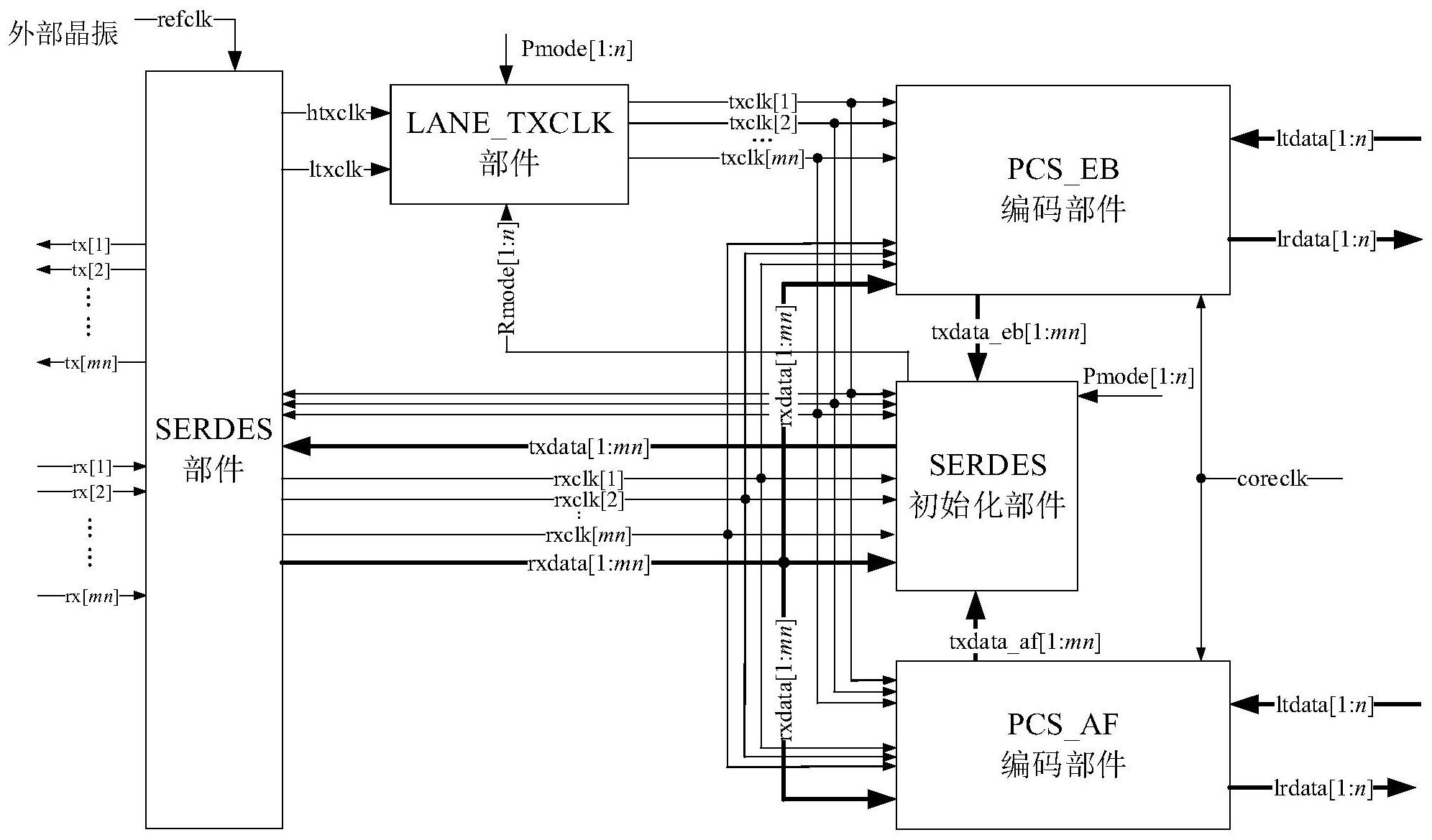

本发明公开了一种面向融合网络的多模互连接口控制器,包括:负责串/并转换的SERDES部件,负责产生发送时钟的LANE_TXCLK部件,负责链路训练和速率协商的SERDES初始化部件,负责报文物理层编码的PCS_EB编码部件和PCS_AF编码部件。通过共享的SERDES初始化部件,自动完成链 全部

背景技术:

互连芯片广泛应用于数据中心、HPC(High Performance Computing,高性能计 算)、多路服务器领域,链路速率持续上升同时呈现出不同应用特征。数据中心网络持续向 400G更高带宽发展。随着视频业务和未来5G业务逐步普及,400G以太网互连芯片市场已初 见端倪。2018年Marvell推出了支持400G以太网的收发芯片,兼容IEEE802.3cd标准,满足人 工智能、机器学习等新兴应用对带宽超高需求。2018年美国博通公司交付战斧3系列交换机 芯片,支持单芯片32x400G,64x200G或128x100G速率交换路由,标志数据中心400G以太网时 代很快到来。高性能计算机普遍采取的专用高速互连在追求带宽同时强调低延迟和高可 靠。目前高性能计算机排行榜TOP4排名的山峰、太湖之光、山脊、天河二号均采取100G互连, 跳步延迟小于100ns。下一代专用互连瞄准200G速率。2018年美国迈络思公司推出HDR(High Data Rate,高速数据传输技术)交换芯片,端口含4通道50G信号,但误码率降低约6个量级, 其互连接口引入200ns左右延迟难以适合部分HPC应用,亟需进一步降低端口延迟。 互连芯片通常区分以数据中心为中心的以太网芯片和以高性能计算机为中心的 专用高速网络芯片两个市场。这两类互连芯片以美国博通公司和迈络思公司为典型代表, 面向应用需求不同,近二十年来两者市场相互并存。然而,近些年来随着数据中心业务范畴 不断扩张,传统专用网络也开始具备以太网应用特征来满足云计算需求;同时未来数据中 心由于AI应用逐步普及,也开始强调以太网络具备低延迟特性。目前业界中以太网络和专 用网络两者融合趋势逐渐形成。美国迈络思公司最早专注高性能专用互连研发,而2016年 高速专用互连网卡ConnectX同时配置了双网功能,节省了系统构建成本,目前暂未出现双 网融合交换芯片。2019年美国克雷面向E级计算机推出了Slingshot互连芯片,与前几代最 大区别在于集成以太网功能,在400G以太网协议基础上设计了精简HPC互连技术,具备低延 迟高带宽特性同时满足了数据中心应用需求。2019年以太网联盟参考IB规范宣布推出适用 于50G、100G和200G以太网的低延迟FEC(Forward Error Correction,前向纠错)规范,低延 迟FEC使以太网更好适用HPC、机器学习和金融交易对互连性能的较高要求。 两类互连接口一般采取不同电路结构。以太网络互连接口设计遵循以太网标准, 追求高带宽低成本特性,可以容忍较高延迟。以太网络互连接口采取基于弹性缓冲的物理 编码层设计,放松了核心交换时钟和SERDES发送时钟之间约束具有更好的通用性,但需要 择机插入/删除空闲字符引入了较大延迟。相比之下,专用高速网络采取更多定制性设计, 追求高带宽低延迟特性。专用高速网络物理编码层工作在SERDES发送时钟域,采取异步缓 冲避免了弹性缓冲引入的较大延迟。 要实现以太网络和专用高速网络双网融合,在相同芯片内部同时集成两种网络互 连接口,需要解决两类网络互连接口控制器并存所带来的时钟产生问题、数据通路及初始 7 CN 111600813 A 说 明 书 2/11 页 化功能共享等问题。

技术实现要素:

针对专用高速网络和以太网络双网融合,在相同芯片内部同时集成两种网络互连 接口,需要解决两类互连接口控制器并存所带来的时钟产生问题、数据通路及初始化功能 共享等问题,本发明提供一种面向融合网络的多模互连接口控制器,通过配置端口模式寄 存器支持两种类型物理层编码部件切换工作;提供共享的SERDES初始化部件,自动完成链 路训练和速率协商;提供基于弹性缓冲(Elastic Buffer)的物理层编码部件(简称PCS_EB 编码部件)给互连芯片设计提供更多通用性灵活性;提供基于异步缓冲(Asynchronous Buffer)的物理层编码部件(简称PCS_AF编码部件)降低报文穿透延迟。本发明可以通过灵 活配置使单块芯片能够满足专用高速网络和以太网络传输需求。 本发明采用的技术方案如下: 面向融合网络的多模互连接口控制器,包括:负责串/并转换的SERDES部件,负责 产生发送时钟的LANE_TXCLK部件(LANE for Transmit Clock,发送时钟产生部件),负责链 路训练和速率协商的SERDES初始化部件,负责报文物理层编码的PCS_EB编码部件和PCS_AF 编码部件。针对任意端口来说,PCS_EB编码部件和PCS_AF编码部件任意时刻只有唯一部件 工作。 SERDES部件作为所述面向融合网络的多模互连接口控制器的入口,对外连接参考 时钟refclk、mn条输入链路rx[1:mn]和mn条输出链路tx[1:mn](m和n为正整数),对内连接 LANE_TXCLK部件、SERDES初始化部件、PCS_EB编码部件和PCS_AF编码部件,SERDES部件负责 m个端口收发数据的串/并和并/串转换。其中,rx[1:mn]为mn个数组rx[1]、…、rx[mn]的简 化表示,tx[1:mn]为mn个数组tx[1]、…、tx[mn]的简化表示,数组缩写[1:mn]为1~mn的简 化表示。SERDES部件从外部晶振接收参考时钟refclk,产生高频传输时钟htxclk和中频传 输时钟ltxclk发给LANE_TXCLK部件;SERDES部件从SERDES初始化部件接收mn路链路有效数 据txdata[1:mn]数据,从LANE_TXCLK部件接收mn路发送时钟txclk[1:mn],利用txclk[i]对 txdata[i]进行采样且完成并/串转换后产生发送串行数据tx[i],并将发送串行数据tx[i] 向外输出,i为正整数,且i≤mn;SERDES部件从mn条输入链路rx[1:mn]接收串行数据,进行 串/并转换恢复产生接收数据rxdata[1:mn]和恢复时钟rxclk[1:mn],并将接收数据rxdata [1:mn]和恢复时钟rxclk[1:mn]发送给SERDES初始化部件、PCS_EB编码部件和PCS_AF编码 部件。 LANE_TXCLK部件与SERDES初始化部件、PCS_EB编码部件、PCS_AF编码部件和 SERDES部件相连,负责产生n个端口mn条链路的发送时钟txclk[1:mn]。LANE_TXCLK部件从 SERDES部件接收高频传输时钟htxclk和中频传输时钟ltxclk,从SERDES初始化部件接收速 率配置寄存器值Rmode[1:n],从全局寄存器接收模式配置寄存器值Pmode[1:n],产生mn条 链路上的发送时钟txclk[1:mn],并将发送时钟txclk[1:mn]发送给SERDES初始化部件、 PCS_EB编码部件、PCS_AF编码部件和SERDES部件。 SERDES初始化部件与SERDES部件、PCS_EB编码部件、PCS_AF编码部件和LANE_ TXCLK部件相连,负责n个端口输出链路的均衡参数训练和速率协商,并且根据配置寄存器 取值Pmode[1:n]产生mn条输出链路有效数据txdata[1:mn]发给SERDES部件,实现初始化功 8 CN 111600813 A 说 明 书 3/11 页 能和数据通路功能共享。SERDES初始化部件从全局寄存器接收模式配置寄存器值Pmode[1: n],产生速率配置寄存器值Rmode[1:n],并发送给SERDES初始化部件;SERDES初始化部件从 SERDES部件接收数据rxdata[1:mn]和恢复时钟rxclk[1:mn]进行参数训练和速率协商,从 LANE_TXCLK部件接收发送时钟txclk[1:mn],从PCS_EB编码部件接收有效数据txdata_eb [1:mn],从PCS_AF编码部件接收有效数据txdata_af[1:mn],产生链路有效数据txdata[1: mn]并发送给SERDES部件。 PCS_EB编码部件与LANE_TXCLK部件、SERDES部件、SERDES初始化部件相连,负责对 所属n个端口mn条链路上有效数据rxdata[1:mn]进行编码。PCS_EB编码部件从LANE_TXCLK 部件接收txclk[1:mn],从外部接收核心时钟coreclk,从SERDES部件接收恢复时钟rxclk [1:mn],采取弹性缓冲完成核心时钟coreclk与SERDES收发时钟txclk/rxclk之间的跨时钟 域数据传输;PCS_EB编码部件从链路层接收n个端口的报文数据ltdata[1:n],经物理层编 码后发送txdata_eb[1:mn]给SERDES初始化部件;PCS_EB编码部件从SERDES部件接收数据 rxdata[1:mn]和恢复时钟rxclk[1:mn],经物理层解码后发送lrdata[1:n]报文数据给链路 层。 PCS_AF编码部件与LANE_TXCLK部件、SERDES部件、SERDES初始化部件相连,负责对 所属n个端口mn条链路有效数据rxdata[1:mn]进行编码。PCS_AF编码部件要求内核频率 coreclk不低于txclk/rxclk频率,要求同端口m条链路发送时钟相同相位。PCS_AF编码部件 从LANE_TXCLK部件接收txclk[1:mn],从外部接收核心时钟coreclk,从SERDES部件接收恢 复时钟rxclk[1:mn],采取异步缓冲完成核心时钟coreclk与SERDES收发时钟txclk/rxclk 之间的跨时钟域数据传输;PCS_AF编码部件从链路层接收n个端口报文数据ltdata[1:n], 经物理层编码后发送txdata_af[1:mn]给SERDES初始化部件;PCS_AF编码部件从SERDES部 件接收数据rxdata[1:mn]和恢复时钟rxclk[1:mn],经物理层解码后发送lrdata[1:n]报文 数据给链路层。 进一步,SERDES初始化部件包括:n个端口初始化单元,n个模式多路选择单元 DMUX1~DMUXn,n个初始化多路选择单元IMUX1~IMUXn。 第j个端口初始化单元与LANE_TXCLK部件、SERDES部件和多路选择单元IMUXj相 连,从LANE_TXCLK部件接收m路发送时钟txclk[(j-1)m 1:(j-1)m m],经过端口处理后,向 初始化多路选择单元IMUXj发送训练测试帧数据txdata_i[(j-1)m 1:(j-1)m m],向LANE_ TXCLK部件发送速率配置寄存器值Rmode[j],j为整数,1整j≤n;从SERDES部件接收数据 rxdata[(j-1)m 1:(j-1)m m]和恢复时钟rxclk[(j-1)m 1:(j-1)m m],在接收训练测试帧 校验结束后,发送初始化结束信号init[j]给初始化多路选择单元IMUXj。 第j个模式多路选择单元DMUXj与PCS_EB编码部件、PCS_AF编码部件以及第j个模 式初始化多路选择单元IMUXj相连,从PCS_EB编码部件接收有效数据信号txdata_eb[(j-1) m 1:(j-1)m m],从PCS_AF编码部件接收有效数据信号txdata_ef[(j-1)m 1:(j-1)m m],根 据端口配置寄存器Pmode[j]选择产生临时数据发送给IMUXj。 第j个模式初始化多路选择单元IMUXj与第j个模式多路选择单元DMUXj、第j个端 口初始化单元以及SERDES部件相连,从DMUXj单元接收临时数据,从第j个端口初始化单元 接收训练测试帧数据txdata_i[(j-1)m 1:(j-1)m m]和init[j],根据init[j]值选择产生 有效数据信号txdata[(j-1)m 1:(j-1)m m]发送给SERDES部件。 9 CN 111600813 A 说 明 书 4/11 页 进一步,端口初始化单元j采取以下步骤完成第j个端口输出链路的均衡参数训练 和端口速率协商: 步骤1):上电复位时,进入初始化状态。若收到软件启动训练命令,或收到SERDES 部件的rxdata[(j-1)m 1:(j-1)m m]数据属于训练测试帧,转向步骤2)进行参数训练和速 率协商; 步骤2):采取最低速率rate[0]交换协商参数,至少包括j端口支持的w个传输速 率,w为自然数。记j端口支持的w个传输速率rate[f],1af≤w,f为自然数,rate[f]按照速率 降序排列,即若u≤v,则rate[u]ate[序排v],rate[0]为j端口支持的最低速率。交换参数后 设置f=1,转向步骤3); 步骤3):根据速率rate[f],设置速率配置寄存器Rmode[j]发送给LANE_TXCLK部 件。然后初始化发送均衡参数,转向步骤4); 步骤4):通过有效数据信号txdata_i[(j-1)m 1:(j-1)m m]发送训练测试帧,并接 收来自rxdata[(j-1)m 1:(j-1)m m]上的训练测试帧。若接收训练测试帧校验正确,确定协 商速率rate[f]和发送端均衡参数,整个流程结束;若接收训练测试帧校验失败,进入步骤 5); 步骤5):调整发送端均衡参数。如果调整成功那么尝试下一个均衡参数,继续回到 步骤4),否则表示速率rate[f]采取所有均衡参数都无效,转向步骤6); 步骤6):尝试下个速率继续协商,f=f 1。若f>w,那么表示只有最低速率rate[0] 成功,确定协商速率rate[0],整个流程结束;否则尝试下一个速率,转向步骤3)。 进一步,LANE_TXCLK部件由mn个Txclk速率调整单元和n个Txclk模式调整单元组 成,且每m个Txclk速率调整单元对应一个Txclk模式调整单元。第k个(1(k≤mn)Txclk速率 调整单元根据来自SERDES初始化部件的速率配置寄存器值Rmode[1:n],产生链路k的临时 发送时钟txclk_t[k]。第k个Txclk速率调整单元与SERDES部件、第l个Txclk模式调整单元 相连 由六个分频单元DIV_p1~DIV_p6和七个时钟MUX选择单元RMux1~RMux7组 成。分频单元DIV_p1、DIV_p2和DIV_p3分别从SERDES部件接收高频时钟htxclk,经过p1、p2 和p3分频后产生分频时钟分别给RMux1单元OSC0端、RMux1单元和RMux3单元OSC1端,p1、p2 和p3为大于2的整数,OSC0与OSC1为晶振、振荡器(Oscillator)引脚;分频单元DIV_p4、DIV_ p5和DIV_p6分别从SERDES部件接收中频时钟ltxclk,经过p4、p5和p6分频后产生分频时钟 给RMux2单元OSC0端、RMux2单元和RMux4单元OSC1端,p4、p5和p6为大于2的整数。RMux1单元 接收来自DIV_p1的p1分频时钟和p2分频时钟,根据Rmode[l]值选择产生Txclk临时时钟1至 RMux3的OSC0端;RMux3单元接收Txclk临时时钟1和来自DIV_p3的p3分频时钟,根据Rmode [l]值选择产生Txclk临时时钟2至RMux5的OSC0端;RMux5单元接收Txclk临时时钟2和来自 SERDES部件的htxclk时钟,根据Rmode[l]值选择产生临时时钟3至RMux7单元的OSC0端。 RMux2单元、RMux4单元和RMux6单元根据Rmode[l]值选择产生临时时钟6至RMux7单元的 OSC1端。最后RMux7单元根据Rmode[l]值选择产生第i条链路的临时发送时钟txclk_t[k]给 第l个Txclk模式调整单元。上述Txclk速率调整单元根据速率配置寄存器具体取值Rmode [l]可以产生htxclk、htxclk/p1、htxclk/p2、htxclk/p3和ltxclk、ltxclk/p4、ltxclk/p5、 ltxclk/p6共八种临时发送时钟频率。 第l个Txclk模式调整单元负责根据模式配置寄存器值Pmode[l],产生l端口m路发 10 CN 111600813 A 说 明 书 5/11 页 送时钟txclk[(l-1)m 1:(l-1)m m]给LANE_TXCLK部件、SERDES初始化部件、PCS_EB编码部 件和PCS_AF编码部件。由于PCS_EB编码部件对同端口m条链路的发送时钟允许不同相位,而 PCS_AF编码部件对同端口m条链路发送时钟要求相同相位,因此Txclk模式调整单元分别对 两种需求产生不同发送时钟。第l个Txclk模式调整单元由m-1个时钟MUX选择单元PMux2~ PMuxm组成。第l个Txclk模式调整单元从第(l-1)m 1个至第(l-1)m m个TXCLK速率调整单元 接收临时发送时钟,记为txclk_t[(l-1)m 1:(l-1)m m]。若Pmode[l]等于1表示以太网模 式,PMux2~PMuxm单元选择txclk_t[(l-1)m 1:(l-1)m m]作为l端口m路发送时钟txclk [(l-1)m 1:(l-1)m m];若Pmode[l]等于0表示专用高速网模式,选择txclk_t[(l-1)m 1]复 制m份作为l端口m路发送时钟txclk[(l-1)m 1:(l-1)m m]。为此,Txclk模式调整单元根据 Pmode[l]选择产生同端口m路发送时钟是否为同相位时钟。进一步,PCS_EB编码部件由n个 EPD模块和n个EPCS模块组成。第j个EPD模块,记为EPD_j模块,负责端口j数据宽度适配和有 效数据监测。EPD_j模块与LANE_TXCLK部件、SERDES部件、SERDES初始化部件以及第j个EPCS 模块(记为EPCS_j模块)相连。EPD_j模块包括m个弹性缓冲TF_1,…,TF_r,…,TF_m,m个变速 器TG_1,…,TG_r,…,TG_m,m个弹性缓冲RF_1,…,RF_r,…,RF_m,m个同步锁定RL_1,…,RL_ r,…,RL_m,m个变速器RG_1,…,RG_r,…,RG_m,1≤r≤m,r为自然数。在发送方向,EPD_j模 块从LANE_TXCLK部件接收发送时钟txclk[(j-1)m 1:(j-1)m m],将时钟txclk[j*m r]发给 变速器TG_r和弹性缓冲TF_r。弹性缓冲TF_r写端口工作在核心时钟域coreclk,从EPCS_j模 块接收j端口m路数据;TF_r择机动态插入或删除空闲字符;弹性缓冲TF_r读端口工作在 txclk[(j-1)m r],读出数据发给变速器TG_r。EPD_j模块的变速器TG_r从弹性缓冲TF_r接 收数据,完成宽度转换后发送数据txdata_eb[(j-1)m r]给SERDES初始化部件。在接收方 向,EPD_j模块从SERDES部件接收端口j上的数据rxdata[(j-1)m 1:(j-1)m m]和恢复时钟 rxclk[(j-1)m 1:(j-1)m m],发送rxclk[(j-1)m r]给变速器RG_r、锁定单元RL_r和弹性缓 冲RF_r。变速器RG_r从SERDES部件接收数据rxdata[(j-1)m r],完成宽度转换后发给锁定 单元RL_r。锁定单元RL_r判定链路被锁定后再将数据发给弹性缓冲RF_r。弹性缓冲RF_r写 端口工作在rxclk[(j-1)m r]时钟域;弹性缓冲RF_r择机动态插入或删除空闲字符;弹性缓 冲RF_r读端口工作在核心时钟域coreclk,读出有效数据发给EPCS_j模块。 EPCS_j模块与EPD_j模块相连,工作在核心时钟域coreclk。EPCS_j模块接收链路 层输入报文ltdata[j]进行66B/64B编码或FEC编码,然后再将j端口m路有效数据发给EPD_j 模块的TF_1至TF_m;EPCS_j模块从EPD_j模块中RF_1至RF_m接收m路有效数据,进行66B/64B 解码或FEC解码后输出报文lrdata[j]给链路层。进一步,PCS_AF编码部件由n个HPD模块、n 个HPCS模块、n个发送异步缓冲TAF和n个接收异步缓冲RAF组成。第j个HPD模块记为HPD_j模 块,与LANE_TXCLK部件、第j个HPCS模块(记为HPCS_j模块)、SERDES初始化部件、SERDES部件 相连。HPD_j模块包括m个变速器TG_1 ,…,TG_r,…,TG_m,m个同步锁定RL_1 ,…,RL_r,…, RL_m,m个变速器RG_1,…,RG_r,…,RG_m,1≤r≤m,r为自然数。HPD_j模块从LANE_TXCLK部 件接收发送时钟txclk[(j-1)m 1:(j-1)m m],将发送时钟txclk[(j-1)m 1]发给HPCS_j模 块,将发送时钟txclk[(j-1)m r]发给m个变速器TG_r,r=1,…,m。由于此时LANE_TXCLK部 件的输入Rmode[j]等于1,因此对任意r(1因r≤m)存在txclk[(j-1)m r]与txclk[(j-1)m 1]为相同时钟。变速器TG_r从HPCS模块接收数据,完成宽度转换后发送数据txdata_af[(j- 1)m r]给SERDES初始化部件。HPD_j模块从SERDES部件接收数据rxdata[(j-1)m 1:(j-1)m 11 CN 111600813 A 说 明 书 6/11 页 m]和恢复时钟rxclk[(j-1)m 1:(j-1)m m],发送rxclk[(j-1)m r]给变速器RG_r、锁定单元 RL_r。变速器RG_r从SERDES部件接收数据rxdata[(j-1)m r],完成宽度转换后发给锁定单 元RL_r。锁定单元RL_r判定链路被锁定后发送数据给第j个HPCS_j模块。 HPCS_j模块工作在txclk[(j-1)m 1]时钟域,与HPD_j模块、异步缓冲TAF_j、异步 缓冲RAF_j相连。HPCS_j模块从异步缓冲TAF_j读取报文进行66B/64B编码或FEC编码,然后 发送编码数据给HPD_j模块的变速器TG_1至TG_m;从HPD_j模块的同步锁定RL_1至RL_m接收 链路锁定有效数据,进行66B/64B解码或FEC解码后写入异步缓冲RAF_j。 异步缓冲TAF_j写端口工作在核心时钟域coreclk,与链路层、HPCS_j模块相连。异 步缓冲TAF_j从链路层接收报文数据ltdata[j]进行缓存;异步缓冲TAF_j读端口工作在 txclk[(j-1)m 1]时钟域,读取的报文数据ltdata[j]发给HPCS_j模块进行编码。 异步缓冲RAF_j写端口工作在txclk[(j-1)m 1]时钟域,与链路层、HPCS_j模块相 连。它从HPCS_j模块接收报文数据;异步缓冲RAF_j读端口工作在核心时钟域coreclk,只要 缓冲非空无条件发送报文数据给上层链路层。 与现有技术相比,本发明面向融合网络的多模互连接口控制器具有以下优点: 1.多模互连接口控制器通过配置寄存器可提供两种灵活的SERDES发送时钟方案, 分别支持两种类型物理编码部件。单芯片内集成多模互连接口控制器可同时支持数据中心 以太网和高性能计算专用高速网互连,节省成本并有效支撑云计算、科学计算、智能计算、 机器学习等各类应用; 2.多模互连接口控制器集成SERDES初始化部件,可通过自动调整发送均衡参数来 优化适应各种链路状态下的高速信号质量,并能够完成端口之间最大化传输速率的自动化 协商; 3.多模互连接口控制器集成PCS_EB编码部件,对芯片核心时钟和SERDES收发时钟 之间没有约束,给互连芯片设计提供更多通用性和灵活性; 4.多模互连接口控制器集成PCS_AF编码部件。在核心时钟工作频率略高于SERDES 收发时钟频率前提下采取异步缓冲替代弹性缓冲完成时钟域转换,降低了报文穿透延迟。 附图说明 图1为本发明实施例中的面向融合网络的多模互连接口控制器总体结构图。 图2为本发明实施例中的LANE_TXCLK部件发送时钟产生结构图。 图3为本发明实施例中的SERDES初始化部件结构图。 图4为本发明实施例中端口初始化单元均衡参数训练和速率协商流程图。 图5为本发明实施例中PCS_EB编码部件结构图。 图6为本发明实施例中PCS_AF编码部件结构图。