技术摘要:

本发明涉及半导体技术领域,具体涉及一种芯片封装结构及制备方法。其中,芯片封装结构包括:载片,具有容纳空间;至少一个芯片组,设置在所述容纳空间内;其中,每个所述芯片组包括至少两个堆叠设置且电连接的芯片;封装层,填充所述容纳空间,以对所述至少一个芯片组 全部

背景技术:

现有的芯片封装大体上可以分为堆叠封装(Stacked package)或者堆叠芯片封装 (Stacked die package),其中,所述的堆叠封装是将单个封装体堆叠,所述的堆叠芯片封 装是单芯片堆叠后再封装。 堆叠封装存在多个封装体多次塑封的过程,封装过程复杂,另外由于多次塑封的 塑封层的膨胀系数的不一致性,导致堆叠封装容易产生较大的翘曲问题;且多个封装体堆 积造成尺寸较大,导致系统集成度降低。堆叠芯片封装其最终成品良率受单个芯片影响,若 芯片在堆叠过程中发生偏移,最终会导致产品良率变低。 因此,现有的芯片封装结构集成度较低、尺寸较大,而且还面临着芯片偏移、翘曲 较大等问题,最终导致封装成品良率较低,这些都制约着芯片封装的发展。

技术实现要素:

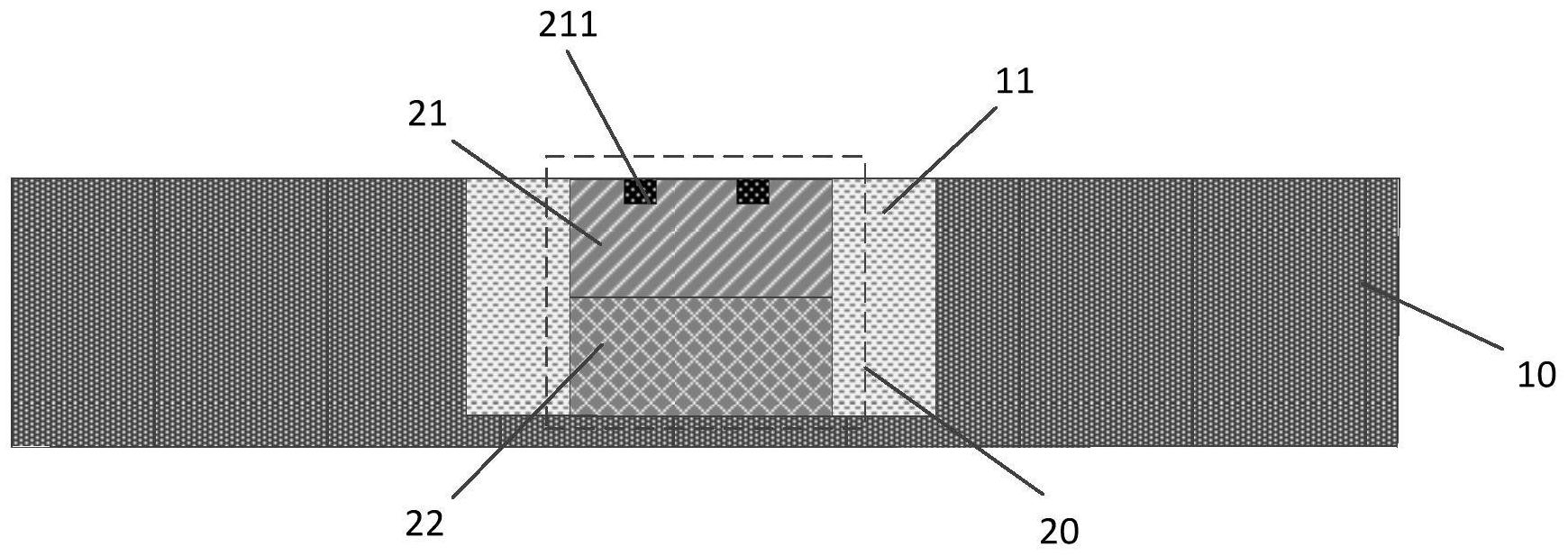

有鉴于此,本发明实施例提供了一种芯片封装结构及制备方法,以解决现有技术 中,芯片封装结构集成度低、尺寸大、芯片偏移、翘曲较大的问题。 根据第一方面,本发明实施例提供了一种芯片封装结构,包括:载片,具有容纳空 间;至少一个芯片组,设置在所述容纳空间内;其中,每个所述芯片组包括至少两个堆叠设 置且电连接的芯片;封装层,填充所述容纳空间,以对所述至少一个芯片组进行封装;其中, 每个所述芯片组中至少一个芯片的表面与所述容纳空间的端面平齐,且所述芯片的表面上 具有第一导电连接点。 本发明实施例提供的芯片封装结构,通过将至少一个芯片组设置在载片的容纳空 间内,其中,每个所述芯片组中的芯片堆叠设置,有效节约所述封装结构的空间尺寸,提高 集成度;利用封装层填充所述载片的容纳空间,将所述至少一个芯片组进行封装,可以避免 传统封装结构在封装过程中容易出现芯片偏移的问题,相比传统封装结构,封装层的层数 越少,翘曲越小。 可选地,所述芯片组内的芯片之间为硅通孔互连结构。 本发明实施例提供的芯片封装结构,芯片组内的芯片之间通过硅通孔互连结构进 行电连接,代替传统封装结构中的金属引线,不仅增强了所述封装结构的电气性能,还缩小 了所述芯片封装结构中的芯片尺寸,提高了集成度。 可选地,所述容纳空间为设置在所述载片上的通孔。 本发明实施例提供的芯片封装结构,将设置在载片上的通孔作为至少一个芯片组 的容纳空间,便于将所述至少一个芯片组放入,使得封装工艺更加简单。 可选地,每个所述芯片组内第一个芯片的表面与所述容纳空间的第一端面平齐, 且所述第一个芯片的表面上具有所述第一导电连接点;最后一个芯片的表面与所述容纳空 4 CN 111584449 A 说 明 书 2/7 页 间的第二端面平齐,且所述最后一个芯片的表面上具有第二导电连接点。 本发明实施例提供的芯片封装结构,每个芯片组内第一芯片的表面以及最后一个 芯片的表面分别与容纳空间的第一端面和第二端面平齐,在所述容纳空间能够集成所述至 少一个芯片组的情况下,节约所述封装层的材料用量,保证所述封装结构第一端面和第二 端面的平整度,为后续的工艺结构提供基础。 可选地,所述容纳空间的第一端面和/或所述第二端面上设置有电连接结构,所述 电连接结构分别与对应的所述第一导电连接点和/或所述第二导电连接点连接。 可选地,所述电连接结构包括:再布线层,形成在所述第一端面和/或所述第二端 面上;凸点单元,形成在所述再布线层上。 本发明实施例提供的芯片封装结构,通过在容纳空间的第一端面和/或第二端面 处设置电连接结构,改变所述容纳空间内设置的芯片组的第一导电连接点和/或第二导电 连接点的位置分布,使其能够与更多的外部产品实现电连接,增加所述芯片组的使用多样 性。 根据第二方面,本发明实施例提供了一种芯片封装结构的制备方法,包括:提供载 片;在所述载片上形成容纳空间,并在所述容纳空间内设置至少一个芯片组;其中,每个所 述芯片组包括至少两个堆叠设置且电连接的芯片;利用封装层填充所述容纳空间,以对所 述至少一个芯片组进行封装;其中,每个所述芯片组中至少一个芯片的表面与所述容纳空 间的端面平齐,且所述表面上具有第一导电连接点。 本发明实施例提供的芯片封装结构的制备方法,通过在载片上形成容纳空间,并 在所述容纳空间内设置至少一个芯片组,,其中,每个所述芯片组中的芯片堆叠设置,有效 节约所述封装结构的空间尺寸,提高集成度;通过封装层将所述至少一个芯片组进行封装, 可以避免传统封装结构在封装过程中容易出现芯片偏移的问题,相比传统封装结构,所述 封装层的层数越少,翘曲越小。 可选地,所述在所述载片上形成容纳空间,并在所述容纳空间内设置有至少一个 芯片组,包括:在所述载片的第一表面上开设凹槽;提供至少两个芯片;在所述凹槽内采用 硅通孔互连结构将所述至少两个芯片堆叠设置形成所述芯片组;其中,所述芯片组中第一 个芯片的表面与所述凹槽的端面平齐,所述第一个芯片表面具有所述第一导电连接点。 本发明实施例提供的芯片封装结构的制备方法,在载片的第一表面开设凹槽,在 所述凹槽内,采用硅通孔互连结构将至少两个芯片堆叠设置,增强所述芯片封装结构的电 气性能,有效节约所述封装结构的空间尺寸,提高集成度,避免传统封装结构在封装过程中 容易出现芯片偏移、翘曲的问题。 可选地,所述方法还包括:在所述凹槽的端面上形成第一电连接结构,所述第一电 连接结构与所述第一个芯片表面的所述第一导电连接点连接。 可选地,所述方法还包括:对所述载片的第二表面进行减薄处理,以露出所述芯片 组中最后一个芯片表面的第二导电连接点;在减薄后的所述载片的第二表面上形成第二电 连接结构,所述第二电连接结构与所述第二导电连接点连接。 本发明实施例提供的芯片封装结构的制备方法,通过在凹槽的端面上形成第一电 连接结构,在减薄后的载片的第二表面形成第二电连接结构,改变芯片组的第一导电连接 点、第二导电连接点的位置分布,使其能够与更多的外部产品实现电连接,增加所述芯片组 5 CN 111584449 A 说 明 书 3/7 页 的使用多样性。 附图说明 为了更清楚地说明本发明