技术摘要:

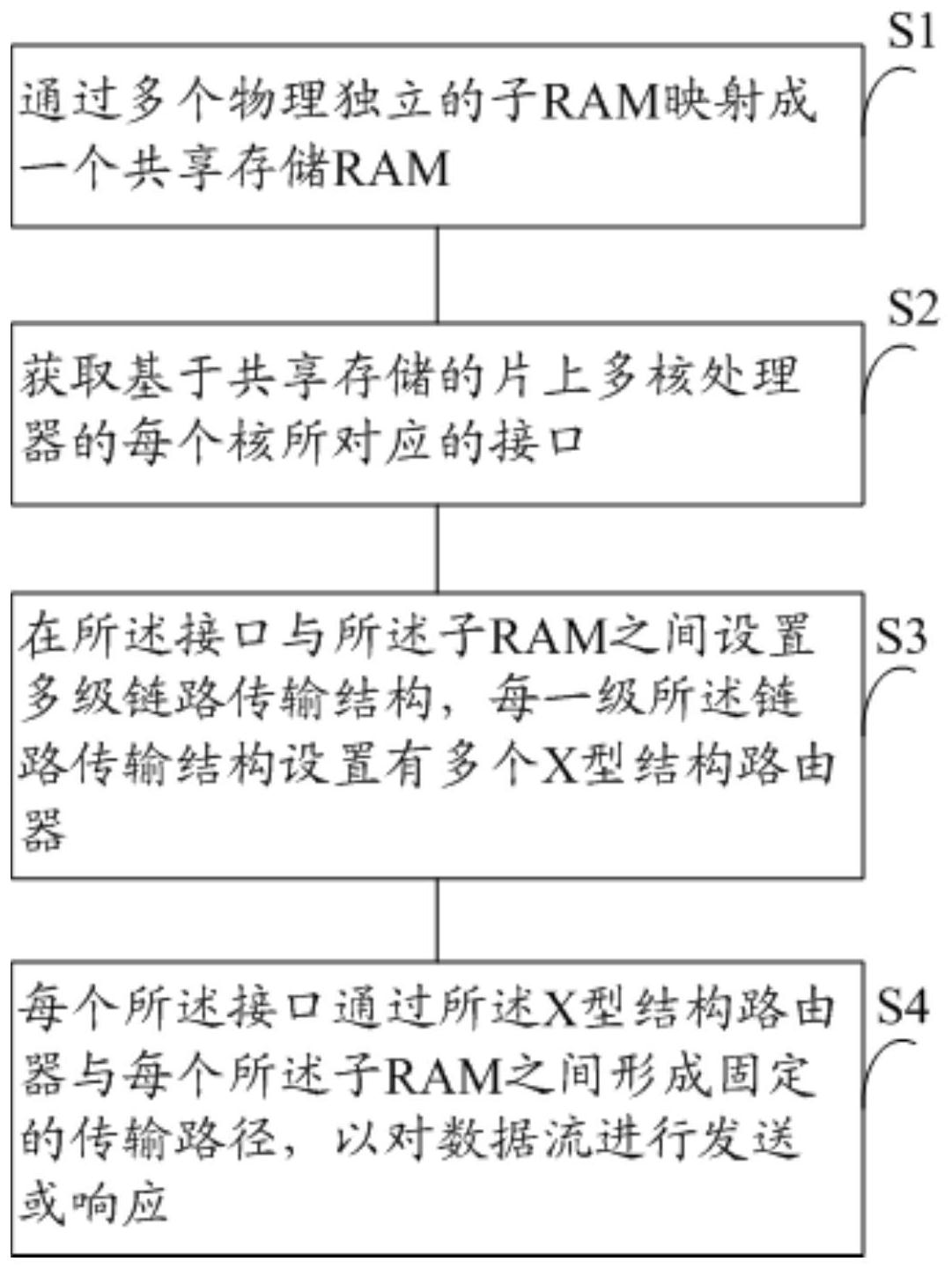

本发明提供一种X型链路结构的多并发RAM数据传输方法及结构,该方法包括:通过多个物理独立的子RAM映射成一个共享存储RAM;获取基于共享存储的片上多核处理器的每个核所对应的接口;在所述接口与所述子RAM之间设置多级链路传输结构,每一级所述链路传输结构设置有多个X 全部

背景技术:

在工艺和应用的双重推动下,片上多核处理器(Chip Multiple Processors;简 称:CMP)成为当前高性能处理器的发展趋势,从专用集成电路 (Application Specific Integrated Circuit;以下简称:ASIC)至现场可编程门阵列(Field Programmable Gate Array;以下简称:FPGA),从云端到边缘。CMP中多核之间的高效数据交互一般是基于共享存 储(多个处理器可以共用一个存储器)的并行体系结构,也就是多并发RAM实现的,这部分已 经成为CMP高运算性能的关键所在。 现有的多并发RAM是基于全连接网络实现的,如图1所示,上面四个接口与下面一 个RAM(四个子RAM通过两个最低有效位来映射成这个 RAM)可以进行多并发的数据传输。接 口数量较少时,这种网络具有高并发和数据流灵活等优点;而接口数量较多(大于4)时,会 导致先入先出队列(First Input First Output;以下简称:FIFO)过多,仲裁电路过于复 杂、交换电路面积过大等问题。基于全连接网络的多并发RAM在接口数量较多时,存在电路 异常复杂的问题。而在实际CMP中,每组共享存储会有四个核,且每个核有多个接口,会造成 多并发RAM电路面积过大且仲裁电路过于复杂,最终会给布局布线造成困难,进而导致电路 整体性能难以提升。

技术实现要素:

本发明提供一种X型链路结构的多并发RAM数据传输方法及结构,解决现有多并发 RAM电路面积过大且仲裁电路过于复杂,造成布局布线困难的问题,相较于现有技术方案, 本发明的方案无需路由FIFO和仲裁电路,因而硬件资源开销小,只有少量扇入扇出的x型路 由器,简化布局布线并有效提升电路主频。 为实现以上目的,本发明提供以下技术方案: 一种X型链路结构的多并发RAM数据传输方法,包括: 通过多个物理独立的子RAM映射成一个共享存储RAM; 获取基于共享存储的片上多核处理器的每个核所对应的接口; 在所述接口与所述子RAM之间设置多级链路传输结构,每一级所述链路传输结构 设置有多个X型结构路由器; 每个所述接口通过所述X型结构路由器与每个所述子RAM之间形成固定的传输路 径,以对数据流进行发送或响应。 优选的,还包括: 所述X型结构路由器设置有两路输入和两路输出,以构成交叉链接状态或直接链 接状态,并按设定时钟周期进行状态切换; 5 CN 111597138 A 说 明 书 2/9 页 通过对每个所述X型结构路由器的状态切换的时钟周期和当前工作状态设置,使 每个所述接口与每个所述子RAM链接的地址时隙均不相同,以形成地址递增或地址递减的 地址时隙规则; 按所述地址时隙规则对所述接口与所述子RAM进行链接,以实现数据交互的全并 发RAM。 优选的,还包括: 按地址递增或地址递减建立地址存储区域; 获取所述接口的数据流,并将所述数据流传输到所述地址存储区域进行存储; 判断所述数据流是否符合所述地址时隙规则,如果否,则对所述数据流传输的地 址时隙进行重新排序,进而根据排序后的地址时隙从所述地址时隙区域中获取数据进行传 送或响应。 优选的,所述X型结构路由器设置有两路输入和两路输出,以构成交叉链接状态或 直接链接状态,并按设定时钟周期进行状态切换,包括: 通过设置X型结构路由器的时钟周期和当前时钟值,并对当前时钟值进行递减计 数,如果当前时钟值递减计数的值为0,则下个时钟周期的所述X型结构路由器的链接状态 将进行切换,否则保持不变; 在进行切换时,所述X型结构路由器由交叉链接状态切换为直接链接状态,或由直 接链接状态切换为交叉链接状态。 优选的,所述X型结构路由器设置有两路输入和两路输出,以构成交叉链接状态或 直接链接状态,并按设定时钟周期进行状态切换,还包括: 在所述X型结构路由器中设置有时钟周期寄存器、计数寄存器和链接寄存器; 所述时钟周期寄存器,用于设置所述X型结构路由器的时钟周期; 所述计数寄存器,用于将当前时钟值设置为计数值,并对计数值进行递减计数,且 所述计数值表征所述X型结构路由器的当前工作状态,在计数值为0时,重新按所述时钟周 期作为计数值,以开始重新计递减计数; 所述链接寄存器,用于存储链接的地址指针,在所述计数寄存器的计数值为0时, 通过链接的地址指针变换以对X型结构路由器的链接状态进行切换。 优选的,所述在所述接口与所述子RAM之间设置多级链路传输结构,每一级所述链 路传输结构设置有多个X型结构路由器,包括: 在8并发RAM的链路结构中,设置三级链路传输结构,每一级链路传输结构包含4个 X型结构路由器; 第一级链路传输结构中的X型结构路由器的时钟周期为4,第二级链路传输结构中 的X型结构路由器的时钟周期为2,第三级链路传输结构的 X型结构路由器的时钟周期为1; 所述第一级链路传输结构的X型结构路由器与所述第二级链路传输结构的X型结 构路由器之间,及所述第二级链路传输结构的X型结构路由器与所述第三级链路传输结构 的X型结构路由器之间均设置有8个缓存寄存器,并与相应的X型结构路由器链接。 优选的,所述在所述接口与所述子RAM之间设置多级链路传输结构,每一级所述链 路传输结构设置有多个X型结构路由器,还包括: 在8并发RAM的链路结构中,在第一级链路传输结构中,4个X型结构路由器的工作 6 CN 111597138 A 说 明 书 3/9 页 状态按时钟周期的递减顺序或递增顺序设置; 在第二级链路传输结构中,将4个X型结构路由器分成两组,每一组的X型结构路由 器的工作状态按时钟周期的递减顺序或递增顺序设置; 在第三级链路传输结构中,将4个X型结构路由器的工作状态以计数值0表征。 本发明还提供一种X型链路结构的多并发RAM数据传输结构,包括: 子RAM层,用于通过多个物理独立的子RAM映射至少一个共享存储的多并发RAM; 接口层,用于获取基于共享存储的片上多核处理器的每个核所对应的接口; 链路传输结构层,用于在所述接口与所述子RAM之间设置多级链路传输结构,且每 一级所述链路传输结构设置有多个X型结构路由器,使每个所述接口通过所述X型路由器与 每个所述子RAM之间形成固定的传输路径,以对数据流进行发送或响应。 优选的,还包括: 所述X型结构路由器设置有两路输入和两路输出,以构成交叉链接状态或直接链 接状态,并按设定时钟周期进行状态切换; 地址时隙规则单元,用于通过对每个所述X型结构路由器的状态切换的时钟周期 和当前工作状态设置,使每个所述接口与每个所述子RAM链接的地址时隙均不相同,并形成 地址递增或地址递减的地址时隙规则; 链接切换则单元,用于按所述地址时隙规则对所述接口与所述子RAM 进行链接切 换,以实现数据交互的全并发RAM。 优选的,还包括: 存储区域设置单元,用于按地址递增或地址递减建立地址存储区域; 数据存储单元,用于获取所述接口的数据流,并将所述数据流传输到所述地址存 储区域进行存储; 重排序模块,用于判断所述数据流是否符合所述地址时隙规则,如果否,则对所述 数据流传输的地址时隙进行重新排序,进而根据排序后的地址时隙从所述地址时隙区域中 获取数据进行传送或响应。 优选的,所述X型结构路由器包括:时钟周期寄存器、计数寄存器和链接寄存器; 所述时钟周期寄存器,用于设置所述X型结构路由器的时钟周期; 所述计数寄存器,用于将当前时钟值设置为计数值,并对计数值进行递减计数,且 所述计数值表征所述X型结构路由器的当前工作状态,在计数值为0时,重新按所述时钟周 期作为计数值,以开始重新计递减计数; 所述链接寄存器,用于存储链接的地址指针,在所述计数寄存器的计数值为0时, 通过链接的地址指针变换以对X型结构路由器的链接状态进行切换。 优选的,链路传输结构层包括三级链路传输结构,每一级链路传输结构包含4个X 型结构路由器; 第一级链路传输结构中的X型结构路由器的时钟周期为4,第二级链路传输结构中 的X型结构路由器的时钟周期为2,第三级链路传输结构的 X型结构路由器的时钟周期为1; 所述第一级链路传输结构的X型结构路由器与所述第二级链路传输结构的X型结 构路由器之间,及所述第二级链路传输结构的X型结构路由器与所述第三级链路传输结构 的X型结构路由器之间均设置有8个缓存寄存器,并与相应的X型结构路由器链接。 7 CN 111597138 A 说 明 书 4/9 页 本发明提供一种X型链路结构的多并发RAM数据传输方法及结构,其互连网络的基 本结构是由按一定规律切换传输方向的X型结构路由器组成,并形成多级链路传输结构,使 X型结构路由器将接口与逻辑上完整的 RAM链接起来,解决现有多并发RAM电路面积过大且 仲裁电路过于复杂,造成布局布线困难的问题,相较于现有技术方案,该方案无需路由FIFO 和仲裁电路,因而硬件资源开销小,只有少量扇入扇出的x型路由器,简化布局布线并有效 提升电路主频。 附图说明 为了更清楚地说明本发明的具体实施例,下面将对实施例中所需要使用的附图作 简单地介绍。 图1是现有技术中基于全连接网络的多并发RAM结构示意图。 图2是本发明提供的一种X型链路结构的多并发RAM数据传输方法示意图; 图3是本发明提供的一种X型结构路由器的工作状态示意图; 图4是本发明实施例提供的基于X型结构路由器的8并发RAM结构示意图; 图5(a)~图5(f)是本发明实施例提供的数据流传输示意图; 图6是本发明实施例提供的重排序模块示意图。