技术摘要:

一种数字电路局部时钟网络SPICE网表的生成方法,包括以下步骤:1)从根节点到指定叶节点进行遍历,标记该路径上的节点为合法节点;2)回溯非指定叶节点至所述合法节点的子节点,并移除冗余节点;3)处理寄生参数信息,将与待移除节点的耦合电容转化为对地电容。本发明 全部

背景技术:

在数字电路设计中,时钟网络的时序质量如延时偏差、各个节点信号占空比等对 后期整个设计的时序收敛有很重要的影响。数字电路设计的后端流程首先对时钟树进行综 合,之后整体做布局布线进而进行时序优化和检查。时钟树综合阶段通常对逻辑门级数,总 的延时以及延时偏差进行约束,布局布线工具在设定的约束下完成时钟树的综合工作,然 后进行下一步的布局布线工作。但在时钟树综合阶段,一般来说不会使用STA(静态时序分 析)工具检查时序,因为数据路径上尚未完成布局布线以及只有部分寄生参数信息,所以仅 通过布局布线工具难以准确评估时钟网络的时序质量。 针对上述情况,使用SPICE进行仿真是一种比较合适的方案。在实际设计中,整个 芯片的时钟结构是极其复杂的,全部进行SPICE仿真并不现实。通常会选出来一部分时钟电 路结构进行仿真和分析。这部分电路可以是一个时钟的mesh结构或者一个树结构,其中不 包含复杂的逻辑单元如异或门和分频器件,但是可以有时钟门控单元、多路选择器和其它 时序逻辑可以确定的组合单元如与门,或门等。 通过设计网表(.v)的连接关系以及标准单元库文件中相应管脚的时序边关系可 以提取出具有时序传递关系的连接图, 再结合寄生参数信息文件产生出SPICE网表进行仿 真。

技术实现要素:

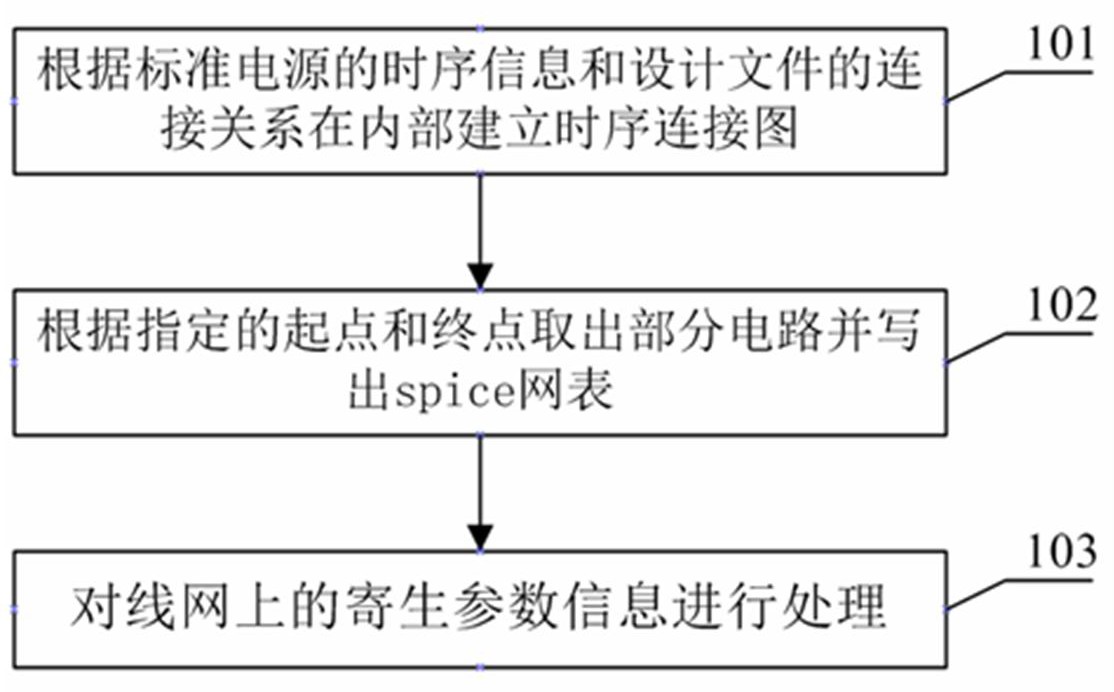

为了解决现有技术存在的不足,本发明的目的在于提供一种数字电路局部时钟网 络SPICE网表的生成方法,能够在仿真精度和仿真时间方面都有比较好的表现,极大地提高 了用来做SPICE仿真的可行性。 为实现上述目的,本发明提供的一种数字电路局部时钟网络SPICE网表的生成方 法,包括以下步骤: 1)从根节点到指定叶节点进行遍历,标记该路径上的节点为合法节点; 2)回溯非指定叶节点至所述合法节点的子节点,并移除冗余节点; 3)处理寄生参数信息,将移除节点的耦合电容转化为对地电容。 进一步地,在所述步骤1)之前,还包括, 读入设计文件,根据时序信息和所述设计文件的连接关系建立时序连接图; 深度遍历所述连接图得到所述根节点到所有叶节点的路径。 进一步地,所述设计文件包括网表.v,标准单元时序库文件.lib,寄生参数文件 .spef。 进一步地,所述步骤2)进一步包括,保留回溯过程中与所述合法节点相连接的一 3 CN 111553120 A 说 明 书 2/4 页 级冗余节点的信息。 更进一步地,包括,当电路中存在多路选择器或门控时钟单元时,将其控制管脚设 为正确的偏置值。 为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机程 序,所述计算机程序运行时执行如上文所述的数字电路局部时钟网络SPICE网表的生成方 法步骤。 为实现上述目的,本发明还提供一种数字电路局部时钟网络SPICE网表的生成设 备,包括存储器和处理器,所述存储器上储存有在所述处理器上运行的计算机程序,所述处 理器运行所述计算机程序时执行如上文所述的数字电路局部时钟网络SPICE网表的生成方 法步骤。 本发明的一种数字电路局部时钟网络SPICE网表的生成方法,具有以下有益效果: 1)将不在根节点到指定叶节点路径上的中间节点删除,保留分支节点后一级的负载信 息,能够在不损失精度的同时提高仿真效率。 2)在写线网上的寄生参数数据时,将不在该电路结构上的耦合电容转变为对地电 容,针对设计规模庞大的数字电路所产生的SPICE网表在仿真精度和仿真速度方面都有比 较好的表现,极大地提高了用来做SPICE仿真的可行性。 本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变 得显而易见,或者通过实施本发明而了解。 附图说明 附图用来提供对本发明的进一步理解,并且构成说明书的一部分,并与本发明的 实施例一起,用于解释本发明,并不构成对本发明的限制。在附图中: 图1为根据本发明的数字电路局部时钟网络SPICE网表的生成方法流程图; 图2为根据本发明的数字电路局部时钟网络SPICE网表的生成方法实施例一去除冗余 电路示意图; 图3为根据本发明的数字电路局部时钟网络SPICE网表的生成方法实施例一转化耦合 电容示意图。