技术摘要:

本发明提供一种阵列基板及其制备方法,所述阵列基板包括衬底基板、第一走线、第二走线以及第三走线和第四走线。本申请通过在第一走线朝向第二走线的一侧设置第一凹槽以及在第二走线朝向第一走线的一侧设置第二凹槽,且第一凹槽和第二凹槽相对设置,其中,第一凹槽和第 全部

背景技术:

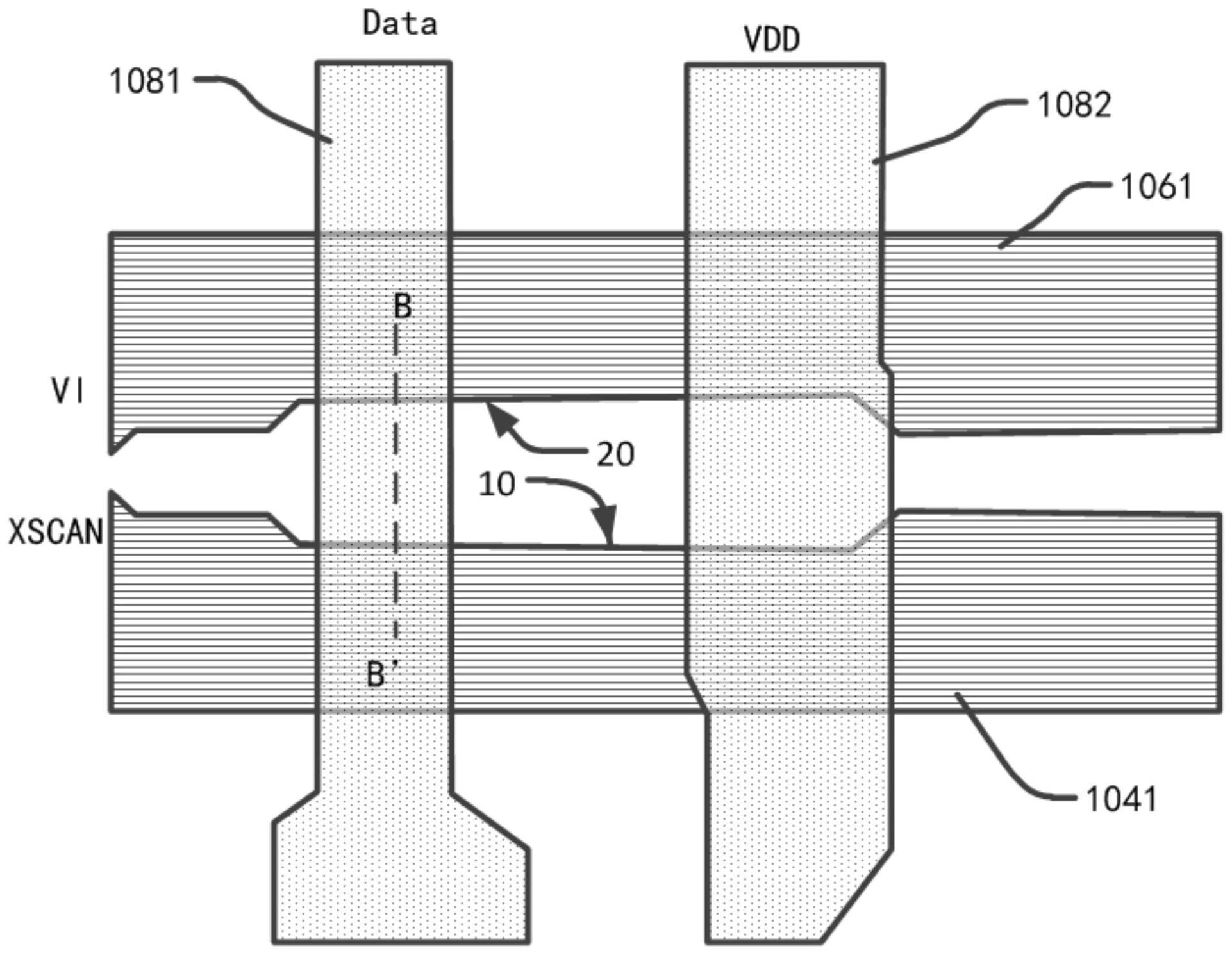

近年来,随着显示技术的进步,有机发光二极管(Organic Light Emitting Diode,OLED)显示器是当今平板显示器研究领域的热点之一,越来越多的有源矩阵有机发 光二极管(Active Matrix Organic Light Emitting Diode,AMOLED)显示面板进入市场, 相对于传统的薄膜晶体管液晶显示面板(Thin Film Transistor Liquid Crystal Display,TFTLCD),AMOLED具有更快的反应速度,更高的对比度以及更广大的视角。且随着 显示技术的发展,越来越多的电子设备中开始使用轻薄且抗冲击特性表现良好的可弯折柔 性OLED显示屏。 如图1和图2所示,阵列基板从下至上依次包括PI基板101、缓冲层102、第一绝缘层 103、第一金属层104、第二绝缘层105、第二金属层106、介电层107以及第三金属层108。其 中,第一金属层104图案化形成扫描线走线XSCAN,第二金属层106图案化形成复位线VI,第 三金属层108图案化形成数据线Data和电源电压线VDD。当像素尺寸较小或者为了增加像素 的透过率时,会使扫描线走线XSCAN和复位线VI的间距拉近。当Data和VDD在跨越XSCAN和VI 时存在金属的段差。因此,在制作Data和电源VDD时,由于凹陷在Data和VDD之间的光刻胶曝 光不充分,而导致data和VDD之间存在残留金属区域M,该残留金属区域M会导致data和VDD 发生短路,从而影响产品良率。

技术实现要素:

本发明的目的在于,提供一种阵列基板及其制备方法,以解决金属层在形成Data 和电源电压线VDD时,Data和VDD之间容易存在残留金属,该残留金属导致data和VDD发生短 路的技术问题。 为实现上述目的,本发明提供一种阵列基板,包括:衬底基板;第一走线,设于所述 衬底基板的一面;第二走线,设于所述第一走线上方且与所述第一走线相错且平行,在平行 于所述衬底基板表面方向,相错的所述第一走线和所述第二走线之间具有第一间距区;所 述第一走线朝向第二走线的一侧具有第一凹槽,所述第二走线朝向所述第一走线的一侧具 有第二凹槽,所述第一凹槽和第二凹槽相对设置;以及第三走线和第四走线,同层设置且相 互平行,并位于所述第二走线的上方;所述第三走线和所述第四走线之间具有一第二间距 区;所述第三走线和所述第四走线分别跨过所述第一走线和所述第二走线,且所述第二间 距区对应跨过所述第一凹槽和所述第二凹槽所在区域。 进一步地,所述第一凹槽和所述第二凹槽用以加宽所述第一间距区,当所述第一 间距区增大时,所述第二间距区随着所述第一间距区增大而增大,所述第三走线在所述衬 底基板上的投影和所述第四走线在所述衬底基板上的投影彼此分离。 进一步地,所述第一凹槽和第二凹槽的底壁呈锯齿状。 4 CN 111613624 A 说 明 书 2/6 页 进一步地,所述衬底基板包括:PI基板;缓冲层,设于所述PI基板上;以及第一绝缘 层,设于所述缓冲层上。 进一步地,所述第一走线设于所述第一绝缘层上; 第二绝缘层,设于所述第一绝缘层及所述第一走线上,所述第二绝缘层在所述第 一走线对应的位置具有一第一凸起; 所述第二走线设于所述第二绝缘层上,所述第二走线与所述第一凸起之间具有第 一沟槽; 介电层,设于所述第二绝缘层及所述第二走线上,所述介电层在所述第二走线对 应的位置具有第二凸起,所述介电层在所述第一凸起对应的位置具有第三凸起,所述第二 凸起与所述第三凸起之间具有第二沟槽,所述第二沟槽在所述第二绝缘层上的投影完全落 入所述第一沟槽内; 所述第三走线和所述第四走线设于所述介电层上,所述第三走线或所述第四走线 在所述第二凸起对应的位置具有第四凸起,所述第三走线或所述第四走线在所述第三凸起 对应的位置具有第五凸起,所述第四凸起与所述第五凸起之间具有第三沟槽,所述第三沟 槽在所述介电层上的投影完全落入所述第二沟槽内。 进一步地,当加宽所述第二沟槽的宽度时,所述第一走线与所述第二走线的第一 间距区的间距增大,并使得沉积金属材料形成所述第三走线与所述第四走线时,无金属材 料残留在所述第三沟槽内。 为实现上述目的,本发明还提供一种阵列基板的制备方法,包括如下步骤:形成一 衬底基板;形成第一走线于所述衬底基板的一面;形成第二走线于所述第一走线上方且与 所述第一走线相错且平行,在平行于所述衬底基板表面方向,相错的所述第一走线和所述 第二走线之间具有第一间距区;所述第一走线朝向第二走线的一侧具有第一凹槽,所述第 二走线朝向所述第一走线的一侧具有第二凹槽,所述第一凹槽和第二凹槽相对设置;以及 形成第三走线和第四走线于所述第二走线的上方,所述第三走线和所述第四走线同层设置 且相互平行,所述第三走线和所述第四走线之间具有一第二间距区;其中,所述第三走线和 所述第四走线分别跨过所述第一走线和所述第二走线,且所述第二间距区对应跨过所述第 一凹槽和所述第二凹槽所在区域。 进一步地,所述第一凹槽和第二凹槽的底壁呈锯齿状。 进一步地,所述形成一衬底基板的步骤具体包括:提供一PI基板;形成一缓冲层于 所述PI基板上;以及形成一第一绝缘层于所述缓冲层上。 进一步地,所述形成一衬底基板的步骤之后,具体包括: 在所述衬底基板的上表面沉积金属材料形成所述第一走线; 形成一第二绝缘层于所述第一绝缘层及所述第一走线上,所述第二绝缘层在所述 第一走线对应的位置具有一第一凸起; 在所述第二绝缘层上表面沉积金属材料形成所述第二走线,所述第二走线与所述 第一凸起之间具有第一沟槽; 形成一介电层于所述第二绝缘层及所述第二走线上,所述介电层在所述第二走线 对应的位置具有第二凸起,所述介电层在所述第一凸起对应的位置具有第三凸起,所述第 二凸起与所述第三凸起之间具有第二沟槽,所述第二沟槽在所述第二绝缘层上的投影完全 5 CN 111613624 A 说 明 书 3/6 页 落入所述第一沟槽内; 在所述介电层上表面沉积金属材料形成所述第三走线和所述第四走线,所述第三 走线或所述第四走线在所述第二凸起对应的位置具有第四凸起,所述第三走线或所述第四 走线在所述第三凸起对应的位置具有第五凸起,所述第四凸起与所述第五凸起之间具有第 三沟槽,所述第三沟槽在所述介电层上的投影完全落入所述第二沟槽内。 本发明的技术效果在于,提供一种阵列基板及其制备方法,通过在第一走线朝向 第二走线的一侧设置第一凹槽以及在第二走线朝向第一走线的一侧设置第二凹槽,且第一 凹槽和第二凹槽相对设置,其中,第一凹槽和第二凹槽用以加宽第一走线和第二走线之间 的间距区。当第三走线和第四走线分别跨过第一走线和第二走线时,第三走线和第四走线 之间的间距区对应跨过第一凹槽和第二凹槽所在区域,使得第三走线和第四走线彼此分离 互不连接,且不会发生短路,提高阵列基板的良率。 附图说明 下面结合附图,通过对本申请的