技术摘要:

包括桥接管芯的系统级封装。一种系统级封装包括再分配线RDL结构、第一半导体芯片、第二半导体芯片、第二子封装、第一桥接管芯和第二桥接管芯。该RDL结构包括第一RDL图案,第一半导体芯片的第一芯片焊盘电连接至第一RDL图案。第二半导体芯片层叠在第一半导体芯片上,使 全部

背景技术:

近来,大量努力集中在将多个半导体芯片集成到单个半导体封装中。即,已尝试增 加封装集成密度以实现利用多功能操作高速处理大量数据的高性能半导体封装。例如,系 统级封装(SiP)技术可被视为实现高性能半导体封装的有吸引力的候选。包括在各个SiP中 的多个半导体芯片并排设置。然而,这可导致难以减小SiP的宽度。因此,已提出将多个半导 体芯片设置在SiP封装中的各种技术以减小SiP的尺寸。

技术实现要素:

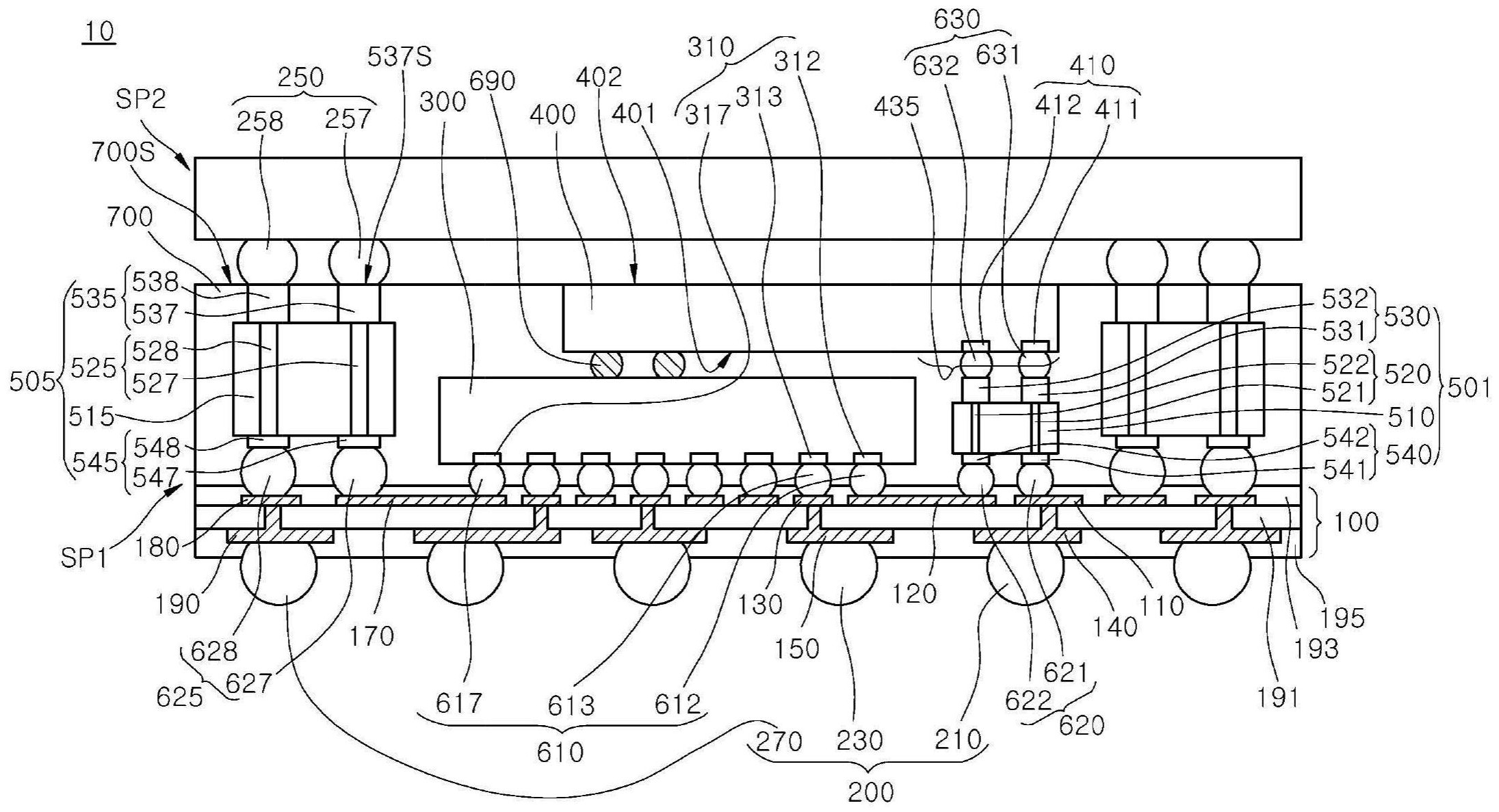

根据实施方式,一种系统级封装包括第一子封装以及安装在第一子封装上的第二 子封装。第一子封装包括再分配线(RDL)结构,该RDL结构具有第一RDL图案和第二RDL图案。 第一子封装还包括第一半导体芯片,该第一半导体芯片设置在RDL结构上,使得第一半导体 芯片的电连接到第一RDL图案的第一芯片焊盘面向RDL结构。第一子封装还包括第二半导体 芯片,该第二半导体芯片层叠在第一半导体芯片上,使得第二半导体芯片突出越过第一半 导体芯片的侧表面,其中,设置在第二半导体芯片的突起上的第二芯片焊盘面向RDL结构。 第一子封装另外包括第一桥接管芯,该第一桥接管芯设置在RDL结构上以支撑第二半导体 芯片的突起,其中,第一桥接管芯包括由第一通孔穿透的第一主体,其中,第一通孔将第二 芯片焊盘电连接到第一RDL图案。第一子封装还包括第二桥接管芯,该第二桥接管芯设置在 RDL结构上并且与第一半导体芯片间隔开,其中,该第二桥接管芯包括由第二通孔穿透的第 二主体,其中,第二通孔将第二子封装电连接到第二RDL图案。第一子封装还包括模制层,该 模制层设置在RDL结构上以覆盖第一半导体芯片和第一桥接管芯并且围绕第二半导体芯片 和第二桥接管芯。 根据另一实施方式,一种系统级封装包括第一子封装以及安装在第一子封装上的 第二子封装。第一子封装包括再分配线(RDL)结构,该RDL结构包括第一RDL图案和第二RDL 图案。第一子封装还包括第一半导体芯片,该第一半导体芯片设置在RDL结构上,使得第一 半导体芯片的电连接到第一RDL图案的第一芯片焊盘面向RDL结构。第一子封装还包括第二 半导体芯片,该第二半导体芯片层叠在第一半导体芯片上,使得第二半导体芯片突出越过 第一半导体芯片的侧表面,其中,设置在第二半导体芯片的突起上的第二芯片焊盘面向RDL 结构。第一子封装另外包括第一桥接管芯,该第一桥接管芯设置在RDL结构上以支撑第二半 导体芯片的突起,其中,该第一桥接管芯包括由第一通孔穿透的第一模制材料基板,其中, 第一通孔将第二芯片焊盘电连接到第一RDL图案。第一子封装还包括第二桥接管芯,该第二 桥接管芯设置在RDL结构上并且与第一半导体芯片间隔开,其中,该第二桥接管芯包括由第 二通孔穿透的第二模制材料基板,其中,第二通孔将第二子封装电连接到第二RDL图案。第 一子封装还包括模制层,该模制层设置在RDL结构上以覆盖第一半导体芯片和第一桥接管 5 CN 111613605 A 说 明 书 2/13 页 芯并且围绕第二半导体芯片和第二桥接管芯。 附图说明 图1是示出根据实施方式的系统级封装(SiP)的横截面图。 图2是示出图1的一部分(包括第一桥接管芯)的放大横截面图。 图3是示出将图2所示的半导体芯片彼此连接的电路径的立体图。 图4是示出图1的一部分(包括第二桥接管芯)的放大横截面图。 图5是示出图1的一部分(包括第一桥接管芯和第二桥接管芯)的放大横截面图。 图6是示出图5所示的第一桥接管芯和第二桥接管芯的柱状凸块的平面图。 图7是示出图1所示的半导体芯片之间的连接部分的放大横截面图。 图8是示出根据另一实施方式的SiP的横截面图。 图9是示出根据另一实施方式的SiP的横截面图。 图10是示出采用包括根据实施方式的至少一个SiP的存储卡的电子系统的框图。 图11是示出包括根据实施方式的至少一个SiP的另一电子系统的框图。