技术摘要:

提供了一种图像传感器的脉冲发生器,所述脉冲发生器包括延迟单元,其中,所述延迟单元包括:串联地布置在电源电压与接地电压之间的多个晶体管、稳定电容器和稳定开关。所述电源电压被提供给所述多个晶体管之中的设置在首位的第一晶体管的第一端,并且所述第一晶体管的 全部

背景技术:

图像传感器是检测并传送用于生成图像的信息的传感器。图像传感器可以包括多 个像素、模数转换器(ADC)和计数器。当图像传感器包括大量的像素时,ADC需要以高速进行 操作。随着ADC以更高的速度进行操作,计数器的频率增加,并且图像传感器的功耗与计数 器的频率成比例地增加。脉冲发生器方法可以用于在计数器的计数周期期间降低图像传感 器的功耗。然而,在典型的脉冲发生器方法中,由于在电源电压的值改变时由该方法生成的 脉冲的宽度变化,因此会生成过多的噪声。

技术实现要素:

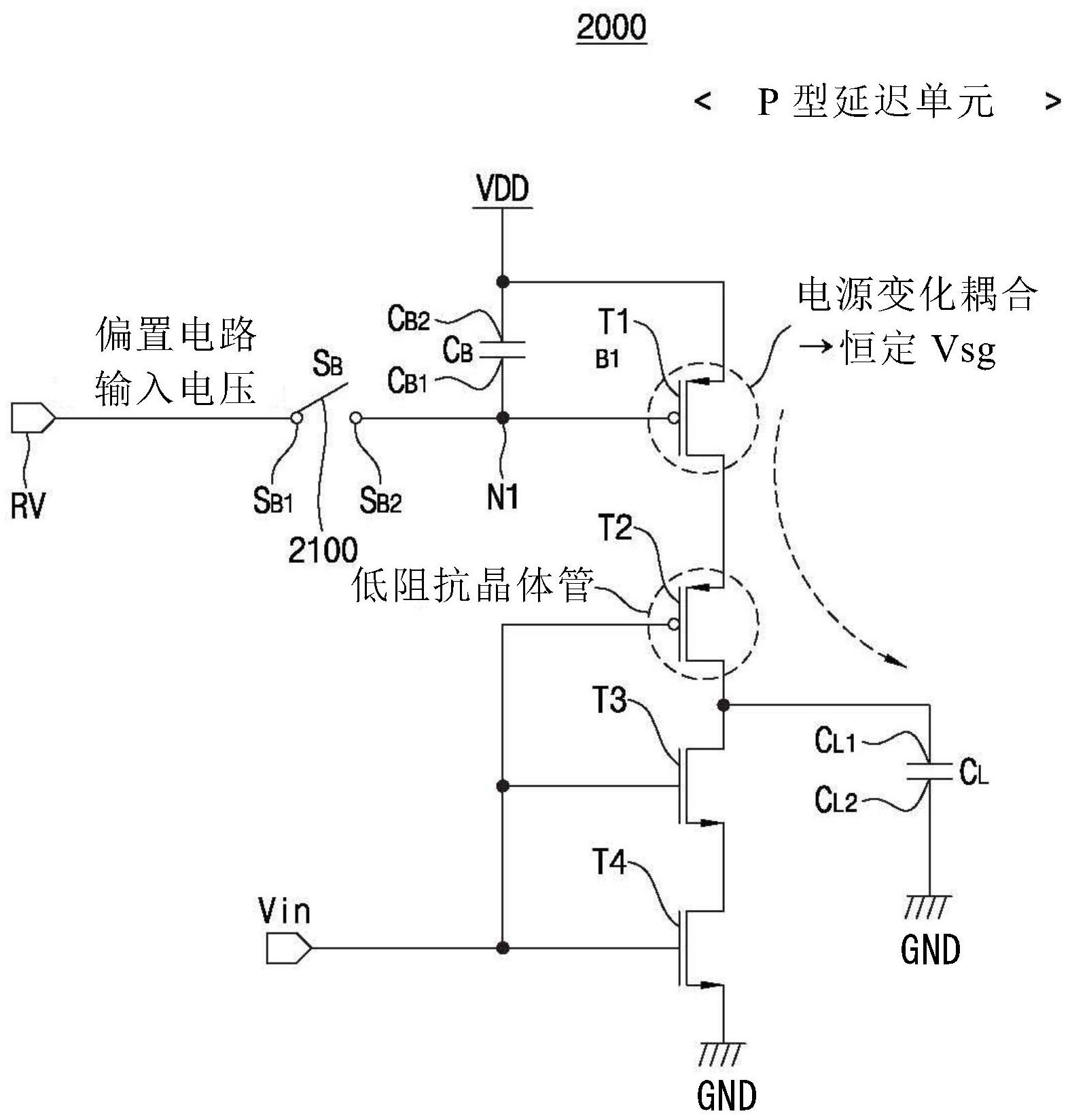

本发明构思的至少一个实施例旨在提供一种用于图像传感器的脉冲发生器及其 驱动方法,其中,所述脉冲发生器在考虑电源纹波抑制(PSRR)特性的情况下不受电源状态 的变化的影响。 此外,本发明构思的至少一个实施例旨在提供一种不受可能由电源电压的变化生 成的水平噪声、随机噪声、列固定模式噪声和码线性误差(code linearity error)影响的 延迟单元,并且提供包括该延迟单元的用于图像传感器的脉冲发生器及其驱动方法。 根据本发明构思的示例性实施例的图像传感器的脉冲发生器包括延迟单元,所述 延迟单元包括串联地布置在电源电压与接地电压之间的多个晶体管、稳定电容器和稳定开 关。所述电源电压被提供给所述多个晶体管之中的设置在首位的第一晶体管的第一端,并 且所述第一晶体管的栅极端连接到第一节点。输入电压被提供给所述多个晶体管之中的设 置在末位的第n晶体管的栅极端,并且所述接地电压被提供给所述第n晶体管的第一端。所 述稳定电容器连接在所述第一晶体管的所述第一端与所述第一节点之间。所述稳定开关设 置在提供参考电压的参考电压输入端与所述第一节点之间。所述稳定开关被输入的偏置控 制信号接通,以将所述参考电压提供给所述第一节点。所述图像传感器的所述脉冲发生器 可以基于从比较器输入的比较信号的转变,将脉冲信号输出给计数器。 根据本发明构思的示例性实施例的图像传感器的脉冲发生器包括延迟单元,所述 延迟单元包括串联地布置在电源电压与接地电压之间的多个晶体管、稳定电容器和稳定开 关。所述电源电压被提供给所述多个晶体管之中的设置在首位的第一晶体管的第一端,并 5 CN 111556258 A 说 明 书 2/19 页 且输入电压被提供给所述第一晶体管的栅极端。所述接地电压被提供给所述多个晶体管之 中的设置在末位的第n晶体管的第一端,并且所述第n晶体管的栅极端连接到第一节点。所 述稳定电容器连接在所述第n晶体管的所述第一端与所述第一节点之间。所述稳定开关设 置在提供参考电压的参考电压输入端与所述第一节点之间。所述稳定开关被输入的偏置控 制信号接通,以将所述参考电压提供给所述第一节点。所述图像传感器的所述脉冲发生器 可以基于从比较器输入的比较信号的转变,将脉冲信号输出给计数器。 根据本发明构思的示例性实施例的图像传感器的脉冲发生器包括延迟单元,所述 延迟单元包括串联地布置在电源电压与接地电压之间的多个晶体管、第一稳定电容器、第 二稳定电容器、第一稳定开关和第二稳定开关。所述电源电压被提供给所述多个晶体管之 中的设置在首位的第一晶体管的第一端,并且所述第一晶体管的栅极端连接到第一节点。 所述接地电压被提供给所述多个晶体管之中的设置在末位的第n晶体管的第一端,并且所 述第n晶体管的栅极端连接到第二节点。所述第一稳定电容器连接在所述第一晶体管的所 述第一端与所述第一节点之间。所述第一稳定开关设置在提供第一参考电压的第一参考电 压输入端与所述第一节点之间。所述第一稳定开关被输入的偏置控制信号接通,以将所述 第一参考电压提供给所述第一节点。所述第二稳定电容器连接在所述第n晶体管的所述第 一端与所述第二节点之间。所述第二稳定开关设置在提供第二参考电压的第二参考电压输 入端与所述第二节点之间。所述第二稳定开关被所述输入的偏置控制信号接通,以将所述 第二参考电压提供给所述第二节点。所述图像传感器的所述脉冲发生器可以基于从比较器 输入的比较信号的转变,将脉冲信号输出给计数器。 根据本发明构思的示例性实施例的图像传感器的脉冲发生器包括延迟单元,所述 延迟单元包括串联地布置在电源电压与接地电压之间的多个晶体管以及连接到第一晶体 管的栅极端的偏置电路。所述电源电压被提供给所述多个晶体管之中的设置在首位的第一 晶体管的第一端,并且所述第一晶体管的栅极端连接到第一节点。输入电压被提供给所述 多个晶体管之中的设置在末位的第n晶体管的栅极端,并且所述接地电压被提供给所述第n 晶体管的第一端。所述偏置电路包括偏置晶体管和运算放大器(op-amp)。所述偏置晶体管 包括被提供电源电压的第一端、连接到接地的第二端以及连接到所述第一晶体管的栅极 端。所述op-amp包括连接到所述偏置晶体管的所述第二端的正端和被施加参考电压的负 端。所述图像传感器的所述脉冲发生器可以恒定地保持所述第一晶体管的源极端和栅极端 之间的电压。 根据本发明构思的示例性实施例的图像传感器的脉冲发生器包括延迟单元,所述 延迟单元包括串联地布置在电源电压与接地电压之间的多个晶体管以及连接到第n晶体管 的栅极端的偏置电路。所述电源电压被提供给所述多个晶体管之中的设置在首位的第一晶 体管的第一端,并且输入电压被提供给所述第一晶体管的栅极端。所述接地电压被提供给 所述多个晶体管之中的设置在末位的第n晶体管的第一端,并且所述第n晶体管的栅极端连 接到第一节点。所述偏置电路包括偏置晶体管和运算放大器(op-amp)。所述偏置晶体管包 括被提供电源电压的第一端、连接到接地的第二端以及连接到所述第n晶体管的栅极端。所 述op-amp包括连接到所述偏置晶体管的所述第一端的正端和被施加参考电压的负端。所述 图像传感器的所述脉冲发生器可以恒定地保持所述第n晶体管的源极端和栅极端之间的电 压。 6 CN 111556258 A 说 明 书 3/19 页 根据本发明构思的示例性实施例的图像传感器的脉冲发生器包括延迟单元,所述 延迟单元包括串联地布置在电源电压与接地电压之间的多个晶体管、连接到第一晶体管的 栅极端的第一偏置电路以及连接到第n晶体管的栅极端的偏置电路。所述电源电压被提供 给所述多个晶体管之中的设置在首位的第一晶体管的第一端,并且所述第一晶体管的栅极 端连接到第一节点。所述接地电压被提供给所述多个晶体管之中的设置在末位的所述第n 晶体管的第一端,并且所述第n晶体管的栅极端连接到第二节点。所述第一偏置电路包括第 一偏置晶体管和第一运算放大器(op-amp)。所述第一偏置晶体管包括被提供电源电压的第 一端、被提供接地电压的第二端以及连接到所述第一op-amp的输出端和所述第一晶体管的 栅极端的栅极端。所述第一op-amp包括连接到所述第一偏置晶体管的第二端的正端和被施 加参考电压的负端。所述第二偏置电路包括第二偏置晶体管和第二op-amp。所述第二偏置 晶体管包括被提供电源电压的第一端、被提供接地电压的第二端以及连接到所述第二op- amp的输出端和所述第n晶体管的栅极端的栅极端。所述第二op-amp包括连接到所述第二偏 置晶体管的第一端的正端和被施加参考电压的负端。所述图像传感器的所述脉冲发生器可 以恒定地保持所述第一晶体管的源极端和栅极端之间的电压以及所述第n晶体管的源极端 和栅极端之间的电压。 附图说明 通过以下结合附图的详细描述,将更清楚地理解本公开的示例性实施例。 图1是根据本发明构思的示例性实施例的包括图像传感器的图像处理系统的框 图。 图2是示出图1中所示的图像传感器的视图。 图3是示出图1中所示的像素阵列和读出电路的视图。 图4是示出图3中所示的ADC块的视图。 图5是示出图4中所示的脉冲发生器的视图。 图6是示出具有基于相关双采样电路(CDS)的输出转变发生的时间而生成的延迟 的信号的视图。 图7A示出根据本发明构思的示例性实施例的延迟单元,并且图7A是示出P型延迟 单元的视图。 图7B示出根据本发明构思的示例性实施例的延迟单元,并且图7B是示出P型延迟 单元的视图。 图7C示出根据本发明构思的示例性实施例的延迟单元,并且图7C是示出P型延迟 单元的视图。 图8A是示出在执行双CDS的ADC的操作时序中脉冲发生器的驱动方法的视图。 图8B是示出脉冲发生器的输出脉冲的视图。 图9A示出根据本发明构思的示例性实施例的延迟单元,并且图9A是示出N型延迟 单元的视图。 图9B示出根据本发明构思的示例性实施例的延迟单元,并且图9B是示出N型延迟 单元的视图。 图9C示出根据本发明构思的示例性实施例的延迟单元,并且图9C是示出N型延迟 7 CN 111556258 A 说 明 书 4/19 页 单元的视图。 图10示出根据本发明构思的示例性实施例的延迟单元,并且图10是示出P-N型延 迟单元的视图。 图11A至图11D是示出根据本发明构思的示例性实施例的多级延迟单元的视图。 图12示出根据本发明构思的示例性实施例的延迟单元,并且图12是示出P型延迟 单元的视图。 图13示出根据本发明构思的示例性实施例的延迟单元,并且图13是示出N型延迟 单元的视图。 图14示出根据本发明构思的示例性实施例的延迟单元,并且图14是示出P-N型延 迟单元的视图。