技术摘要:

本发明描述与确定由三个或多于三个阵列存储的数据值之间的匹配有关的设备、系统及方法。使用所述数据值的系统可基于所述数据值是否匹配来管理功能的执行,包含对防止产品损坏、人员安全及/或可靠操作至关重要的自动功能。例如,本文中所描述的一种设备包含形成在单个存 全部

背景技术:

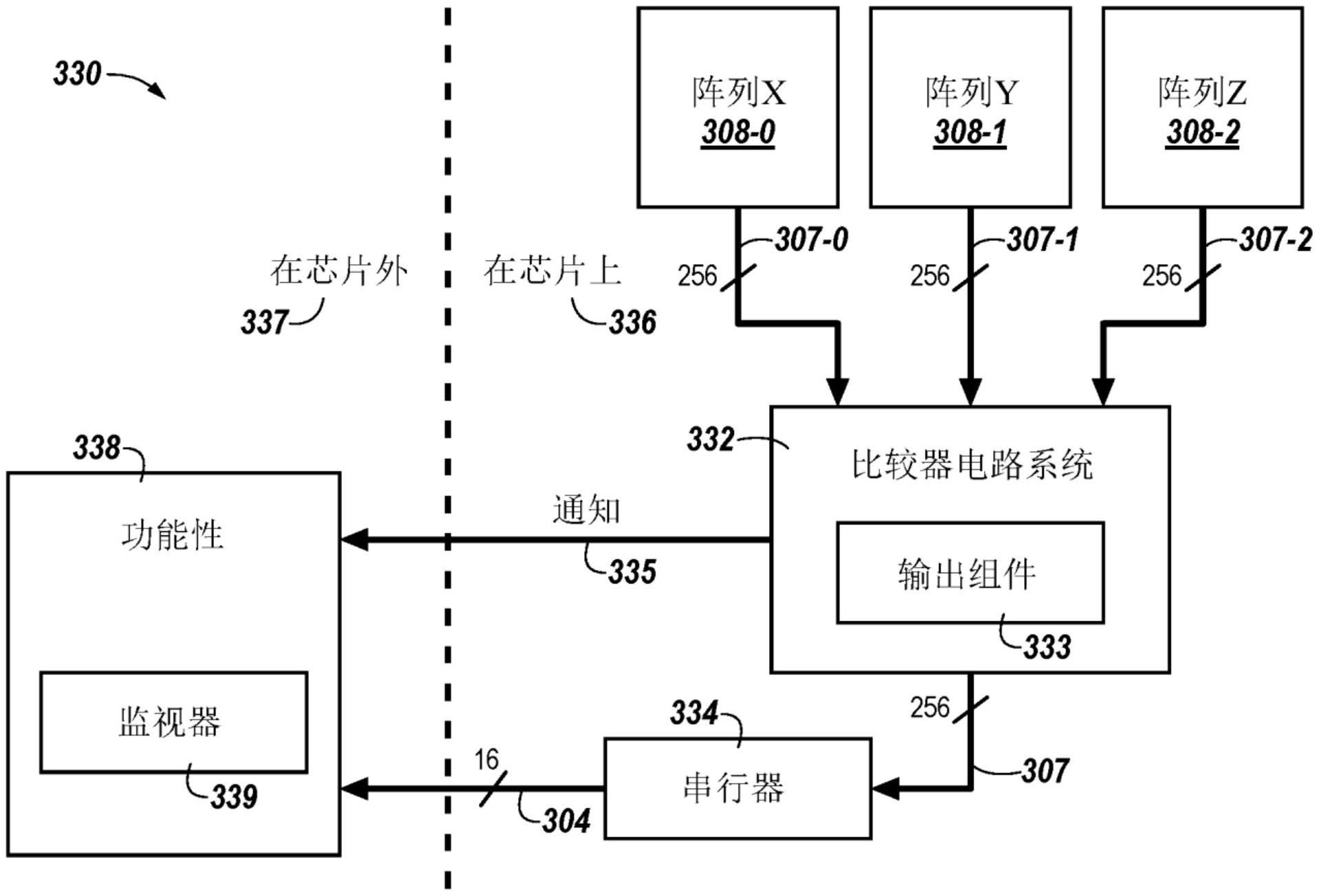

存储器装置通常经提供作为计算机或其它电子系统中的内部半导体集成电路。存 在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器可能需要电力来 维持其数据(例如,主机数据、错误数据等)。易失性存储器可包含随机存取存储器(RAM)、动 态随机存取存储器(DRAM)、静态随机存储器(SRAM)、同步动态随机存取存储器(SDRAM)及晶 闸管随机存取存储器(TRAM)以及其它类型。非易失性存储器可通过在未通电时保留所存储 数据来提供持久数据。非易失性存储器可包含NAND快闪存储器、NOR快闪存储器及例如相变 随机存取存储器(PCRAM)及电阻随机存取存储器(RRAM)的电阻可变存储器,以及例如自旋 转矩转移随机存取存储器(STT RAM)的磁阻式随机存取存储器(MRAM),以及其它类型。 电子系统通常包含多个处理资源(例如,一或多个处理器),其可从合适的位置检 索指令并执行指令及/或将所执行指令的结果存储到合适的位置(例如,易失性及/或非易 失性存储器)。处理器可包含多个功能单元,例如算术逻辑单元(ALU)电路系统、浮点单元 (FPU)电路系统及组合逻辑块,例如所述功能单元可用于通过对数据(例如,一或多个操作 数)执行例如“与”、“或”、“非”、“与非”、“或非”及“异或”的逻辑运算及反(例如,“非”)逻辑 运算来执行指令。例如,功能单元电路系统可用于经由多个运算对操作数执行算术运算,例 如加、减、乘以及除。 在许多情况下,处理资源可在存储器装置外部(例如,包含多个存储器阵列),且可 经由处理资源与存储器阵列之间的总线来存取数据以执行一组指令。然而,指令中数据值 的存储及/或存取以及此类数据值从存储体到存储器装置外部处理器的移动中的一或多个 错误可能会影响指令是否可如预期执行用于由外部处理资料执行操作。 附图说明 图1A及1B为说明根据本发明的多个实施例的在至少三个阵列上冗余地存储单个 数据文件的实例的示意图。 图2为根据本发明的多个实施例的在存储器装置的部分上的存储器单元阵列的实 例的框图。 图3为根据本发明的多个实施例说明用于比较由三个阵列存储的数据值的电路系 统的实例的示意图。 图4为根据本发明的多个实施例说明比较器组件的实例的示意图。 图5为根据本发明的多个实施例说明选择性耦合到比较器电路系统的三个阵列的 实例的示意图。 图6为根据本发明的多个实施例的用于确定由三个阵列存储的数据值之间是否存 5 CN 111587422 A 说 明 书 2/12 页 在匹配的逻辑的实例。 图7为根据本发明的多个实施例的用于选择一个阵列用于输出匹配数据值的逻辑 的实例。 图8为根据本发明的多个实施例的用于确定由三个阵列存储的数据值之间的匹配 的流程图。

技术实现要素:

本发明包含与确定由多个阵列存储的数据值之间的匹配相关联的系统、设备及方 法。在多个实施例中,设备包含形成在单个存储器芯片上的多个存储器单元阵列。所述设备 进一步包含比较器电路系统,所述比较器电路系统经配置以比较由选自多个阵列的三个阵 列存储的数据值,以确定在由三个阵列存储的数据值之间是否存在匹配。所述设备进一步 包含比较器电路系统的输出组件,所述比较器电路系统的输出组件经配置以响应于确定由 三个阵列中的两个阵列存储的数据值之间的匹配而输出所述两个阵列中的一个的数据值。 形成在单个存储器芯片(例如,在芯片上)在本文中旨在表示与存储器阵列(例如, 如在108处所展示且结合图1A及1B且在本文中别处所描述的“阵列”)形成(例如,定位)在同 一芯片上。如本文中所使用的阵列为通用术语,意在包含图2中所展示并结合图2所描述的 存储体组213、存储体214及/或存储体段216(例如,以DRAM配置,尽管存储器阵列不限于 DRAM配置)。在多个实施例中,存储体段216可与DRAM存储器阵列及/或存储体的“子阵列”相 对应。 相比之下,形成在不同芯片上(例如,在芯片外)在本文中旨在表示形成(例如,定 位)在与执行从芯片上接收(例如,发送)的指令(例如,按数据值顺序编码)相关联的芯片上 以通过外部处理资源(例如,如在338处所展示且结合图3且在本文中别处所描述的功能性) 执行操作。监视器组件(例如,如在339处所展示且结合图3且在本文中别处所描述)也可形 成在芯片外(例如,耦合到至少一个功能性338或作为其一部分)以接收确定由三个阵列存 储的指令的数据值之间无匹配的通知。 基于执行由存储器阵列存储及从存储器阵列存取的数据值(指令)的顺序的功能 的执行可能为许多自动化系统的整体部分。使用所述数据值的系统可基于所述数据值是否 匹配来管理功能的执行,包含对防止产品损坏、人员安全及/或可靠操作至关重要的自动功 能。对于对包含此类自动化系统(例如,自主运载工具,例如汽车、火车、飞机、火箭、空间站 等及许多其它可能性)的产品的损坏的预防,及/或使用此类自动化系统及/或在此类自动 化系统的人员(例如,自主运载工具的乘客、自行车手、行人、观察者等,及许多其它可能性) 的安全性,恰当执行有助于自动化系统的功能可为关键的。 因此,在此类实施方案中使用的自动化系统可能会受益于欲经执行以用于执行有 助于自动化系统的功能的所存储数据值中较低的错误率(例如,相对于被认为对其它实用 工具(例如,蜂窝电话、智能手机、个人计算机等)可接受的错误率)。因此,由三个阵列冗余 存储的数据值(指令)之间的匹配的确定及/或无本文中所描述的任何此类匹配的通知可增 强对包含此类自动化系统的产品的损坏的预防及/或使用此类自动化系统及/或在此类自 动化系统附近的人员的安全性。 本文中的诸图遵循编号惯例,其中参考编号的第一个数字或前几个数字与图编号 6 CN 111587422 A 说 明 书 3/12 页 相对应,而其余数字标识图中的元件或组件。可通过使用类似的数字来识别不同图之间的 类似元件或组件。例如,108可在图1A中指代元件“08”,且类似元件可在图3中被称为308。 图1A及1B为说明根据本发明的多个实施例的在至少三个阵列上冗余地存储单个 数据文件的实例的示意图100。三个存储器单元阵列由在108-0处的阵列X,在108-1处的阵 列Y及在108-2处的阵列Z表示,尽管在多个实施例中单个数据集或文件102可存储在多于三 个阵列中,且可从中选择三个阵列进行比较数据值,如本文中所描述。单个数据文件102可 为或可包含多个数据值,所述多个数据值经编码为待执行以用于执行操作(例如,制动、加 速、转弯等,以控制自主运载工具前进到达预期目的地,及许多其它可能性)的指令。本文中 所提及的单个数据文件102也或替代地可被称为数据、数据集等。在各种情况下,数据还可 包含控制信息或可执行指令。 可以使用k位数据总线104从例如主机(未展示)接收单个数据文件102,其中k可表 示一次(例如,在计算机的一个循环中)待接收的单个数据文件102中的数据值(位)的数目。 在多个实施例中,由k位数据总线104接收的数据值的数目可为16,如图1A及1B中所展示的 实例中,但实施例不限于16位数据总线。 可使用耦合到k位数据总线的解串器105将k位数据解串为数目(n)个部分。可经由 kn位数据总线107将k位数据的n个部分移动(例如,电子传输)到三个阵列中的至少一个(例 如,到阵列108-0、阵列108-1及/或或阵列108-2)。在多个实施例中,经由kn位数据总线107 移动的数据值的数目可为256(=16×16),如在图1A及1B中所展示的实例中,但实施例不限 于256位数据总线。k位数据的n个部分可作为单个数据文件102冗余存储在三个阵列上。 如在图1A中所展示,在一些实施例中,单个数据文件102可经由三组数据线(例如, kn位数据总线107-0、107-1及107-2)冗余地并行存储在三个阵列上,所述三组数据线分别 耦合到三个单独阵列(例如,分别为阵列108-0、阵列108-1及阵列108-2)。kn位数据总线 107-0、107-1及107-2各自可为将冗余的单个数据文件(例如,重复的数据值)移动到三个单 独阵列108-0、108-1及108-2中的每一者的多个物理数据线。 如在图1B中所展示,在一些实施例中,单个数据文件102可经由耦合到第一阵列的 一组数据线107存储在三个阵列中的第一阵列(例如,阵列108-0)上。可对存储在第一阵列 108-0上的单个数据文件执行拷贝功能109,以将单个数据文件102冗余地存储在三个阵列 中的第二阵列108-1及第三阵列108-2上。 图2为根据本发明的多个实施例的在存储器装置210的部分上的存储器单元阵列 的实例的框图。如本文中所述,可在单个存储器芯片上形成多个存储器单元阵列。图2中所 展示的存储器装置210的部分可形成(例如,包含)在单个存储器芯片上(例如,可在芯片 上)。在多个实施例中,在芯片上还旨在表示与控制器211及/或与耦合到多个阵列的感测电 路系统212形成在同一芯片上。 控制器211(例如,存储体控制逻辑及定序器)可包含呈硬件、固件或软件或其组合 形式的控制电路系统。作为实例,控制器211可包含状态机、定序器及/或一些其它类型的控 制电路系统,其可以耦合到印刷电路板的专用集成电路(ASIC)的形式来实施。在多个实施 例中,控制器211可与主机(未展示)共置(例如,呈单片系统(SOC)配置)。 主机及/或专用组件可包含多个处理资源(例如,一或多个处理器、微处理器,或某 一其它类型的控制电路系统),所述处理资源在存储器装置210形成在其上的芯片外部(在 7 CN 111587422 A 说 明 书 4/12 页 芯片外)。外部处理资源可能够(例如,经由控制器211)存取存储器装置210以对从存储器装 置210移动的数据值执行操作。至少一些操作可由与主机及/或专用组件相关联的各种功能 性(例如,如在338处所展示的功能性以及结合图3及在本文别处所描述的功能)来执行。在 多个实施例中,控制器211还可包含用于执行处理操作的多个处理资源。控制器211可对指 令(例如,与执行经编码在单个数据文件中的指令相关联的命令)及数据的整个块执行地址 解析,并指示(例如,控制)将数据及命令分配及存储到阵列中的分配位置(例如,存储体组 213、存储体214及/或存储体段216)中及/或到外部目的地的。 感测电路系统212可经配置以感测由阵列存储的数据值(例如,通过选择性地耦合 到阵列中的存储器单元的特定行)。所感测的数据值可供由比较器电路系统存取(例如,如 在332处所展示且结合图3及本文中别处所描述),所述比较器电路系统经配置以将由至少 三个阵列存储的单个数据文件102的数据值进行比较以确定由指示三个阵列中的多个阵列 存储的数据值之间是否存在匹配。所述匹配可在由三个阵列中的两个阵列存储的数据值之 间,其中数据值经冗余地存储,但可对四个阵列中的三个,五个阵列中的三个及/或六个阵 列中的五个等之间的匹配进行比较。给定由至少一个阵列存储的单个数据文件102的数据 值中的错误的可能性,且如果数据值由具有数据错误的阵列及仅一个其它阵列存储,那么 可确定无匹配,当数据值由至少三个阵列存储时,确定阵列之间匹配的概率增加。 控制器211可经配置以接收(例如,来自主机及/或功能性338)对所存储的单个数 据文件102的请求。在多个实施例中,控制器211可经配置以指示比较器电路系统332存取由 至少三个阵列存储的数据值,以确定多个阵列中是否存在匹配。 在多个实施例中,在芯片上也可旨在表示与比较器电路系统332形成在同一芯片 上,所述比较器电路系统可包含输出组件(例如,如在333处展示并结合图3及本文中别处所 描述)。在多个实施例中,在芯片上也可旨在表示连同相关联数据线(例如,总线104及107) 与解串器105及/或串行器(例如,如334处所展示且结合图3及本文中别处所描述)形成在同 一芯片上。 可以各种方式实施与存储装置210一起形成在芯片上且通过至少三个阵列在其上 冗余地存储单个数据文件102的多个阵列108。在多个实施例中,至少三个阵列可各自与形 成在芯片上的不同存储体组(例如,存储体组213-0、213-1、213-2及213-N,但不同存储体组 的数目不限于四个)相对应。每一不同的存储体组可具有形成在芯片上的多个存储体(例 如,存储体214-0、214-1、214-2及214-M,但存储体的数目不限于四个)。在多个实施例中,至 少三个阵列可各自与形成在芯片上的不同存储体相对应。不同存储体可选自存储体214-0、 214-1、214-2及214-M。在多个实施例中,至少三个阵列可各自与形成在芯片上的单个存储 体(例如,存储体214-0,以及其它可能的存储体)的不同段(例如,段216-0、216-1、216-2及 216-P,但段的数目不限于四个)相对应。 在各种实施例中,可选择在芯片上各种位置处的多个存储体组213-0、...、213-N, 多个存储体214-0、...、214-M及/或多个段216-0、...、216-P中的任何三个或多个三个用于 冗余存储单个数据文件102及/或用于比较存储于其上的数据值以用于确定可能匹配。除其 它可能的考虑因素之外,单个数据文件的大小(例如,数据值的数目)可能会影响在其上存 储单个数据文件102的阵列的确定。举例来说,可选择图2中所展示的存储体组213中四分之 三,可选择存储体组213-0中的四分之三存储体214,或可选择三个不同存储体组中的每一 8 CN 111587422 A 说 明 书 5/12 页 个中的一个存储体,及/或可选择存储体214-0中的四分之三段216,或可选择三个不同存储 体中的每一个中的一段。 在多个实施例中,选自多个阵列的用于冗余存储单个数据文件102的至少三个阵 列可各自以DRAM配置形成在芯片上。本文中所描述的电路系统的实施方式可用于确定例如 由符合协议(例如,JEDEC所发布的那些协议,包含DDR3、DDR4等)的DRAM配置中的三分之二 阵列存储的数据值之间的匹配。 取决于存储器装置210及/或芯片上的阵列213、214、216的架构,在其上冗余地存 储单个数据文件102的阵列可能在物理上并不彼此接近(例如,相邻及/或连续)。例如,考虑 到路由及/或裸片大小的考虑因素,阵列213、214、216可以在物理上彼此分开(例如,经由信 道217及/或219)。 图3为根据本发明的多个实施例说明用于比较由三个阵列存储的数据值的电路系 统330的实例的示意图。如本文中所描述,多个存储器单元阵列可形成在芯片上336,且在一 些实施例中,单个数据文件102可由多个阵列中的三个阵列(例如,在308-0处的阵列X,在 308-1处的阵列Y及在308-2处的阵列Z)中的每一个冗余存储。在多个实施例中,包含三个阵 列308-0、308-1及308-2的多个阵列可以相同的存储器单元配置形成在芯片上336。相同的 配置可便于比较器电路系统332比较及匹配经由相应数据线(例如,kn位数据总线)307-0、 307-1及307-2从三个阵列308-0、308-1及308-2存取的冗余存储数据值。 例如,多个阵列中的每一个(例如,如在213、214及/或216处所展示且结合图2进行 描述)可经配置为DRAM电路系统,其中存储体组213中的每一个可包含相同数目个存储体 214且存储体214中的每一个可包含相同数目个段216(例如,子阵列)。每一存储体214及/或 段216可包含相同数目个存储器单元行。每一行可包含相同数目个存储器单元,借此每一存 储体214及/或段216可包含相同数目个存储器单元列。呈DRAM配置的存储器单元可各自形 成为一个接入装置(例如,晶体管)及一个存储元件(例如,电容器)的1T1C存储器单元,其各 自可耦合到在感测电路系统212中的感测放大器(未展示)。然而,实施例不限于此,使得一 些实施例可具有呈2T2C DRAM配置(例如,其中每一存储器单元可耦合到感测电路系统212 中的感测放大器及/或计算组件(未展示))或其它配置(例如,3T配置,以及其它可能的配 置)的存储器单元。 比较器电路系统332可经配置以比较由选自多个阵列的三个阵列308-0、308-1及 308-2存储的数据值,以确定在由所述三个阵列中的至少两个阵列存储的数据值之间是否 存在匹配。如本文中所描述,单个数据文件102可由三个阵列中的每一个冗余地存储,且比 较器电路系统332可经配置以比较由三个阵列存储的单个数据文件的数据值。比较器电路 系统332可形成(例如,定位)在具有多个阵列的芯片上336。比较器电路系统332可定位在芯 片上336的各个位置中(例如,考虑到路由及/或时序考虑因素)。 比较器电路系统332可进一步经配置以基于由阵列中的两个存储的单个数据文件 102中的不匹配的可调整阈值数目及/或此类不匹配的位置来确定数据值之间是否存在匹 配。在多个实施例中,不匹配的可调整阈值数目可为0到10个不匹配,其可基于多个参数(例 如,单个数据文件102中的数据值的数目)来调整。可调整阈值数目可调整为无不匹配(0个 不匹配)。例如,当由功能性338启用及/或控制的操作的恰当执行可影响乘客及/或旁观者 的安全(例如,用以避免与另一汽车及/或行人发生碰撞的自主汽车的制动及/或避让操纵, 9 CN 111587422 A 说 明 书 6/12 页 及许多其它可能操作)时,0个不匹配可经选择为阈值数目。因此,形成在芯片上336的多个 存储器单元阵列及/或比较器电路系统332可形成(例如,定位)在自主运载工具上,及各种 其它可能位置及/或实施方式中。 比较器电路系统332的输出组件333可经配置以响应于由两个阵列存储的数据值 之间的匹配的确定以输出三个阵列中的两个阵列(例如,从阵列308-0、阵列308-1或阵列 308-2)中的一个的数据值。举例来说,如本文中进一步所描述(例如,结合图5至7),当由阵 列308-0及阵列308-1,由阵列308-0及阵列308-2或由阵列308-1及阵列308-2存储的单个数 据文件102的数据值之间存在由比较器电路系统332确定的匹配时,输出组件333可从阵列 中的选定阵列中输出数据值。 输出组件333可进一步经配置以将来自一个阵列的数据值发送到形成在芯片上 336的串行器334,以输出到形成在芯片外337的功能性338。串行器334可经配置以将经由数 据总线(例如,kn位数据总线)307从三个阵列308-0、308-1、308-2中的一个移动到串行器 334的单个数据文件102的n个部分重构为单个数据值(位)序列。单个数据文件102的单个数 据值序列可经由数据总线(例如,k位数据总线)304从串行器334发送到功能性338。图3中所 展示的功能性338可为启用及/或控制各种操作的多个芯片外功能性中的一个(例如,每一 功能性可启用及/或控制执行与由另一功能性启用及/或控制的操作不同的单个操作及/或 操作组)。识别(例如,通过控制器211)正在请求哪个特定的单个数据文件(例如,通过主机 及/或功能性)可使得能够确定单个数据文件102的单个数据值序列发送至其的特定芯片外 功能性。 在多个实施例中,可响应于通过由比较器电路系统332比较由阵列308-0及阵列 308-1,由阵列308-0及308-2,或由阵列308-1及308-2存储的单个数据文件102的数据值来 确定无匹配,来发送无匹配的通知335。通知335可发送到耦合到功能性338及/或功能性338 的一部分的监视器组件339。接收此通知335可向监视器组件339指示,可不依赖于由三个阵 列存储的数据值(指令)序列中的任一者没有数据错误,且意图由功能性338执行的功能将 被禁用(例如,归因于执行错误指令可能发生意外结果)。响应于由三个阵列中的至少两个 阵列存储的数据值之间的无匹配或不匹配的确定及通知335,监视器组件339可启动用于故 障转移功能性(未展示)的指令(例如,具有存储在芯片外337存储器中的指令的指定功能 性)的执行。在多个实施例中,可执行故障转移功能性以执行替代功能来代替禁用功能(例 如,将自主汽车停靠或停放在可用的停车位中,及许多其它可能性)。 在多个实施例中,还可响应于由比较器电路系统332确定由阵列308-0、308-1及/ 或308-2冗余地存储的数据值之间的至少一个匹配而发送通知335。可将确认确定至少一个 匹配的通知335发送到功能性338、监视器组件339及/或主机。 通过比较由所有阵列308-0、308-1及308-2存储的单个数据文件102的数据值及/ 或单独参考阵列308-0与308-1之间、阵列308-0与阵列308-2之间或阵列308-1与308-2之间 的比较来确定无匹配的通知335可由特定信号(例如,数据值0)提供。相比之下,通过比较由 所有阵列308-0、308-1及308-2存储的数据值及/或分别参考阵列308-0与阵列308-1之间、 阵列308-0与阵列308-2之间或阵列308-1与308-2之间的的比较来确定至少一个匹配的通 知335可由不同信号(例如,数据值1)提供(例如,如结合图6及本文中别处所描述)。 在多个实施例中,无匹配或至少一个匹配的通知335可通过专用数据线及/或引脚 10 CN 111587422 A 说 明 书 7/12 页 在芯片外337直接发送到功能性338、监视器组件339,及/或与主机,如在图3中所指示。在多 个实施例中(例如,在可能不存在专用数据线及/或引脚的情况下),通知335可经由串行器 334及/或先进先出(FIFO)队列(未展示)发送。在多个实施例中,FIFO队列可用于确定来自 串行器334的输出次序。在多个实施例中,通知335可直接或经由串行器334及/或FIFO队列 在芯片外337发送到故障转移功能性,以快速地启用用于替代功能的指令的执行。通知335 可作为被包含在由串行器334及/或FIFO队列输出的数据突发的特定位置(例如,在最后的 单位间隔)处的信号(例如,数据值0或1)发送。替代地或另外,可将通知335发送到芯片上 336的控制器211,以确定是否将通知335在芯片外337发送到功能性338、监测器组件339、故 障转移功能性及/或主机以确定替代功能。 在多个实施例中,响应于比较器电路系统332确定至少一个匹配,可将将单个数据 文件102的n个部分在芯片上336从比较器电路系统332发送到串行器334。通过串行器334重 构的单个数据文件102的单个数据值序列可从串行器334在芯片外337发送到的功能性338, 而无需将通知335发送到监视器组件339。相比之下,响应于比较器电路系统332确定无匹 配,通知335可发送到芯片外337的监视器组件339。 在多个实施例中,监视器组件339可经配置以响应于通知335的输入来决定是否启 用及/或启用何种功能(例如,当比较器电路系统332确定通知无匹配时)。监视器组件339还 可经配置用于从多个其它组件及/或系统(例如,自主运载工具)的多个信号及/或数据的输 入,以有助于做出是否启用及/或启用何种功能的决定。监视器组件339还可经配置以连续 地启用故障转移功能性及/或执行替代功能(例如,直到确定所请求单个数据文件的至少两 个阵列之间的匹配为止,或直到在中断之后已恢复将电力供应到存储器装置210为止,及其 它可能性)。 图4为根据本发明的多个实施例说明比较器组件440的实例的示意图。在图4中所 说明的比较器组件440可耦合到在332处所展示且结合图3所描述的比较器电路系统及/或 在532处所展示且结合图5及本文中别处所描述的比较器电路系统,或成为其一部分。 在使选自多个阵列的至少三个阵列用于单个数据文件102的冗余存储的多个实施 例中,可存在与选自多个阵列的多个阵列相对应的比较器电路系统332的比较器组件440。 多个比较器组件可与至少三个阵列的每一不同配对相对应。例如,当阵列的数目为选自多 个阵列的三个阵列(例如,阵列308-0、308-1及308-2)时,可存在与三个阵列相对应的三个 比较器组件440。三个比较器组件440可与三个阵列的三个不同配对中的每一配对(例如, 308-0处的阵列X与308-1处的阵列Y配对,308-0处的阵列X与308-2处的阵列Z配对,且308-1 处的阵列Y与308-2处的阵列Z配对)相对应。多个比较器组件440可各自经配置以经由与由 至少三个阵列中的两个(例如,阵列X及阵列Y)存储的每一配对数据值相对应的逻辑门(例 如,逻辑门442-0、442-1、...、442-Q)比较两个配对的数据值(例如,数据值x0与y0、x1与 y1、...、xQ与yQ)。 在多个实施例中,n位比较器组件440可比较冗余地存储在两个阵列中的所有kn个 配对数据值(位)(例如,经由kn位数据总线107-0及107-1从阵列X及阵列Y存取)。例如,可使 用对应逻辑门442-0、442-1、...、442-Q来确定配对数据值中的每一个之间是否存在匹配来 分析冗余地存储在阵列X及Y中的单个数据文件102的所有配对数据值x0与y0、x1与y1、...、xQ 与yQ。如图4中所展示,逻辑门442中的每一个可为XNOR逻辑门或可包含XNOR逻辑门,但实施 11 CN 111587422 A 说 明 书 8/12 页 例不限于XNOR逻辑门。XNOR逻辑门在从两个阵列存取的特定配对数据值匹配时可输出特定 信号(例如,数据值1),而在从两个阵列存取的不同配对数据值不匹配时可以输出不同信号 (例如,数据值0)。可对冗余存储在阵列X及阵列Z以及阵列Y及阵列Z中的配对数据值中的每 一个执行相同类型的比较。 由三个比较器组件440中的每一个确定的差分指示符可用于指示对三个不同配对 中的每一配对的数据值的比较是否指示对于三个阵列的三个不同配对中的每一配对的匹 配。例如,当来自阵列X及阵列Y的所有配对数据值匹配(X=Y)时,逻辑门444可输出特定的 差分指示信号(例如,数据值为1),如通过从多个逻辑门442输出匹配信号(例如,所有数据 值为1)所确定。例如,当来自阵列X及阵列Y的所有配对数据值不匹配(X≠Y)时,逻辑门444 可输出特定的差分指示信号(例如,数据值为0),如通过从多个逻辑门442输出不匹配信号 (例如,至少一个数据值为0)所确定。如在图4中所展示,逻辑门444可为“与”逻辑门或可包 含“与”逻辑门,但实施例不限于“与”逻辑门。可如结合图6及/或图7以及本文中别处所描述 使用差分指示器。 图5为根据本发明的多个实施例说明选择性耦合到比较器电路系统的三个阵列的 实例550的示意图。如在图5中所展示的实例550中所说明,在多个实施例中,可将三个阵列 (例如,在508-0处的阵列X,在508-1处的阵列Y及在508-2处的阵列Z)选择性地耦合(例如, 经由三组数据线507-0、507-1及507-2)在芯片536上到比较器电路系统532的相应三个比较 器组件(例如540-0、540-1及540-2)。阵列508各自可形成在213、214及216处所展示且结合 图2所描述的替代实施例中的一或多个中。比较器组件540各自可如440处所展示形成且如 结合图4所描述地操作,或比较器组件540各自可以不同配置形成(例如,具有不同逻辑门 442及/或444或其它配置上的不同)。 在多个实施例中,三个比较器组件540-0、540-1及540-2中的每一个可选择性地耦 合到比较器电路系统532的输出启用器552。比较器电路系统532的输出组件533可经配置以 响应于确定由多个阵列存储的数据值之间的匹配而输出单个数据文件102冗余地存储在其 中的至少三个阵列的多个阵列中的一个的数据值。单个数据文件102可冗余地存储在其上 的至少三个阵列可经由单个网络套接字存取(例如,通过定位在芯片上536的控制器211及/ 或形成在芯片外537的功能性538、监视器组件539及/或主机)且不可经由用于冗余存储器 的对应冗余网络套接字存取。 输出启用器552可经配置以响应于由输出启用器552确定在多个实施例中由单个 数据文件102冗余地存储在其中的三个阵列中的两个存储的数据值之间的匹配来启用输出 组件533的激活。例如,当在阵列508-0、508-1及/或508-2中的至少两个之间存在单个数据 文件102的数据值的匹配时,如由相应三个比较器组件540-0、540-1及540-2确定,输出启用 器552可将激活信号(例如数据值为1)发送到输出组件533。输出启用器552可进一步经配置 以响应于由输出启用器552确定由三个阵列中的两个存储的数据值之间无匹配,将通知535 (例如,如335处所展示且结合图3所描述)输出到在芯片外537形成的监视器组件539。 例如,启用信号(例如,数据值为1)可通过输出启用器552的逻辑门输出,以启用输 出组件533的激活及/或提供通知535。如在图5中所展示,输出启用器552的逻辑门可为“或” 逻辑门或可包含“或”逻辑门,但实施例不限于“或”逻辑门。 经激活输出组件533可经配置以(例如,作为多路复用器)以响应于确定由三个阵 12 CN 111587422 A 说 明 书 9/12 页 列中的两个存储的数据值之间的匹配在第一总线555-0到第一阵列(例如,在508-0处的阵 列X)的耦合与第二总线555-1到第二阵列(例如,在508-1处的阵列Y)的耦合之间进行选择。 经激活输出组件533可基于与由三个阵列中的第三阵列(例如,在508-2处的阵列Z)存储的 数据值的有效匹配(例如,如结合图6及在本文中别处所描述),存取来自第一阵列或第二阵 列的数据值。从第一阵列或第二阵列存取的数据值可经由数据总线507(例如,在307处所展 示且结合图3所描述的kn位数据总线)移动到串行器534。串行器534可经由数据总线504(例 如,在304处所展示且结合图3所描述的k位数据总线)将从第一阵列或第二阵列存取的数据 值作为单个数据文件102的单个数据值序列发送到芯片537外。因此,输出组件533可启用将 与有效匹配相对应的数据值从第一阵列或第二阵列输出到形成在芯片外537的功能性538。 比较器电路系统532的验证组件554可经配置以确定由第一阵列(例如,在508-0处 的阵列X)存储的数据值与由第二阵列(例如,在508-1处的阵列Y)存储的数据值之间的比较 的第一结果和由第一阵列(例如,在508-0处的阵列X)存储的数据值与由第三阵列(例如,在 508-2处阵列Z)存储的数据值之间的比较的第二结果之间的有效匹配。基于对由三个阵列 中的两个存储的数据值之间的匹配的确定来激活输出组件533的输出启用器552指示在阵 列X或阵列Y与三个阵列中的至少一个其它阵列之间存在有效匹配(例如,阵列X匹配阵列Y 及/或阵列Z或阵列Y匹配阵列X及/或阵列Z)。因此,在508-0处的阵列X或在508-1处的阵列Y 为有效的(例如,或阵列X及阵列Z两者均可为有效的)。结合图7及在本文中别处描述确定是 输出来自阵列X还是来自阵列Z的数据值。 验证组件554可进一步经配置以指示有效匹配的数据值(例如,来自阵列X或阵列 Y)由经激活的输出组件533输出(例如,经由第一总线555-0到508-0处的阵列X的选择及耦 合,或经由第二总线555-1到508-1处的阵列Y的选择及耦合)。例如,特定验证信号(例如,数 据值为0)可由验证组件554的逻辑门输出,以启用经由经激活的输出组件533从507-0处的 阵列X输出数据值。相比之下,不同验证信号(例如,数据值为1)可由验证组件554的逻辑门 输出,以启用经由经激活的输出组件533从507-1处的阵列Y输出数据值。验证组件554的逻 辑门可为或可包含“与”逻辑门,如在图5中所展示。在多个实施例中,如在图5中所展示, “与”逻辑门可具有耦合到“非”逻辑门的一个输入,但实施例不限于“与”逻辑门及/或“非” 逻辑门。 图6为根据本发明的多个实施例的用于确定由三个阵列存储的数据值之间是否存 在匹配的逻辑的实例。逻辑电路系统(例如,由图6中所展示的真值表所表示)可接收来自比 较器组件的差分指示符的输出(例如,数据值或0或1,如结合图4所描述),及由三个阵列存 储的用于确定有效匹配的数据值的有效性的确定(例如,如结合图6所描述)。 由真值表表示的逻辑电路系统接收来自三个比较器组件(例如,在540-0、540-1及 540-2处所展示并结合图5所描述的比较器组件)的差分指示符的输出,以指示三个阵列的 三个不同配对中的每一配对存在匹配还是不存在匹配。阵列的三个不同配对经展示在列标 头660-1处用于在阵列X与阵列Y之间进行比较;在列标头660-2处用于在阵列Y与阵列Z之间 进行比较;以及在列标头660-2处用于在阵列X与阵列Z之间进行比较。依据比较由三个阵列 存储的数据值的有效性所作的确定经展示在列标头661下。 逻辑电路系统经配置以启用(例如,通过控制器211、输出启用器552、验证组件554 及/或另一在芯片上536逻辑启用组件(未展示))由此确定:由所有三个阵列存储的数据值 13 CN 111587422 A 说 明 书 10/12 页 是否匹配且有效661-8;由阵列中的特定一个存储的数据值是否与由其它两个阵列存储的 数据值不匹配,由其它两个阵列存储的数据值确实匹配且有效(例如,如针对阵列Y所展示 在661-2处无效,如针对阵列X所展示在661-3处无效,如针对阵列Z所展示在661-5处无效); 且由所有三个阵列存储的数据值是否与由其它两个阵列存储的数据值不匹配且均无效 661-1。可依据比较做出的其它确定661为基于一个阵列的数据值与其它阵列中的两个的数 据值均匹配,比较结果为不可能661-4、661-6及661-7,但其它阵列中的两个的数据值经确 定彼此不匹配(例如,如在661-4处所指示,展示两个阵列X及Y的数据值均与阵列Z的数据值 匹配,且还展示阵列X及Y的数据值彼此不匹配)。 图7为根据本发明的多个实施例的用于选择一个阵列用于输出匹配数据值的逻辑 的实例。逻辑电路系统(例如,由图7中所展示的真值表表示)可(例如,从验证组件554)接收 关于是否已针对由第一阵列存储的数据值与由第二阵列存储的数据值之间的第一比较(例 如,如列标头760-2处所示,用于比较作为第二阵列的阵列Y与作为第一阵列的阵列Z)及由 第一阵列存储的数据值与由三个阵列中的第三阵列存储的数据值之间的第二比较(例如, 如列标头760-3处所展示,用于比较作为第三阵列的阵列X与作为第一阵列的阵列Z)而确定 有效匹配的差分信号(例如,针对阵列中的两个的数据值的匹配,数据值为1,且针对两个阵 列的不匹配,数据值为0)。如由真值表所表示的逻辑电路系统可经配置以启用由此确定(例 如,通过控制器211、验证组件554及/或另一芯片上536逻辑启用组件)指示输出组件533选 择第二阵列(例如,阵列Y)还是第三阵列(例如,阵列X)以输出匹配的数据值。 由阵列的比较产生的差分信号可用于确定选择(例如,基于数据值0或1)匹配阵列 中的哪个阵列(例如,如列标头770下所指示)用于由输出组件533进行的数据值输出。在多 个实施例中,数据值0可指示将选择阵列X,且数据值1可指示将选择阵列Y。例如,如在770-4 处所展示,逻辑电路系统可经配置以响应于接收到与第一阵列(例如,阵列Z)相比已确定第 二阵列(例如,阵列X)及第三阵列(例如,阵列Y)两者的有效匹配的信号(例如,数据值为0) 而启用指示将第二阵列(例如,阵列X)选择作为默认选项用于由输出组件533进行输出。当 已确定匹配时(例如,通过输出启用器552),可使用阵列X的默认选项,但如在770-1处所示, 阵列Y及阵列X均不与阵列Z匹配,此意味着阵列X与Y匹配。如770-2处所展示,阵列Y不匹配 阵列Z且阵列X匹配阵列Z使得能够选择阵列X。如在770-3处所展示,阵列Y匹配阵列Z且阵列 X不匹配阵列Z使得能够选择阵列Z。 如在772处标记为“功能”的列标头下所指示,在772-1、772-2及772-4处选择X阵列 可启用(例如,指示)输出组件533(例如,多路复用器)选择性地耦合数据线507-0及/或第一 总线555-0的集合用于存取508-0处的X阵列的数据值。相比之下,在772-3处选择Y阵列可启 用(例如,指示)输出组件533选择地耦合数据线507-1及/或第二总线555-1的集合用于存取 508-1处的Y阵列的数据值。 图8为根据本发明的多个实施例的用于确定由三个阵列存储的数据值之间的匹配 的方法880的流程图。除非明确说明,否则本文中所描述的方法的要素不限于特定次序或顺 序。另外,本文中所描述的多个方法实施例或其元件可在相同或基本上相同的时间点执行。 在框882处,在多个实施例中,方法880可包含通过存储器装置(例如,如在210处所 展示且结合图2所描述)接收单个数据文件(例如,如在102处所展示且结合图1及本文中别 处所描述)。在框883处,方法880可包含将单个数据文件冗余地存储在选自形成在芯片上的 14 CN 111587422 A 说 明 书 11/12 页 多个存储器单元阵列的三个阵列上(例如,如结合图1及2以及在本文中别处所描述)。在框 884处,方法880可包含比较由三个阵列存储的单个数据文件的数据值,以确定由三个阵列 中的至少两个阵列存储的数据值之间是否存在匹配(例如,如结合图1及3到6及在本文中别 处所描述)。在框885处,方法880可包含响应于确定由三个阵列中的两个阵列存储的数据值 之间的匹配而输出所述两个阵列中的一个的数据值(例如,如结合图1、3至5及7以及本文中 别处所描述)。 在多个实施例中,方法880可包含中断供应到形成在芯片上的存储区装置的电力。 中断电力可导致至少部分地基于中断电力而禁用通过执行由芯片上的单个数据文件存储 的指令而执行的功能响应于所述功能经禁用,方法880可包含输出所述禁用功能的通知(例 如,如在335处所展示且结合图3及在本文中别处所描述),以使得在芯片外存储的故障转移 功能性能够执行替代功能(例如,代替经禁用功能)。 如本文中所使用,序数定位用于在相应元素组内的元素的相对位置之间进行区 分。然而,除非上下文另外明确指出,否则本文中使用例如“第一”、“第二”及“第三”的序数 并非旨在指示元件的特定序数位置。例如,认为在多个阵列中,存储器单元阵列具有阵列0 的序数位置且不同阵列具有阵列2的序数位置。在此实例中,尽管没有阵列3的序数位置,但 阵列0可被称为“第一”阵列,且阵列1可被称为“第三”阵列。替代地,除其它可能性之外,阵 列3可被称为“第一”阵列,且阵列0可被称为“第二”或“第三”阵列。 在本发明的上述详细描述中,参考形成本发明的一部分的附图,并且在附图中通 过说明的方式展示如何可以实践本发明的一或多个实施例。充分详细地描述这些实施例以 使得所属领域的技术人员能够实践本发明的实施例,且应理解,可利用其它实施例且可在 不背离本发明的范围的情况下做出过程、电或结构改变。 如本文中所使用,尤其关于图式,带有连字符的数字及/或例如“X”、“Y”、“N”、“M” 等指定符的参考编号(例如,图2中的213-0、213-1、213-2及213-N)指示可包含多个如此指 定的特定特征。还应理解,本文中所使用的术语是仅出于描述特定实施例的目的且并非旨 在为限制性。如本文中所使用,除非上下文另有明确规定,单数形式“一(a)”、“一(an)”及 “所述(the)”包含单数及复数指示物,“多个(a number of)”、“至少一个”及“一或多个”也 如此(例如,多个存储器阵列可指代一或多个存储器阵列),而“多个(plurality of)”旨在 指代多于一个此类事物。此外,贯穿本申请案,措词“可能”和“可以”是以允许的意义(即,具 有潜在的,能够的)而不是在强制意义上(即,必须)使用。术语“包含”及其派生词意指“包含 但不限于”。术语“经耦合”及“耦合”意指直接或间接地物理连接以用于存取及/或移动(传 输)指令(例如,控制信号、地址信号等)及数据,视上下文而定。术语“数据”及“数据值”在本 文中可互换使用,且可具有相同含义,视上下文而定(例如,一或多个数据单元或“位”)。 虽然本文中已说明且描述包含阵列、比较器电路系统、比较器组件、输出启用器、 验证组件、输出组件、功能性、监视器组件以及用于确定由三个阵列存储的数据值之间的匹 配的其它电路系统的各种组合及配置的实例实施例,但本发明的实施例不限于本文中明确 陈述的那些组合。阵列、比较器电路系统、比较器组件、输出启用器、验证组件、输出组件、功 能性、监视器组件以及用于确定由本文中所揭示的三个阵列存储的数据值之间的匹配的其 它电路系统的其它组合及配置明确地包含在本发明的范围内。 尽管本文中已说明并描述特定实施例,但所属领域的技术人员将了解,经计算以 15 CN 111587422 A 说 明 书 12/12 页 实现相同结果的布置可替代所展示的特定实施例。本发明旨在涵盖本发明的一或多个实施 例的变更或变化。应理解,上述描述是以说明性方式进行的,而非限制性的。在阅读以上描 述后,上述实施例的组合以及本文未具体描述的其它实施例对于所属领域的技术人员来说 将是显而易见的。本发明的一或多个实施例的范围包含括使用上述结构及过程的其它应 用。因此,应参考所附权利要求以及这些权利要求所赋予的等价物的全部范围来确定本发 明的一或多个实施例的范围。 在前述的