技术摘要:

本申请实施例提供一种毛刺检测电路,其包括:沿检测模块,用于通过边沿检测确定电源电压信号出现上冲或者下冲时的毛刺尖峰;锁存模块,用于在检测到所述毛刺尖峰时进行翻转动作以对所述毛刺尖峰进行锁存;复位模块,用于根据锁存的所述毛刺尖峰生成毛刺复位信号以触发 全部

背景技术:

由于环境的影响,高速信号在传播中会产生各种毛刺,比如电源给电子设备提供 电源电压信号的情景中常常会产生一些毛刺信号。为此,现有技术中提供了一些解决方案, 在这些解决方案中,主要利用两个比较器把毛刺信号和设定的基准信号进行比较,产生毛 刺复位信号,然后使用该毛刺复位信号触发毛刺去除处理。然而,受限于比较器的带宽,翻 转速度较慢,尤其对于毛刺信号在纳秒级别甚至更短的情形,无法应对。

技术实现要素:

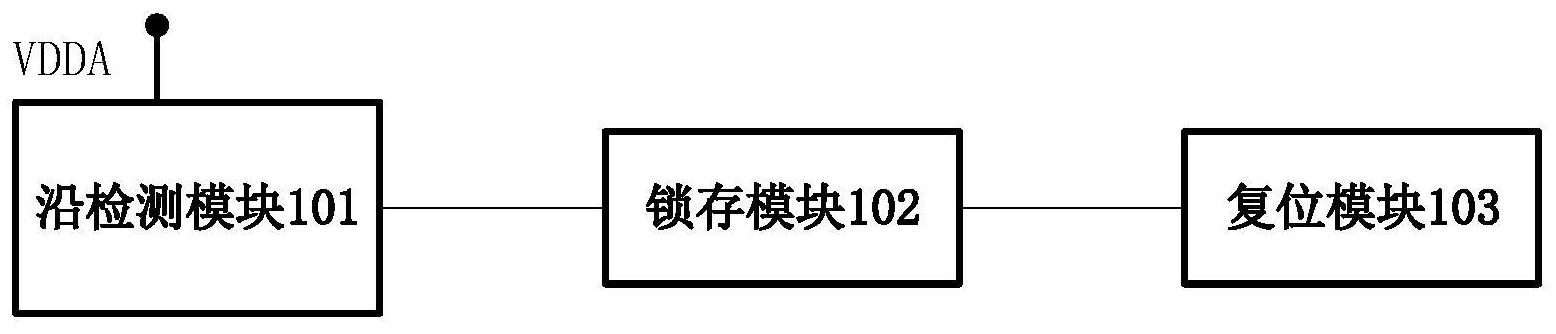

有鉴于此,本申请实施例所解决的技术问题之一在于提供一种毛刺检测电路,用 以克服现有技术中上述缺陷。 本申请实施例提供一种毛刺检测电路,其包括: 沿检测模块,用于通过边沿检测确定电源电压信号出现上冲或者下冲时的毛刺尖 峰; 锁存模块,用于在检测到所述毛刺尖峰时进行翻转动作以对所述毛刺尖峰进行锁 存; 复位模块,用于根据锁存的所述毛刺尖峰生成毛刺复位信号以触发去毛刺处理。 可选地,在本申请的任一实施例中,所述沿检测模块包括:开关单元以及储能单 元,所述开关单元用于在检测到所述毛刺尖峰时进行相应的开关动作并在检测到所述毛刺 尖峰时触发所述锁存模块进行翻转以对检测到的所述毛刺尖峰进行锁存。 可选地,在本申请的任一实施例中,所述开关单元包括:第一开关器件以及第二开 关器件,所述第一开关器件的第一端与电源电连接,所述第一开关器件的另一第二端通过 所述储能元件与所述第二开关器件的第一端电连接,所述第二开关器件的第二端电连接第 一低电平,所述储能单元的第一端分别与所述第一开关器件的第二端以及所述第二开关单 元的第一端电连接,且所述储能单元的第二端电连接第二低电平;对应地,所述第一开关器 件以及第二开关器件之间连接有所述储能单元。 可选地,在本申请的任一实施例中,所述第一开关器件为第一PMOS管,所述第二开 关器件为第一NMOS管,所述第一PMOS管的源极与电源电连接,所述第一PMOS管的漏极与所 述第一NMOS管的漏极电连接,所述储能单元的第一端分别与所述第一NMOS管的漏极和所述 第一PMOS管的漏极之间电连接有所述储能单元。 可选地,在本申请的任一实施例中,还包括:低通滤波器,用于对所述毛刺尖峰进 行低通滤波,并在施加到所述第一PMOS管源极的所述电源电压信号的控制下使得所述第一 NMOS管和所述第一PMOS管进行开关动作。 可选地,在本申请的任一实施例中,所述第一NMOS管的栅极和源极之间连接有电 4 CN 111722020 A 说 明 书 2/9 页 流镜。 可选地,在本申请的任一实施例中,所述低通滤波器包括:滤波电阻,所述滤波电 阻与所述第一PMOS管的栅极和/或源极连接。 可选地,在本申请的任一实施例中,所述低通滤波器还包括滤波电容,所述滤波电 容与所述第一PMOS管的栅极和/或源极连接。 可选地,在本申请的任一实施例中,所述锁存模块包括第一逻辑处理单元,用于对 所述尖峰信号进行逻辑处理以进行翻转以及对所述毛刺尖峰进行锁存。 可选地,在本申请的任一实施例中,所述第一逻辑处理单元包括:第一或非逻辑子 单元以及第一反相子单元,所述第一或非逻辑子单元用于对所述毛刺尖峰进行或非处理得 到逻辑输出信号,所述第一反相子单元用于对所述第一或非逻辑子单元的逻辑输出信号进 行反相处理以进行翻转以及对所述毛刺尖峰进行锁存。 可选地,在本申请的任一实施例中,还包括:第二PMOS管以及第二NMOS管,所述第 二PMOS管的栅极连接上电复位信号,所述第二PMOS管的源极与电源连接,所述第二PMOS管 的漏极与所述第一反相子单元的输入端连接,所述第二NMOS管的漏极与所述第一反相子单 元的输出端连接,所述第二NMOS管的栅极连接所述上电复位信号的反相信号。 可选地,在本申请的任一实施例中,所述锁存模块包括第四反相子单元以及锁存 器,所述锁存器的复位端与所述第四反相子单元连接,所述锁存器的时钟端与所述沿检测 模块连接以进行翻转以及对所述毛刺尖峰进行锁存。 可选地,在本申请的任一实施例中,所述复位模块包括第二逻辑处理单元,用于对 锁存的所述毛刺尖峰进行逻辑处理以生成毛刺复位信号。 可选地,在本申请的任一实施例中,所述第二逻辑处理单元包括第二或非逻辑子 单元、第二反相子单元以及第三反相子单元,所述第三反相子单元用于对所述锁存模块的 输出信号进行反相处理;所述第二或非逻辑子单元用于对所述第三反相子单元的输出信号 进行或非处理,所述第二反相子单元用于对所述第二或非逻辑子单元的输出信号进行反相 处理生成毛刺复位信号。 可选地,在本申请的任一实施例中,所述第二或非逻辑子单元进一步用于对所述 第三反相子单元的输出信号以及上电复位信号的反相信号进行或非处理。 可选地,在本申请的任一实施例中,还包括:延迟单元,用于对所述锁存模块的输 出进行延迟处理后传输至所述复位模块。 可选地,在本申请的任一实施例中,所述锁存模块还电连接一锁存复位信号,用于 对毛刺检测信号进行复位。 本实施例中,由于检测模块通过边沿检测确定电源电压信号中出现的毛刺尖峰; 锁存模块在检测到的所述毛刺尖峰时进行翻转动作以对所述毛刺尖峰进行锁存;复位模块 根据锁存的所述毛刺尖峰生成毛刺复位信号以触发去毛刺处理,从而摆脱了比较器的带宽 束缚,提高了翻转速度,尤其可以应对纳秒级别甚至更短的毛刺信号。 附图说明 后文将参照附图以示例性而非限制性的方式详细描述本申请实施例的一些具体 实施例。附图中相同的附图标记标示了相同或类似的部件或部分。本领域技术人员应该理 5 CN 111722020 A 说 明 书 3/9 页 解,这些附图未必是按比例绘制的。附图中: 图1为本申请实施例一中毛刺检测电路的模块示意图; 图2为本申请实施例二中毛刺检测电路检测上冲的具体结构示意图; 图3为本申请实施例三中毛刺检测电路检测下冲的另一种具体结构示意图 图4为本申请实施例四中毛刺检测电路的控制时序示意图。 图5为本申请实施例五中毛刺检测电路检测下冲的具体结构示意图; 图6为本申请实施例六中毛刺检测电路检测下冲的另一种具体结构示意图;