技术摘要:

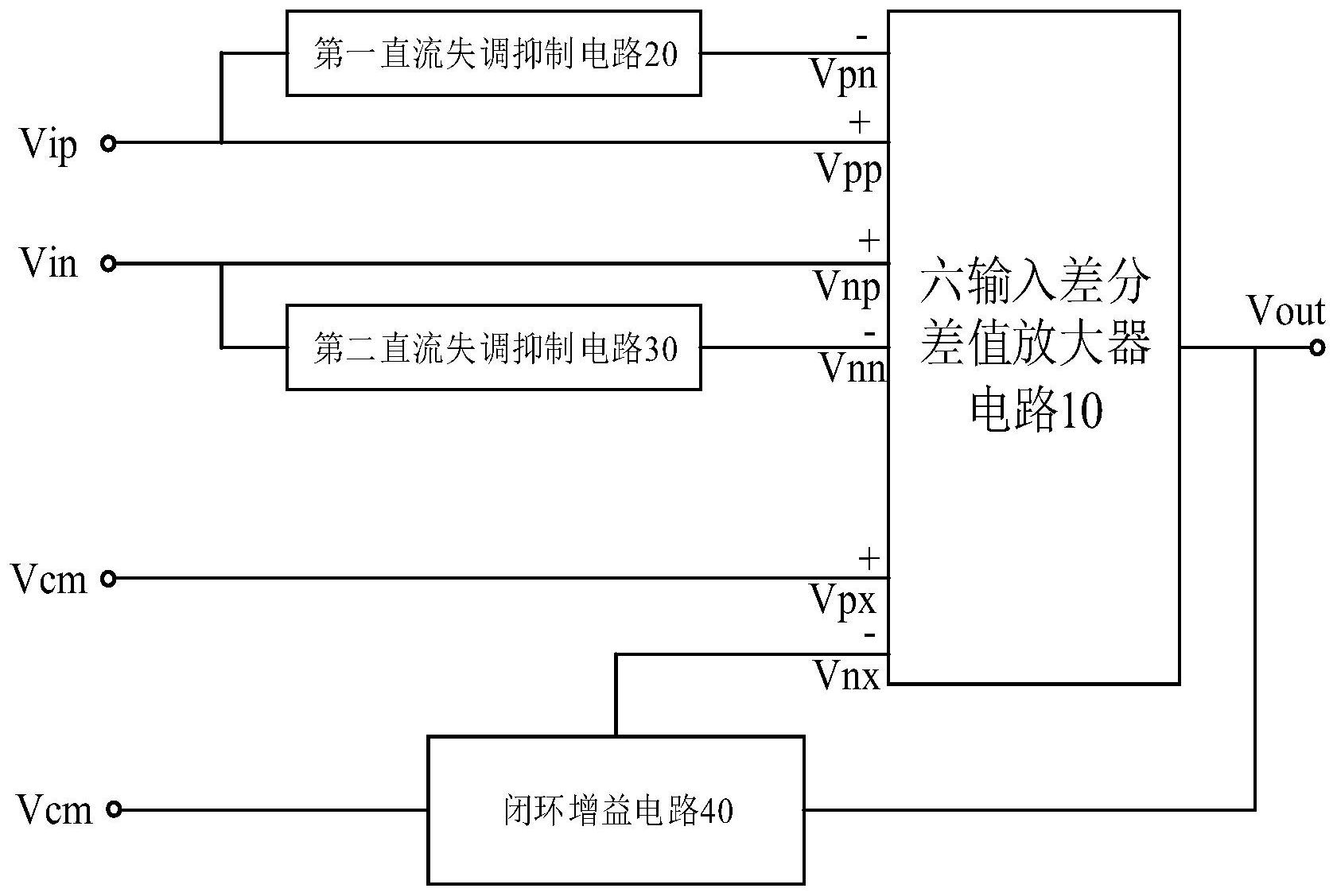

本发明公开了一种直流耦合差分前端放大器电路,包括:六输入差分放大器电路、第一直流失调抑制电路、第二直流失调抑制电路、闭环增益电路;第一直流失调抑制电路和第二直流失调抑制电路用于抑制直流失调电压;闭环增益电路作为负反馈环路为直流耦合差分前端放大器电路 全部

背景技术:

生物电信号的前端放大器是健康信息采集系统的核心模块。作为整个采集系统直 接接触电极实现信号采集的首个电路模块,其采集精度直接影响了获取的健康信息的准确 度。在生物电信号如心电、脑电等微弱生物电信号的采集测量中,通常会使用皮肤清洁剂和 具有导体胶的电极来减小皮肤阻抗,增强电极和皮肤间的导电性,然而这种传统电极具有 一定的极化电压,造成采集放大器的输入失调电压大而引起信号饱和失真,特别是长期测 量下电极极化电压会更大。另外生物电信号幅度较小,极其微弱,因而极易受到环境噪声、 电极接触扰动、电路噪声的干扰,而且上述问题在实际信号采集测量中会显得更加严重。因 此设计具有抑制失调电压、低噪声和高能效的前端放大器是打造高性能的采集系统的关 键,特别是面向穿戴式健康监测的应用趋势,越来越多的新技术开始涌现以满足高性能前 端放大器的设计需求。目前主流的设计方法是采用交流AC耦合输入,但是AC耦合的缺点是 需要在前置放大器输入端放置大的耦合电容,而大电容无法集成且存在器件失配而引起大 的输入误差。为了解决上述问题,需要提供一种新的具有可编程的高通截止频率和放大倍 数的前端放大器电路。

技术实现要素:

本发明要解决的技术问题在于,针对现有技术的缺陷,提供一种直流耦合差分前 端放大器电路。 本发明解决其技术问题所采用的技术方案是:构造一种直流耦合差分前端放大器 电路,包括:六输入差分放大器电路、第一直流失调抑制电路、第二直流失调抑制电路、闭环 增益电路,其中, 所述第一直流失调抑制电路连接在所述六输入差分放大器电路的第一正输入端 Vpp与第一负输入端Vpn之间,所述第一直流失调抑制电路与所述六输入差分放大器电路的 第一正输入端Vpp的连接点为所述直流耦合差分前端放大器电路的外部信号正差分输入端 Vip;所述第二直流失调抑制电路连接在所述六输入差分放大器电路的第二正输入端Vnp与 第二负输入端Vnn之间,所述第二直流失调抑制电路与所述六输入差分放大器电路的第二 正输入端Vnp的连接点为所述直流耦合差分前端放大器电路的外部信号负差分输入端Vin; 所述六输入差分放大器电路的正辅助输入端Vpx和所述闭环增益电路均输入共模电压Vcm, 所述六输入差分放大器电路的负辅助输入端Vnx经所述闭环增益电路与所述六输入差分放 大器电路的输出端Vout连接; 所述第一直流失调抑制电路和第二直流失调抑制电路用于抑制直流失调电压;所 述闭环增益电路作为负反馈环路为所述直流耦合差分前端放大器电路提供闭环增益。 5 CN 111585531 A 说 明 书 2/9 页 优选地,所述六输入差分放大器电路包括:偏置电路、多输入级电路、增益级电路、 输出级电路;其中, 所述偏置电路包括PMOS管Mp1、Mp2以及偏置电流源Ib;所述PMOS管Mp1的源极与电 源正端Vdd连接,所述PMOS管Mp1的漏极与所述PMOS管Mp2的源极连接,所述PMOS管Mp2的源 极经所述偏置电流源Ib与电源负端Vss连接;所述PMOS管Mp1的栅极与漏极短接,所述PMOS 管Mp2的栅极与漏极短接; 所述多输入级电路包括PMOS管Mp3、Mp4、Mp5、Mp6、Mp7、Mp8、Mp15、Mp16、Mp17以及 NMOS管Mn1、Mn3;所述PMOS管Mp3、Mp6、Mp15的源极均与所述电源正端Vdd连接,所述PMOS管 Mp3、Mp6、Mp15三者的栅极短接并连接至所述PMOS管Mp1的栅极;所述PMOS管Mp7和Mp8的栅 极分别作为所述六输入差分放大器电路的第一正输入端Vpp和第一负输入端Vpn,所述PMOS 管Mp7和Mp8的源极相连并连接至所述PMOS管Mp6的漏极,所述PMOS管Mp7的漏极与所述NMOS 管Mn3的漏极连接,所述PMOS管Mp8的漏极与所述NMOS管Mn1的漏极连接;所述PMOS管Mp4和 Mp5的栅极分别作为所述六输入差分放大器电路的第二负输入端Vnn和第二正输入端Vnp, 所述PMOS管Mp4和Mp5的源极相连并连接至所述PMOS管Mp3的漏极,所述PMOS管Mp4的漏极与 所述NMOS管Mn3的漏极连接,所述PMOS管Mp5的漏极与所述NMOS管Mn1的漏极连接;所述PMOS 管Mp16和Mp17的栅极分别作为所述六输入差分放大器电路的负辅助输入端Vnx和正辅助输 入端Vpx,所述PMOS管Mp16和Mp17的源极相连并连接至所述PMOS管Mp15的漏极,所述PMOS管 Mp16的漏极与所述NMOS管Mn1的漏极连接,所述PMOS管Mp17的漏极与所述NMOS管Mn3的漏极 连接;所述NMOS管Mn1栅极与漏极短接,所述NMOS管Mn3栅极与漏极短接,所述NMOS管Mn1和 Mn3的源极均连接至电源负端Vss; 所述增益级电路包括PMOS管Mp9、Mp10、Mp11、Mp12、Mp13以及NMOS管Mn2、Mn4、Mn5、 Mn6;所述PMOS管Mp9和Mp10构成有源电流镜作为负载,所述PMOS管Mp10的栅极与漏极短接 后与所述PMOS管Mp9的栅极连接,所述PMOS管Mp9的漏极与所述NMOS管Mn4的漏极连接,所述 PMOS管Mp10的漏极与所述NMOS管Mn2的漏极连接;所述NMOS管Mn2与所述多输入级电路中的 NMOS管Mn1形成电流镜电路,所述NMOS管Mn2的栅极与所述NMOS管Mn1的栅极相连,所述NMOS 管Mn2的源极连接至电源负端Vss;所述NMOS管Mn4与所述多输入级电路中的NMOS管Mn3形成 电流镜电路,所述NMOS管Mn4的栅极与所述NMOS管Mn3的栅极相连,所述NMOS管Mn4的源极连 接至电源负端Vss;所述PMOS管Mp11、Mp12、Mp13与所述NMOS管Mn5、Mn6形成一个一阶放大器 结构,所述PMOS管Mp11的栅极与所述偏置电路中的PMOS管Mp1的栅极相连形成电流源,所述 PMOS管Mp12、Mp13的栅极分别连接所述PMOS管Mp9、Mp10的漏极,所述PMOS管Mp12和Mp13的 源极相连并连接至所述PMOS管Mp11的漏极,所述PMOS管Mp12、Mp13的漏极分别与所述NMOS 管Mn5、Mn6的漏极连接;所述NMOS管Mn5和Mn6构成有源电流镜作为负载,所述NMOS管Mn5的 栅极与漏极短接后与所述NMOS管Mn6的栅极连接,所述NMOS管Mn5、Mn6的源极均连接至电源 负端Vss; 所述输出级电路包括PMOS管Mp14和NMOS管Mn7;所述PMOS管Mp14的栅极与所述偏 置电路中的PMOS管Mp1的栅极连接构成镜像电流源,所述PMOS管Mp14的源极与电源正端Vdd 连接,所述PMOS管Mp14的漏极与所述NMOS管Mn7的漏极连接;所述NMOS管Mn7的栅极与所述 NMOS管Mn6的漏极连接,所述NMOS管Mn7的源极连接至电源负端Vss;所述PMOS管Mp14的漏极 与所述NMOS管Mn7的漏极连接点作为所述六输入差分放大器电路的输出端Vout。 6 CN 111585531 A 说 明 书 3/9 页 优选地,所述六输入差分放大器电路还包括米勒补偿阻容电路; 所述米勒补偿阻容电路包括电阻R和电容C,所述电阻R和电容C串联连接在所述 PMOS管Mp13的栅极与所述六输入差分放大器电路的输出端Vout之间; 所述米勒补偿阻容电路为所述六输入差分放大器电路提供相位裕度补偿。 优选地,所述第一直流失调抑制电路和第二直流失调抑制电路均包括PMOS管M1、 PMOS管M2; 所述PMOS管M1的栅极和所述PMOS管M2的栅极相连,所述PMOS管M1的漏极和所述 PMOS管M2的漏极相连,所述PMOS管M1、M2的栅极连接点与所述PMOS管M1、M2的漏极连接点相 连;在所述第一直流失调抑制电路中所述PMOS管M1的源极和衬底短接后连接至所述外部信 号正差分输入端Vip,所述PMOS管M2的源极和衬底短接后连接至所述六输入差分放大器电 路的第一负输入端Vpn;在所述第二直流失调抑制电路中所述PMOS管M1的源极和衬底短接 后连接至所述外部信号负差分输入端Vin,所述PMOS管M2的源极衬底短接后连接至所述六 输入差分放大器电路的第二负输入端Vnn。 进一步地,所述第一直流失调抑制电路和第二直流失调抑制电路的高通截止频率 可调;所述第一直流失调抑制电路和第二直流失调抑制电路均包括PMOS管M1和PMOS管M2; 所述PMOS管M1的栅极和所述PMOS管M2的栅极短接并连接偏置电压Vb,所述PMOS管 M1和所述PMOS管M2的漏极相连,所述PMOS管M1与所述PMOS管M2的衬底连接在一起并连接至 所述PMOS管M1与所述PMOS管M2的漏极连接点;在所述第一直流失调抑制电路中所述PMOS管 M1的源极连接至所述外部信号正差分输入端Vip,所述PMOS管M2的源极连接至所述六输入 差分放大器电路的第一负输入端Vpn;在所述第二直流失调抑制电路中所述PMOS管M1的源 极连接至所述外部信号负差分输入端Vin,所述PMOS管M2的源极连接至所述六输入差分放 大器电路的第二负输入端Vnn;所述偏置电压Vb由偏置电压产生电路产生; 通过调节偏置电压Vb的大小,调节所述第一直流失调抑制电路和第二直流失调抑 制电路的高通截止频率。 优选地,所述的直流耦合差分前端放大器电路还包括第一快速恢复电路和第二快 速恢复电路; 所述第一快速恢复电路连接在所述直流耦合差分前端放大器电路的外部信号正 差分输入端Vip与所述六输入差分放大器电路的第一负输入端Vpn之间;所述第二快速恢复 电路连接在所述直流耦合差分前端放大器电路的外部信号负差分输入端Vin与所述六输入 差分放大器电路的第二负输入端Vnn之间; 所述第一快速恢复电路和第二快速恢复电路用于在外部信号输入导联线脱落并 重新连接的情形下,提高所述直流耦合差分前端放大器电路的响应速度。 优选地,所述第一快速恢复电路包括MOS管M3,所述第二快速恢复电路包括MOS管 M4; 所述MOS管M3的源极连接所述直流耦合差分前端放大器电路的外部信号负差分输 入端Vip,所述MOS管M3的漏极连接所述六输入差分放大器电路的第一负输入端Vpn;所述 MOS管M4的源极连接所述直流耦合差分前端放大器电路的外部信号负差分输入端Vin,所述 MOS管M4的漏极连接所述六输入差分放大器电路的第二负输入端Vnn;所述MOS管M3的栅极 和所述MOS管M4的栅极均由控制信号SW控制; 7 CN 111585531 A 说 明 书 4/9 页 在外部信号输入导联线脱落并重新连接时,所述控制信号SW控制所述MOS管M3和 所述MOS管M4导通,将外部信号低阻抗地输送到所述六输入差分放大器电路。 优选地,所述闭环增益电路为可变闭环增益电路,所述可变闭环增益电路为所述 直流耦合差分前端放大器电路提供可调节的闭环增益。 可选地,所述可变闭环增益电路包括可变电阻阵列网络Rf和固定电阻Rg; 所述固定电阻Rg一端与所述六输入差分放大器电路的负辅助输入端Vnx连接,所 述固定电阻Rg另一端与所述六输入差分放大器电路的输出端Vout连接;所述可变电阻阵列 网络Rf由多个不同阻值的电阻组成,所述多个不同阻值的电阻一端相连并连接共模电压 Vcm,所述多个不同阻值的电阻另一端经选择开关连接至所述固定电阻Rg与所述六输入差 分放大器电路的负辅助输入端Vnx的连接点;所述选择开关由数字控制电路控制; 所述数字控制电路通过控制选择开关选择所述可变电阻阵列网络Rf接入所述可 变闭环增益电路的阻值大小,使所述直流耦合差分前端放大器电路实现不同的闭环增益。 可选地,所述可变闭环增益电路包括固定电阻Rf和可变电阻Rg; 所述可变电阻Rg一端与所述六输入差分放大器电路的负辅助输入端Vnx连接,所 述可变电阻Rg另一端与所述六输入差分放大器电路的输出端Vout连接;所述固定电阻Rf一 端接收所述共模电压Vcm,所述固定电阻Rf另一端连接至所述可变电阻Rg与所述六输入差 分放大器电路的负辅助输入端Vnx的连接点; 通过改变所述可变电阻Rg接入所述可变闭环增益电路的阻值大小,使所述直流耦 合差分前端放大器电路实现不同的闭环增益。 实施本发明的技术方案,具有以下有益效果:本发明的电路具有一定的可调放大 倍数能力,可以提升微弱信号的传输信噪比。同时具有一定的电极极化失调电压抑制能力, 因而可以采用直流耦合输入而不会引起系统饱和失真。通过引入快速恢复电路,可以解决 在输入信号导联线脱落重新连接情形下,放大器响应速度很慢的问题。因此本发明可以有 效增强微弱生物电信号的传感采集效果。另外本发明的电路采用单运放结构,系统体积小, 功耗低,易于在标准CMOS工艺下集成和实现。 附图说明 下面将结合附图及实施例对本发明作进一步说明,附图中: 图1是本发明实施例一的结构示意图; 图2是本发明实施例二的结构示意图; 图3是本发明实施例中的直流失调抑制电路的一种电路原理图; 图4是发明实施例的一种电路原理图; 图5是本发明实施例中的六输入差分差值放大器电路的电路原理图。