技术摘要:

本发明公开了一种JTAG调试电路和计算机调试工具,JTAG调试电路包括如下部件:XDP,XDP的第一时钟输出接口连接到PCH的时钟接收接口,XDP的第二时钟输出接口连接到CPU的时钟接收接口,XDP的数据传输接口分别连接到PCH的数据传输接口和CPU的数据传输接口;BMC转换芯片,BM 全部

背景技术:

JTAG(Joint Test Action Group,联合测试工作组)是一种国际标准测试协议 (IEEE 1149 .1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如 CPU、PCH、BMC、CPLD器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时 钟、数据输入和数据输出线。 JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP (Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。JTAG测 试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。 在服务器设计中,JTAG还用于调试CPU和PCH,用于获取CPU和PCH内部的IO接口状 态、寄存器值、日志等信息,目前常见的调试方式有XDP debug、BMC remote debug以及PCH DCI debug。 在目前的服务器主板设计中,由于围绕CPU/PCH/BMC等芯片的JTAG拓扑过于复杂, 芯片boundary scan测试、XDP debug、BMC remote debug、PCH DCI debug等功能往往做部 分支持。基于调试的JTAG链路设计复杂,使用多个逻辑芯片进行切换,带来了额外的成本上 升。

技术实现要素:

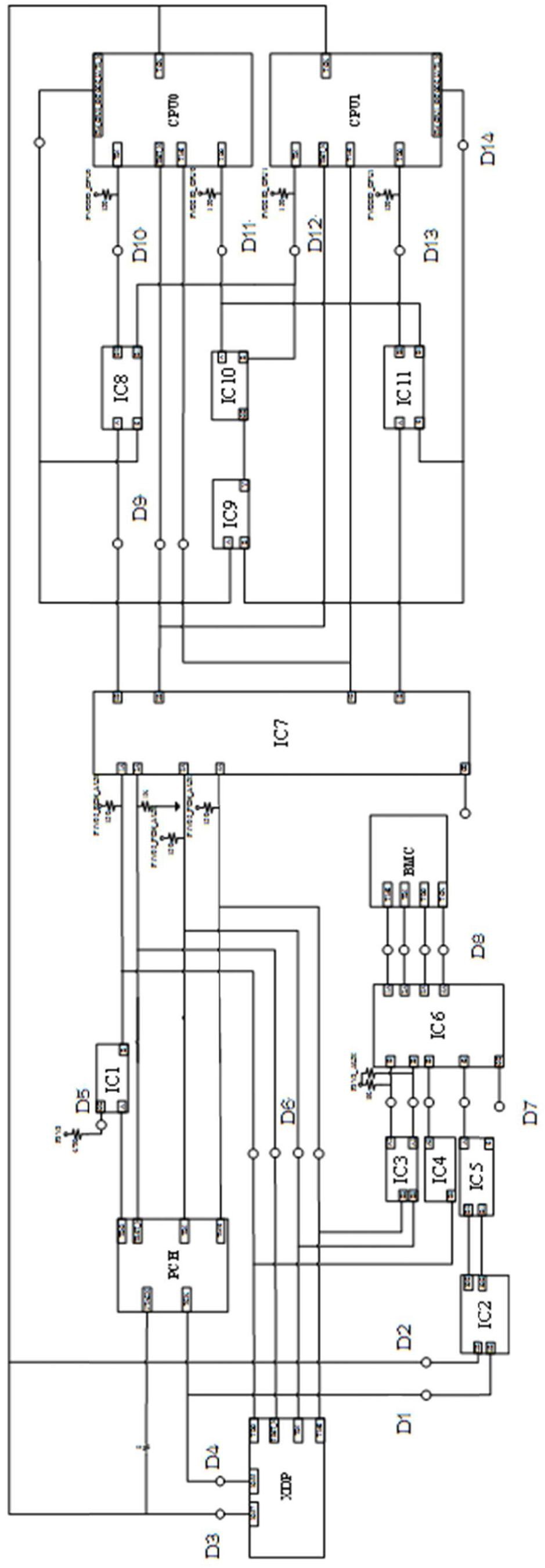

有鉴于此,本发明实施例的目的在于提出一种JTAG调试电路和计算机调试工具, 实现boundary scan、XDP debug、BMC remote debug、PCH DCI debug等功能的集成,提供了 多种研发端的调试模式,能够较大程度提高设计效率、降低产品不良率。 基于上述目的,本发明实施例的一方面提供了一种JTAG调试电路,包括如下部件: XDP,XDP的第一时钟输出接口连接到PCH的时钟接收接口,XDP的第二时钟输出接口连接到 CPU的时钟接收接口,XDP的数据传输接口分别连接到PCH的数据传输接口和CPU的数据传输 接口;BMC转换芯片,BMC转换芯片的第一时钟输出接口连接到PCH的时钟接收接口,BMC转换 芯片的第二时钟输出接口连接到CPU的时钟接收接口,BMC转换芯片的数据传输接口分别连 接到PCH的数据传输接口和CPU的数据传输接口;以及BMC,BMC的第一时钟输出接口连接到 BMC转换芯片的时钟接收接口,BMC的数据传输接口连接到BMC转换芯片的数据接收接口。 在一些实施方式中,PCH的第一时钟输出接口连接到CPU的时钟接收接口。 在一些实施方式中,还包括:第一使能芯片,第一使能芯片与PCH相连,以控制PCH 芯片状态。 在一些实施方式中,还包括:第二使能芯片,第二使能芯片一端与BMC转换芯片连 接,以控制BMC转换芯片的芯片状态。 4 CN 111722971 A 说 明 书 2/5 页 在一些实施方式中,CPU包括:CPU检测芯片,配置有CPU的数据传输接口,数据传输 接口连接第三使能芯片,以通过第三使能芯片控制CPU检测芯片的芯片状态;若干CPU芯片, 配置有CPU的时钟接收接口以接收时钟信号;CPU切换芯片,连接在CPU检测芯片和若干CPU 芯片之间,以动态连接CPU并进行数据传输。 本发明实施例的另一方面,还提供了一种计算机调试工具,包括JTAG调试电路, JTAG调试电路包括:XDP,XDP的第一时钟输出接口连接到PCH的时钟接收接口,XDP的第二时 钟输出接口连接到CPU的时钟接收接口,XDP的数据传输接口分别连接到PCH的数据传输接 口和CPU的数据传输接口;BMC转换芯片,BMC转换芯片的第一时钟输出接口连接到PCH的时 钟接收接口,BMC转换芯片的第二时钟输出接口连接到CPU的时钟接收接口,BMC转换芯片的 数据传输接口分别连接到PCH的数据传输接口和CPU的数据传输接口;以及BMC,BMC的第一 时钟输出接口连接到BMC转换芯片的时钟接收接口,BMC的数据传输接口连接到BMC转换芯 片的数据接收接口。 在一些实施方式中,PCH的第一时钟输出接口连接到CPU的时钟接收接口。 在一些实施方式中,JTAG调试电路还包括:第一使能芯片,第一使能芯片与PCH相 连,以控制PCH芯片状态。 在一些实施方式中,JTAG调试电路还包括:第二使能芯片,第二使能芯片一端与 BMC转换芯片连接,以控制BMC转换芯片的芯片状态。 在一些实施方式中,CPU包括:CPU检测芯片,配置有CPU的数据传输接口,数据传输 接口连接第三使能芯片,以通过第三使能芯片控制CPU检测芯片的芯片状态;若干CPU芯片, 配置有CPU的时钟接收接口以接收时钟信号;CPU切换芯片,连接在CPU检测芯片和若干CPU 芯片之间,以动态连接CPU并进行数据传输。 本发明具有以下有益技术效果:实现boundary scan、XDP debug、BMC remote debug、PCH DCI debug等功能的集成,提供了多种研发端的调试模式,能够较大程度提高设 计效率、降低产品不良率。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本 发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以 根据这些附图获得其他的实施例。 图1为本发明提供的JTAG调试电路的实施例的示意图。