技术摘要:

本发明公开了一种基于阻变存储器的物理不可克隆函数电路结构,主要包括PUF控制逻辑模块、m行*n列的RRAM存储单元、m条字线、n条位线、n条源线、n个灵敏放大器、n个异或门和n个D触发器,其中每个RRAM存储单元由N型晶体管和阻变存储单元组成;PUF控制逻辑模块接收外部激励 全部

背景技术:

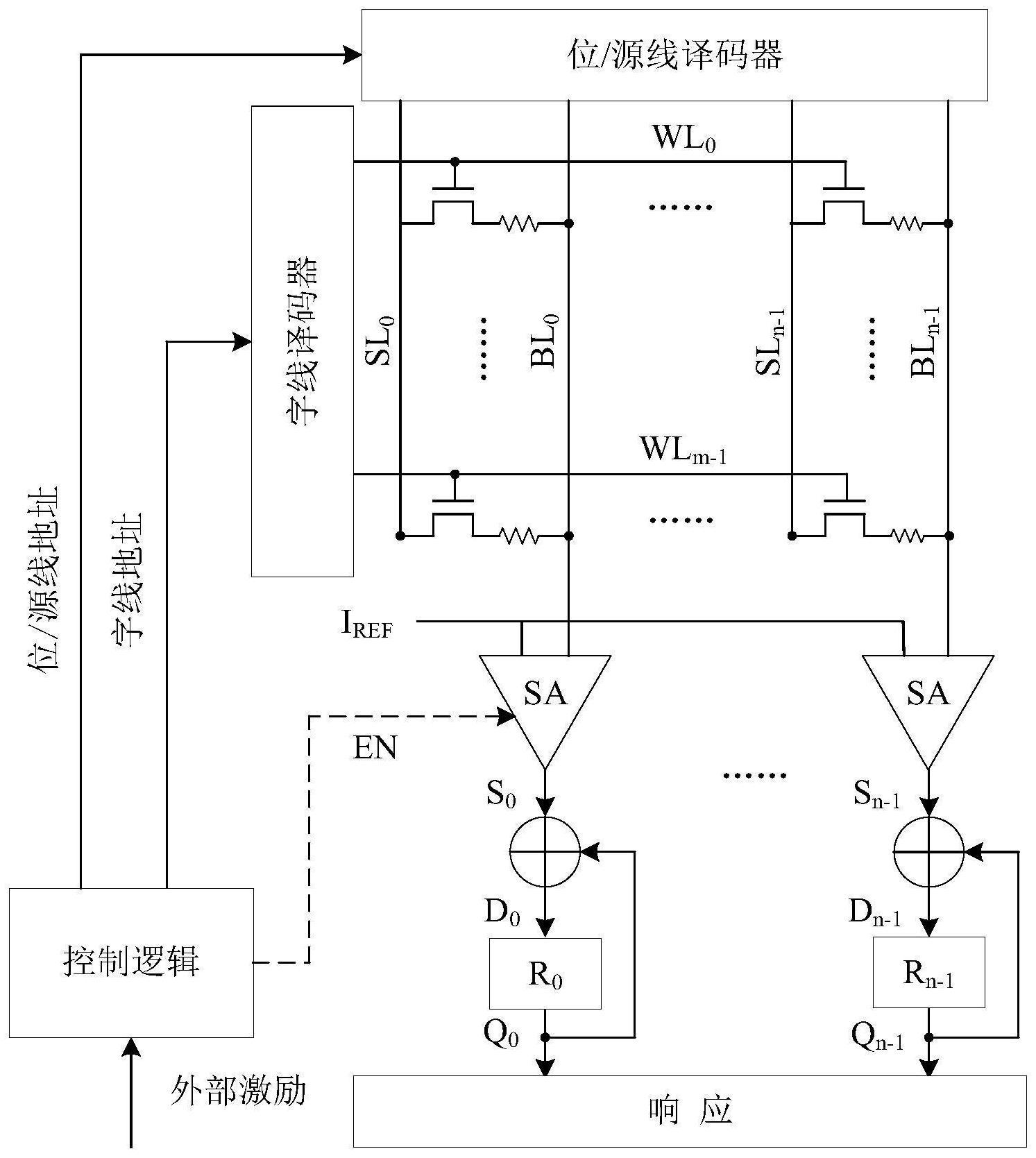

随着物联网技术的飞速发展,各种无线便携式设备开始广泛应用,由于这些设备 通信是通过无线空中接口实现的,通信内容很容易被第三方窃听、拦截以及篡改,无线设备 安全保护成为了当前亟待解决的问题。如DES、RC5等传统加密算法需要将密钥保存于非易 失性存储中,容易受到侵入式攻击导致密钥被获取,而物理不可克隆函数(Physical Unclonable Function,缩写为PUF)的实现为解决该问题提供了新的思路,PUF利用物理实 体在制造过程不可避免的工艺偏差或自身的物理特性而产生自身的唯一性标识,使得对其 输入任何激励都会产生一个唯一且不可预测的响应。 基于阻变存储器(Resistive Random Access Memory,缩写为RRAM)器件在擦写时 的独特物理特性,两个金属电极间由含氧空位构成的导电丝会进行可逆地断裂和生长,由 于含氧空位每次产生和消失具有随机性,所以在不同RRAM单元甚至同一RRAM单元的不同擦 写周期内,导电丝的形状和大小都是随机变化的,从而导致阻值的随机变化。而不同RRAM单 元器件在每次擦写后形成的随机电阻分布可作为PUF的熵源,与其他类型的PUF相比,RRAM 具有单元结构小、可重构等优点。在RRAM电路中,受到存储单元存储机理的影响,RRAM的写 入操作分为三种情况:forming、reset、set。forming操作即初始化激活存储单元的过程,一 般初始化过程中需要对新制备的RRAM器件施加一个较大的forming电压,使得器件内部形 成稳定的导电通路,随后器件阻值可以在高电阻状态与低电阻状态间进行可逆地转换; reset即复位写0操作,具体为对RRAM器件施加reset电压,使得器件电阻由低阻态转变为高 阻态;set即置位写1操作,具体为对RRAM器件施加set电压,使得器件电阻由高阻态转变为 低阻态。 如图1所示为现有技术中基于RRAM的传统弱PUF主要电路结构示意图,图1中PUF在 工作时利用挑战(challenge)输入作为RRAM单元的地址信号,并选中RRAM单元进行读取,具 体为将RRAM单元的读出电流IR与参考电流IREF进行比较,最后通过灵敏放大器输出1bit的 PUF响应,当需要产生N个PUF响应时则需要重复N次操作,该结构受到RRAM单元数量的限制, 只能产生有限的挑战响应对(Challenge Response Pairs,缩写为CRPs),是一种典型的弱 PUF电路。如图2所示为现有技术中基于RRAM的传统强PUF主要电路结构示意图,图2中的PUF 在工作时,通过将挑战作为地址选中两个RRAM单元R1和R2,并对它们的读出电流IR1和IR2进 行比较,通过灵敏放大器输出1bit的PUF响应,当需要产生N个PUF响应时则需要重复N次该 操作,由于实现方式的差别使得该结构可以产生大量的CRPs,是一种典型的强PUF电路。但 对于上述现有技术的两种电路结构进行分析,不难发现一方面上述结构产生PUF响应的效 率十分低下,另一方面当需要产生多位的PUF响应时,则需要较多的PUF挑战位,导致适用于 无线传输领域的通信过程中出现误码的概率将会增加,因此需要一种更高效、挑战响应空 3 CN 111581675 A 说 明 书 2/5 页 间大且实用性更强的PUF电路结构。

技术实现要素:

本发明的目的是提供一种基于阻变存储器的物理不可克隆函数电路结构,基于该 电路结构的PUF拥有极大的挑战响应空间和较高的响应计算效率,具有很高的实用性。 本发明的目的是通过以下技术方案实现的: 一种基于阻变存储器的物理不可克隆函数电路结构,所述电路结构包括物理不可 克隆函数PUF控制逻辑模块、m行*n列的阻变存储器RRAM存储单元、m条字线、n条位线、n条源 线、n个灵敏放大器、n个异或门和n个D触发器,其中: 每个RRAM存储单元由一个N型晶体管和一个阻变存储单元组成,m行*n列的RRAM存 储单元的字/位/源线译码器分别有m和n位输出端,m和n位输出端分别接WL0~m-1/BL0~n-1/ SL0~n-1; 所述PUF控制逻辑模块接收主系统的外部激励信号,根据外部激励信号生成RRAM 存储单元的译码器控制信号、地址和其它读/写控制信号,并完成RRAM存储单元的配置、读/ 写、PUF响应计算功能; 每个RRAM存储单元分别具有字线端WL、位线端BL和源线端SL;其中位于第i行第j 列的RRAM存储单元的字线端连接WLi,位线端连接BLj,源线端连接SLj,i=0,1,2,...m-1;j =0,1,2,...n-1; 每个灵敏放大器分别具有输入端1、输入端2、使能端和输出端,其中第j列的灵敏 放大器的输入端1接BLj,输入端2接参考电流IREF,使能端连接所述PUF控制逻辑模块产生的 EN信号,输出端为Sj; 每个异或门包括输入端1、输入端2和输出端,其中第j个异或门输入端1接Sj,输入 端2接Qj,输出端接Dj; 每个D触发器包括时钟端、复位端、输入端和输出端,其中第j个D触发器的时钟端、 复位端接统一的时钟和复位信号;输入端接信号Dj;输出端输出信号Qj,生成PUF响应。 由上述本发明提供的技术方案可以看出,相对于传统的实现方式,本发明的技术 方案可以大幅扩展PUF的挑战响应空间,并显著减少了读操作的次数,提高了PUF响应的计 算效率,具有很高的实用性。 附图说明 为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用 的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本 领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他 附图。 图1为现有技术中基于RRAM的传统弱PUF主要电路结构示意图; 图2为现有技术中基于RRAM的传统强PUF主要电路结构示意图; 图3为本发明实施例所述基于阻变存储器的物理不可克隆函数电路结构示意图。 4 CN 111581675 A 说 明 书 3/5 页