技术摘要:

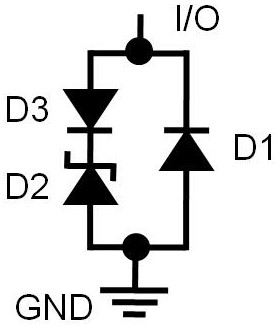

一种静电防护阵列芯片及其加工方法,本发明涉及芯片技术领域;它包含下管、上管、二极管;下管、上管以及二极管三者之间串并联后接地,同时与输入输出端连接。其简化芯粒数量,减少芯片面积,降低芯片总电容值,降低生产成本,实用性更强。

背景技术:

在半导体静电防护技术领域中,简化芯粒数量、减少芯片面积,降低芯片总电容值 一直是业界追求的目标。对于日趋小型化及节约成本和应对高速数据传输的需求,简化芯 粒数量、减少芯片面积,降低芯片总电容值成为是关键因素。 单PN结的静电防器件即瞬态电压抑制二极管可有效的抑制静电冲击,但因结电容 过大容易导致高速数据传输线上的数据丢失;因此通常会在瞬态电压抑制二极管上串接一 个小电容二极管来降低静电防护线路上的总电容;这样线路也相应的变得繁杂。 为了解决上述技术问题,有必要提出一种新的静电防护阵列芯片的设计方法及静 电防护阵列芯片。

技术实现要素:

本发明的目的在于针对现有技术的缺陷和不足,提供一种结构简单,设计合理、使 用方便的静电防护阵列芯片及其加工方法,其简化芯粒数量,减少芯片面积,降低芯片总电 容值,降低生产成本,实用性更强。 为实现上述目的,本发明采用的技术方案是:它包含下管、上管、二极管;下管、上 管以及二极管三者之间串并联后接地,同时与输入输出端连接。 进一步地,所述的下管为开关二极管。 进一步地,所述的二极管为瞬态电压抑制二极管。 进一步地,所述的上管为开关二极管。 本发明的加工步骤如下: 1、基于P型衬底硅片进行N型外延生长,形成N型外延层; 2、在N型外延层的左右两侧选出相对面积并下挖一定深度,然后进行N型埋层; 3、在N型埋层上进行扩散,形成P型扩散层和N型扩散层,在N型外延层的中部上进行扩 散,形成N型扩散层; 4、基于上述步骤2,在N型外延层的中部左右两侧选出的相对面积,挖两条至P型衬底硅 片的沟槽并填入隔离材料;于此,由P型衬底硅片和N型外延层的中部形成下管,以达成该静 电防护阵列芯片所需的小电容值之一及总正向压降;由P型衬底硅片、N型外延层的左右两 侧部分和N型埋层组成瞬态电压抑制二极管,以达成该静电防护阵列芯片所需要反向击穿 电压;由N型外延层的左右两侧部分、N型埋层和P型扩散层组成上管,以达成该静电防护阵 列芯片所需的小电容值之一及通流能力;而N型扩散层则起到了避免闩锁效应的作用; 5、在N型外延层、N型埋层、P型扩散层、N型扩散层及沟槽的相应顶部均覆盖氧化层,以 消除芯片表面电荷,降低该静电防护阵列芯片的漏电流; 6、在氧化层及未覆盖氧化层的顶部覆盖芯片正面金属,作为该静电防护阵列芯片后续 3 CN 111613615 A 说 明 书 2/3 页 封装的联接介面; 7、在芯片正面金属上除联接介面部分的顶部覆盖钝化层,以隔离外界对该静电防护阵 列芯片敏感区域的污染和干扰; 8、将P型衬底硅片的背面减薄并覆盖金属化层,以达成该静电防护阵列芯片后续封装 所需的厚度及金属层。 采用上述结构后,本发明有益效果为:本发明所述的一种静电防护阵列芯片及其 加工方法,其简化芯粒数量,减少芯片面积,降低芯片总电容值,降低生产成本,实用性更 强,本发明具有结构简单,设置合理,制作成本低等优点。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本 发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以 根据这些附图获得其他的附图。 图1是本发明的电路连接图。 图2是本发明的结构层次图。 附图标记说明: 下管D1、二极管D2、上管D3、P型衬底硅片101、N型外延层102、N型埋层103、P型扩散层 104、N型扩散层105、沟槽106、氧化层107、芯片正面金属108、钝化层109、金属化层110。