技术摘要:

本发明公开了一种基于高速异步逻辑的PVT自校准方法及其SAR ADC电路。PVT自校准方法通过对高速异步延时链的选择,以较小的面积和功耗代价来量化当前电路处于的PVT状态信息,从系统量化的角度,根据量化得到的PVT量化码来校准芯片偏置电路产生恒定的电流、控制关键模拟电 全部

背景技术:

不同的晶片和不同的批次之间,因为半导体制成工艺中掺杂、刻蚀、温度等外界因 素导致MOSFETs参数的变化范围比较大,即为工艺涨落。同时电路工作处在的温度和电压也 会对电路的功能和性能产生影响。通常一般电路在设计时留出足够的余量使得电路在所有 工艺-温度-电压组合下实现功能和性能,而这往往会造成功耗等资源的浪费。 ADC是模拟信号实现数字量化的转换系统,是连接数字处理与模拟世界的接口,其 性能至关重要。SAR ADC因结构简单、功耗低并且与易与数字电路兼容的优点,被广泛应用 于低功耗电子设备中。 虽然SAR ADC中受工艺影响大的模拟模块较少,业界认为SAR ADC具有优良的鲁棒 性,但高速SAR ADC受PVT影响大。一般高速SAR ADC采用内部“延时”和反馈来实现比较器时 钟的产生,而片上延时受工艺-电压-温度影响很大,即高速异步时钟对PVT高度敏感,在ss/ 低电压工艺角小相同尺寸延时单元延时最大,电容上电压置位建立时间也最长,ADC的转换 速度和精度受限。 通常系统内部留出足够的时间余量使ADC高位电压有较高的建立精度。高速SAR ADC 的PVT鲁棒性常被忽视,专门为抗PVT的高速低功耗高性能SAR ADC的设计并不多见。一 般的高速低功耗高性能SAR ADC对外预留多个调试管脚,通过外部器件或信号的调整来进 行修调和测试,而非内部自校准来达到最优的性能。同时,目前对于PVT的校准往往只针对 单一电路,难以做到PVT共享检测与校准,暂未有从量化PVT量化码的角度对系统进行全局 校准的方案。

技术实现要素:

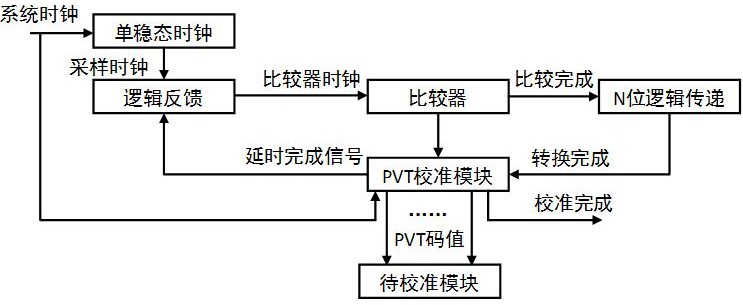

为了克服现有技术的不足,本发明的目的是提供一种基于高速异步逻辑的PVT自 校准方法及其SAR ADC电路。 一种基于高速异步逻辑的PVT自校准方法, 1)由多组且不同长短的延时链单元构成高速异步SAR逻辑,延时链包括标准延时 单元和多个带有选通控制端的数据选择器级联,选通控制端由自校准电路控制; 2)从高速异步逻辑上电后进入长度为m个周期的空循环,在第m 1个转换周期开 始,持续检测高速异步逻辑是否出现转换完成信号; 3)若检测到转换完成信号,则延时链固定,自校准电路进入休眠,若没有检测到转 换完成信号,则自校准电路改变数据选择器选通控制端的码值,逐步缩短下一个周期延时 链的长度,即自主从大延时向小延时调整,直至调整到合适的延时后延时链长短固定并且 自校准电路进入休眠模式; 4 CN 111740739 A 说 明 书 2/7 页 4)固定的延时链中的多个选择器控制端码值包含与延时有关且反映出的延时链 当前状态的 PVT信息,将PVT量化码通过锁存器进行存储,通过译码器进行数据处理,通过 缓冲器将 PVT状态传输到对PVT敏感且待校准的电路; 5)待校准的电路根据得到的PVT量化码进行校准,如调制电阻校准偏置电流和调 制衬底校准; 6)在接受到有效PVT量化码后,分配q个时钟周期时间用于调整待校准的电路自校 准,待校准电路自校准结束后产生校准完成信号,标志整个自校准完成,此后缓冲器、译码 器、锁存器均进入休眠。 所述的方法,当高速异步逻辑工作一段时间后,通过外部使能启动校准信号暂停 高速异步逻辑工作,使自校准电路脱离休眠模式进入自校准模式,进行PVT自校准。 所述的方法,采用自校准PVT模块,包括 1)用于高速异步时序且长短不同的延时链,由多个标准延时单元和多个带有选通 端的数据选择器级联组成,上电后默认延时链为最长; 2)延时检测模块,能在上电后检测时期持续检测每个周期是否产生转换完成标志 信号; 3)延时链调整模块,根据校准开启信号和延时检测模块产生的使能信号以及系统 总时钟触发依次从高到低调整延时链选择器选择端的控制信号,在校准结束后能自动进入 休眠低功耗状态,同时可以等待重启校准信号唤醒; 4)量化码锁存和传输模块,由多个锁存器和驱动Buffer组成,能在校准完成且PVT 量化码固定后,对量化码进行锁存和传输; 5)自校准偏置电路,由constant gm型自偏置电流产生电路和电阻调整网络DAC组 成,其中DAC由经过锁存驱动的PVT量化码控制; 6)自校准衬底调制电路,由电阻调整网络DAC组成,其中DAC由经过锁存驱动的PVT 量化码控制。 7)系统PVT调制电路,根据PVT量化码进行调制。 一种采用了所述方法的抗PVT涨落的SAR ADC电路,包括: 采样开关,由自举电容、输入管和自举时钟控制电路组成,对输入信号进行采样; CDAC电路,由带多个冗余位的呈二进制排列的电容阵列和开关组成,利用电容间 电荷再分配完成二进制搜索算法; 动态比较器,由预放大器和再生锁存器组成,用于比较差分模拟输入信号的大小, 输出二进制数字信号,完成量化; SAR逻辑,异步时钟发生电路、采样时钟发生电路和数据传输窗口电路组成,根据 比较器的输出结果来控制信号切换电容阵列; 自校准PVT模块,由延时链、延时检测模块、延时链调整模块、量化码锁存和传输模 块、自校准偏置电路、自校准衬底调制电路和系统PVT调制电路组成,上电后检测当前电路 处在状态,量化PVT码,并对系统进行抗PVT的校准; 转码输出电路,完成对冗余位进行转换并缓冲输出量化码; 其中自校准PVT模块能根据量化得的PVT量化码调制动态比较器中预放大器尾电 流的偏置电流,补偿Cascode放大器尾电流管随PVT的较大变化,使预放大器增益AV和带宽 5 CN 111740739 A 说 明 书 3/7 页 Bw 的稳定,提高动态比较器的速度和降低噪声;自校准PVT模块输出的码值调制动态比较 器中再生锁存器的衬底电位,提高再生锁存器的速度,且则动态比较器尾电流管由于衬底 电位升高而Itail增加,动态比较器输入管偏置于亚阈值区,则输入管gm增加,使得比较器 噪声减小。 本发明的有益效果为: 针对高速异步SAR比较器时钟产生原理,将内部总延时拆成多个延时单元和多个 选择器级联的方式,配合自校准PVT算法电路实现对电路当前状态PVT的码值量化,并将该 量化码进行存储、传输和处理,通过电阻DAC网络对PVT敏感电路进行电压或电流的校准。该 方案在维持传统SAR ADC的简单架构的基础上,具有很强的抗PVT涨落的能力。采用 SMIC 40nm CMOS工艺进行仿真验证,以差分输入电压为2.0Vpp为例,本发明改进型SAR ADC电路 采样率80MS/s,全工艺角(tt、ss、ff、sf、fs)、正负10%电压、宽温度(-40°~125°) 范围下 均能达到有效位数大于11.50bit,动态杂散范围小于-78.5dB,最大功耗小于2.4mW 的性 能,具有很强的抗PVT的能力。仿真结果表明,在不增加额外芯片管脚面积和维护成本的条 件下,带PVT自校准的SAR ADC的最差有效位数从11 .60bits提高到11 .67bits,3 σ从 0.22bits降低至0.17bits,鲁棒性提高了22%,验证了该算法的可行性和有效性。 附图说明 图1是基于新型PVT校准算法的一种高速异步SAR时钟发生电路框图; 图2是基于SAR异步时钟的新型PVT校准算法的流程图; 图3是PVT自校准控制电路的一种信号时序图; 图4是自校准PVT模块结构框图; 图5是自校准偏置电路, 其中(a)是延时单元电路图,延时单位由偶数个级联的反相器构成,(b)是反相器 下降时间等效电路图; 图6是自校准偏置电流电路图; 图7是自校准衬底调制电路图; 图8是具有PVT自校准的SAR ADC电路的一种结构图; 其中,1是采样开关、2是CDAC电路、3是动态比较器、4是SAR逻辑、5是转码输出电 路、6是自校准PVT模块; 图9是预放大器增益带宽积GBW蒙特卡洛仿真结果图; 图10是动态比较器传播延时蒙特卡洛仿真结果图; 图11是整体比较器输入等效噪声蒙特卡洛仿真结果图; 图12是PVT自校准SAR ADC有效位数仿真结果图; 图13是在典型情况下PVT自校准SAR ADC的仿真结果频谱图。