技术摘要:

本发明涉及半导体装置及半导体电路。实施方式的半导体装置具备半导体层,该半导体层具有第1面及第2面,从第1面侧向第2面侧依次具有第1导电型的第1半导体区域、第2导电型的第2半导体区域、与第2半导体区域相比第2导电型杂质浓度较高的第2导电型的第3半导体区域、第1导电 全部

背景技术:

作为功率用半导体装置的一例,有Insulated Gate Bipolar Transistor(IGBT: 绝缘栅双极型晶体管)。IGBT例如在集电极电极上设有p型的集电极区域、n型的漂移区域、p 型的基体(base)区域。并且,在将p型的基体区域贯通并到达n型的漂移区域的沟槽内,将栅 极绝缘膜夹在之间地设有栅极电极。进而,在p型的基体区域表面的与沟槽邻接的区域,设 有与发射极电极连接的n型的发射极区域。 IGBT中,通过对栅极电极施加阈值电压以上的正电压,从而在p型的基体区域形成 沟道。并且,在从n型的发射极区域向n型的漂移区域注入电子的同时,从集电极区域向n型 的漂移区域注入空穴。由此,在集电极电极与发射极电极间流过以电子和空穴为载流子的 电流。 为了降低IGBT的导通电阻,增大导通状态的n型的漂移区域的载流子浓度是有效 的。另一方面,当IGBT关断时,如果n型的漂移区域的载流子的排出变慢,则关断时间变长, 开关损耗增大。 作为兼顾导通电阻的降低和开关损耗的降低的方法,提出了双栅极驱动。双栅极 驱动是通过使栅极的驱动系统为两个系统并改变两个栅极的驱动定时、从而缩短IGBT的开 关时间并降低开关损耗的技术。因而,能够兼顾导通电阻的降低和开关损耗的降低。

技术实现要素:

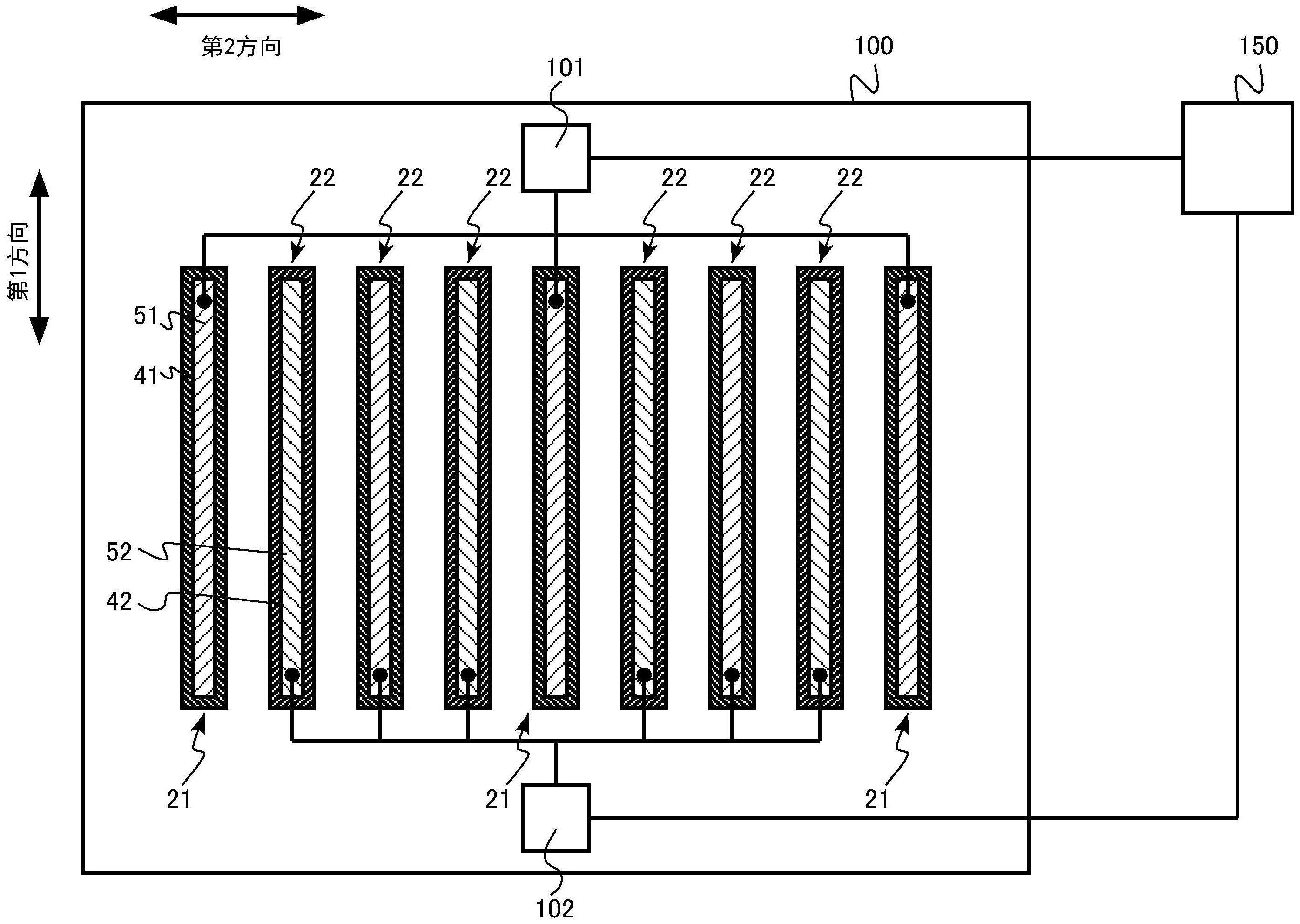

实施方式提供能够降低开关损耗的半导体装置及半导体电路。 实施方式的半导体装置具备: 半导体层,具有第1面及与上述第1面对置的第2面,并且具有:第1导电型的第1半 导体区域;第2导电型的第2半导体区域,设在上述第1半导体区域与上述第1面之间;第2导 电型的第3半导体区域,设在上述第2半导体区域与上述第1面之间,与上述第2半导体区域 相比,第2导电型杂质浓度较高;第1导电型的第4半导体区域,设在上述第3半导体区域与上 述第1面之间;第2导电型的第5半导体区域,设在上述第4半导体区域与上述第1面之间;第1 沟槽,设在上述第1面侧,距上述第2面的第1距离小于从上述第2面到上述第4半导体区域的 距离;以及第2沟槽,设在上述第1面侧,距上述第2面的第2距离小于从上述第2面到上述第4 半导体区域的距离; 第1栅极电极,设在上述第1沟槽之中; 第1栅极绝缘膜,设在上述第1栅极电极与上述第4半导体区域之间、上述第1栅极 5 CN 111725310 A 说 明 书 2/13 页 电极与上述第5半导体区域之间,与上述第5半导体区域相接; 第2栅极电极,设在上述第2沟槽之中; 第2栅极绝缘膜,设在上述第2栅极电极与上述第3半导体区域之间、上述第2栅极 电极与上述第4半导体区域之间; 第1电极,设在上述半导体层的上述第1面侧,与上述第5半导体区域电连接; 第2电极,设在上述半导体层的上述第2面侧,与上述第1半导体区域电连接; 第1栅极电极焊盘,设在上述半导体层的上述第1面侧,与上述第1栅极电极电连 接,被施加第1栅极电压;以及 第2栅极电极焊盘,设在上述半导体层的上述第1面侧,与上述第2栅极电极电连 接,被施加第2栅极电压。 附图说明 图1是第1实施方式的半导体电路的示意图。 图2是第1实施方式的半导体装置的一部分的示意截面图。 图3是第1实施方式的半导体装置的一部分的示意上表面图。 图4是第1实施方式的半导体装置的驱动方法的说明图。 图5是比较例的半导体装置的示意图。 图6是第2实施方式的半导体装置的一部分的示意截面图。 图7是第3实施方式的半导体装置的一部分的示意截面图。 图8是第4实施方式的半导体装置的一部分的示意截面图。 图9是第5实施方式的半导体装置的一部分的示意截面图。 图10是第6实施方式的半导体装置的一部分的示意截面图。 图11是第7实施方式的半导体装置的一部分的示意截面图。 图12是第8实施方式的半导体装置的一部分的示意截面图。 图13是第9实施方式的半导体装置的一部分的示意截面图。