技术摘要:

本发明属于数据传输技术领域,特别涉及一种基于FPGA的网络安全加速卡及加速方法。本发明提供一种新的基于FPGA的网络安全加速卡及加速方法,该基于FPGA的网络安全加速卡及加速方法采用是经典的五元组精确匹配的流转发方式来处理网络报文,可以对处理器进行网络处理的分 全部

背景技术:

随着全球大数据以及人工智能技术的高速发展,对于网络性能越来越高,从原来 的百兆、千兆的吞吐量迅速增长到现在的10G、25G、40G甚至100G、200G等等吞吐量。外部带 宽很高,但同时对服务器的处理器处理能力带来了前所未有的挑战,单靠处理器来进行网 络处理是无法完全满足需求的,网络性能问题甚至成了制约功能进一步丰富完善的瓶颈。

技术实现要素:

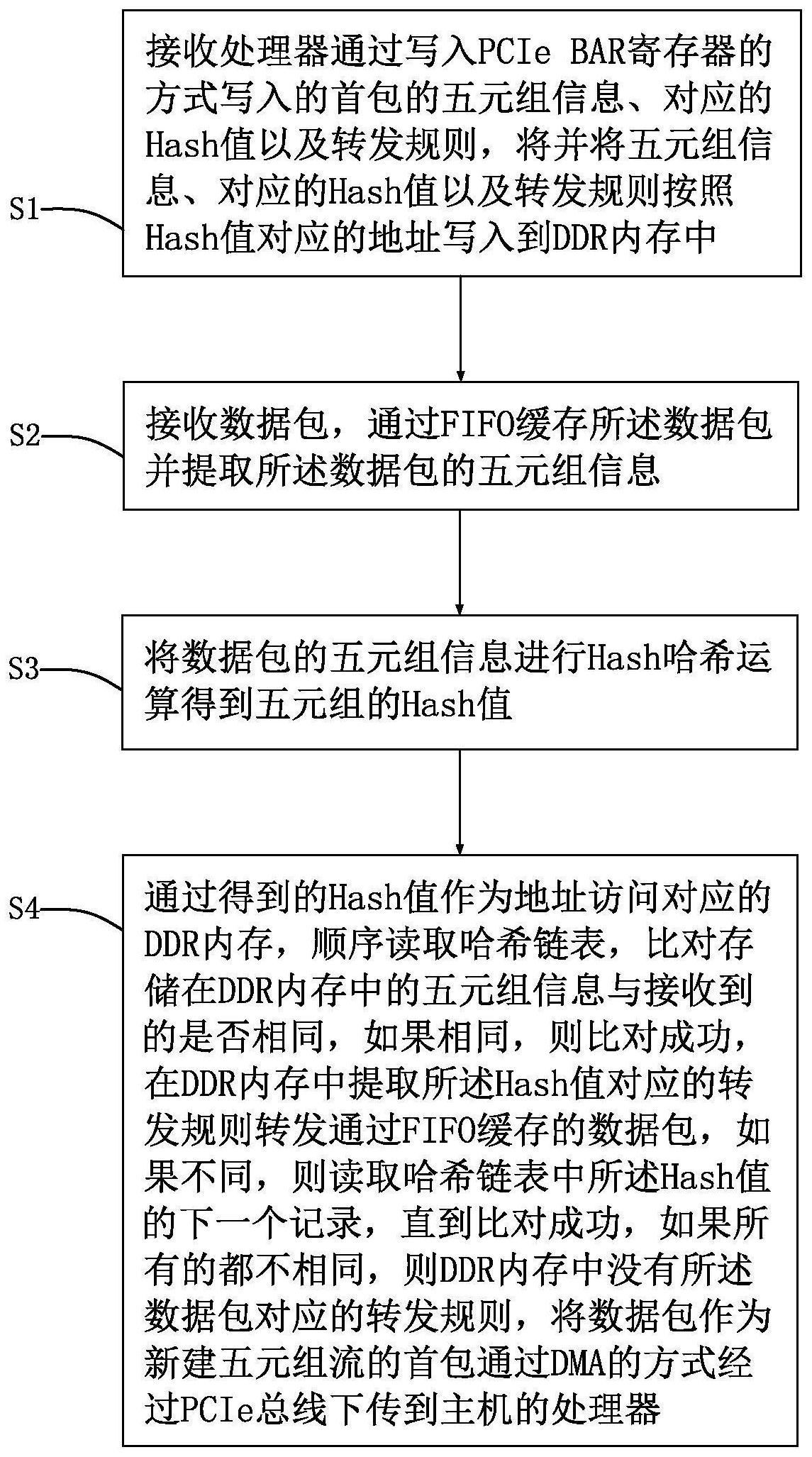

为了解决现有技术中存在的问题,本发明提供一种新的基于FPGA的网络安全加速 卡及加速方法。 本发明具体技术方案如下: 本发明提供一种基于FPGA的网络安全加速方法,包括如下步骤: S1:接收处理器通过写入PCIe BAR寄存器的方式写入的首包的五元组信息、对应 的Hash值以及转发规则,将并将五元组信息、对应的Hash值以及转发规则按照Hash值对应 的地址写入到DDR内存中,所述转发规则包括安全策略、路由信息和处理策略; S2:接收数据包,通过FIFO缓存所述数据包并提取所述数据包的五元组信息; S3:将数据包的五元组信息进行Hash哈希运算得到五元组的Hash值; S4:通过得到的Hash值作为地址访问对应的DDR内存,顺序读取哈希链表,比对存 储在DDR内存中的五元组信息与接收到的是否相同,如果相同,则比对成功,在DDR内存中提 取所述Hash值对应的转发规则转发通过FIFO缓存的数据包,如果不同,则读取哈希链表中 所述Hash值的下一个记录,直到比对成功,如果所有的都不相同,则DDR内存中没有所述数 据包对应的转发规则,将数据包作为新建五元组流的首包通过DMA的方式经过PCIe总线下 传到主机的处理器。 一种基于FPGA的网络安全加速卡,包括如下部分: 信息写入模块,被配置为接收处理器通过写入PCIe BAR寄存器的方式写入的首包 的五元组信息、对应的Hash值以及转发规则,将并将五元组信息、对应的Hash值以及转发规 则按照Hash值对应的地址写入到DDR内存中,所述转发规则包括安全策略、路由信息和处理 策略; 提取模块,被配置为接收数据包,通过FIFO缓存所述数据包并提取所述数据包的 五元组信息; 哈希运算模块,被配置为将数据包的五元组信息进行Hash哈希运算得到五元组的 Hash值; 数据处理模块,被配置为通过得到的Hash值作为地址访问对应的DDR内存,顺序读 5 CN 111597142 A 说 明 书 2/8 页 取哈希链表,比对存储在DDR内存中的五元组信息与接收到的是否相同,如果相同,则比对 成功,在DDR内存中提取所述Hash值对应的转发规则转发通过FIFO缓存的数据包,如果不 同,则读取哈希链表中所述Hash值的下一个记录,直到比对成功,如果所有的都不相同,则 DDR内存中没有所述数据包对应的转发规则,将数据包作为新建五元组流的首包通过DMA的 方式经过PCIe总线下传到主机的处理器。 本发明的有益效果如下: 本发明提供一种新的基于FPGA的网络安全加速卡及加速方法,该基于FPGA的网络 安全加速卡及加速方法采用是经典的五元组精确匹配的流转发方式来处理网络报文,可以 对处理器进行网络处理的分流,使处理器能从繁重的工作中解放出来,处理一些必须它来 做的事情,可以进一步提高数据的转发速率。 附图说明 图1为实施例1基于FPGA的网络安全加速方法的流程图; 图2为实施例1基于FPGA的网络安全加速方法的示意图; 图3为实施例1步骤S2的流程图; 图4为实施例1步骤S22的流程图; 图5为实施例2基于FPGA的网络安全加速卡的结构框图; 图6为实施例2提取模块的结构框图; 图7为实施例2提取单元的结构框图。