技术摘要:

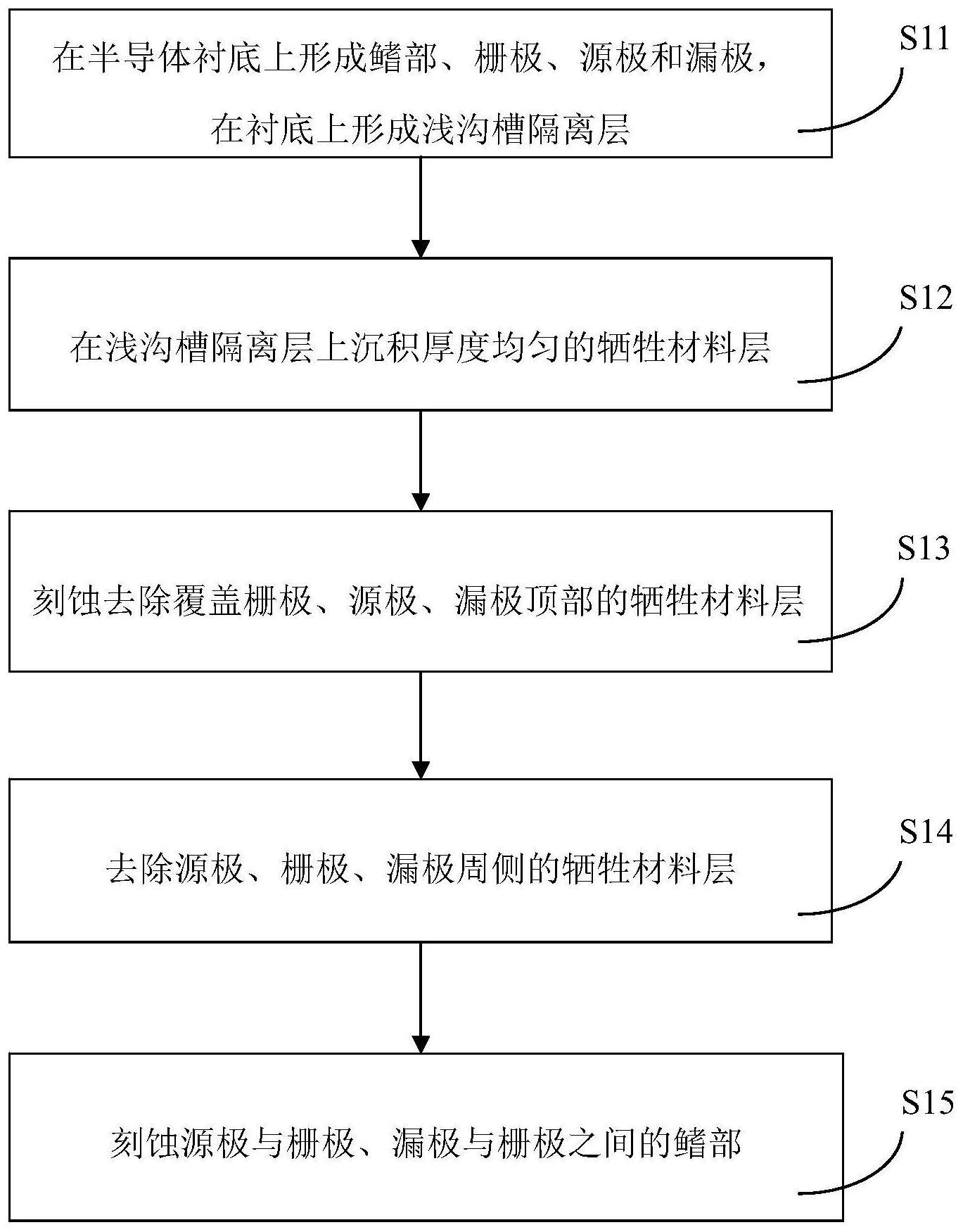

本发明公开了一种场效应管的形成方法,包括提供半导体衬底,在半导体衬底上形成鳍部、栅极、源极和漏极,并在衬底上形成浅沟槽隔离层;在浅沟槽隔离层上沉积厚度均匀的牺牲材料层;刻蚀去除覆盖栅极、源极和漏极顶部的牺牲材料层;去除源极、栅极、漏极周侧的牺牲材料 全部

背景技术:

为了跟上摩根定律的脚步,集成电路器件的尺寸正在不断减小,以达到高器件密 度、 高性能、低成本的要求。比如二极管、三极管等,在器件尺寸减小的同时,器件源极和漏 极的距离也在缩短。由此导致栅极对沟道的控制能力变差,容易产生短沟道效应。 为了抑制短沟道效应,立体场效应管逐渐占领舞台,例如鳍式场效应管(FinFET)。 与平面型场效应管相比,FinFET的栅极对沟道的控制能力更强,能够较好的抑制短沟道效 应。但是,现有技术中,对于短沟道效应的改善,仍无法满足场效应管在集成时的需求。 随着技术不断发展,立体场效应管的体积逐渐缩小,现在已经能够达到10nm以下 的 制程节点,则要求FinFET的栅极线最小可以达到30-80nm以下。但是,目前使用的主流 光刻方式,例如深紫外光刻(Deep Ultraviolet Lithography,DUV)等,均不能对尺寸如此 小的器件进行刻蚀,也不能形成30nm以下的栅极线。 现在已经有例如自对准双重成像技术(Self-aligned Double Patterning,SADP) 等新技术 可以利用作为立体场效应管的加工方式。具体来说,SADP就是在一次光刻完成 后,相继 使用非光刻工艺步骤实现对光刻图形的空间倍频。最后,使用另外一次光刻和刻 蚀把多余 的图形去掉。但是,采用SADP进行立体场效应管加工的过程,流程较为复杂,成品 率底。 另外,现有技术中,场效应管上会形成有两种类型的掩膜:栅掩膜(GM)和阱掩膜 (GT)。栅掩膜用在栅极线的关键尺寸较小的场效应管上;阱掩膜用在栅极线的关键尺寸 较 大的场效应管上。由此,需要分别在不同场合调整工艺步骤,来对关键尺寸不同的场效 应 管进行刻蚀,更进一步导致了加工流程复杂的问题。

技术实现要素:

本发明的目的在于解决现有技术中的FinFET性能不佳的问题。本发明提供了一种 场 效应管的形成方法,操作简单、便捷,并且优品率高。更进一步,能够有效地增大刻蚀源 极与栅极之间的鳍部,以及刻蚀漏极与栅极之间的鳍部后形成的沟槽,因此可以增大设置 该在沟槽内的外延层的体积,从而通过外延层的体积增大,可以减小源极与漏极之间的电 阻,减小短沟道效应,提高FinFET的性能。 为解决上述技术问题,本发明的实施方式公开了一种场效应管的形成方法,包括 提供 半导体衬底,在半导体衬底上形成鳍部、栅极、源极和漏极,并在衬底上形成浅沟槽隔 离 层;在浅沟槽隔离层上沉积厚度均匀的牺牲材料层;刻蚀去除覆盖栅极、源极和漏极顶 部 的牺牲材料层;去除源极、栅极、漏极周侧的牺牲材料层;刻蚀源极与栅极之间的鳍部, 以及刻蚀漏极和栅极之间的鳍部,至鳍部的顶部低于浅沟槽隔离层顶部所在的位置,或鳍 3 CN 111613532 A 说 明 书 2/10 页 部的顶部与浅沟槽隔离层的顶部平齐的位置。 采用上述技术方案,可以使FinFET的制作过程更加简单、便捷,并且优品率高。更 进一步,能够还可以有效地增大刻蚀源极与栅极之间的鳍部,以及刻蚀漏极与栅极之间的 鳍部后形成的沟槽,因此可以增大设置该在沟槽内的外延层的体积,从而通过外延层的体 积增大,可以减小源极与漏极之间的电阻,进而减小短沟道效应,有效地提高了FinFET 的 性能。 根据本发明的另一