技术摘要:

一种方法包括布局标准单元区域,在标准单元区域内具有矩形空间。标准单元区域包括具有面向矩形空间的第一底部边界的第一行标准单元;以及多个标准单元,具有面向矩形空间的侧边界。多个标准单元包括底行的标准单元。在矩形空间中布局存储器阵列,并且底行的第二底部边 全部

背景技术:

通常为存储器阵列形式的存储器单元通常与标准单元形成在同一芯片上。标准单 元可以包括使用存储器单元的逻辑电路的单元。常用的存储器单元是静态随机存取存储器 (SRAM)单元。传统上,由于设计规则和工艺原因,SRAM单元不能直接邻接标准单元,并且需 要在SRAM单元和最近的标准单元之间保留空白空间。空白空间大于多个标准单元的总单元 高度。因此,常规电路在芯片面积使用方面没有成本效益。

技术实现要素:

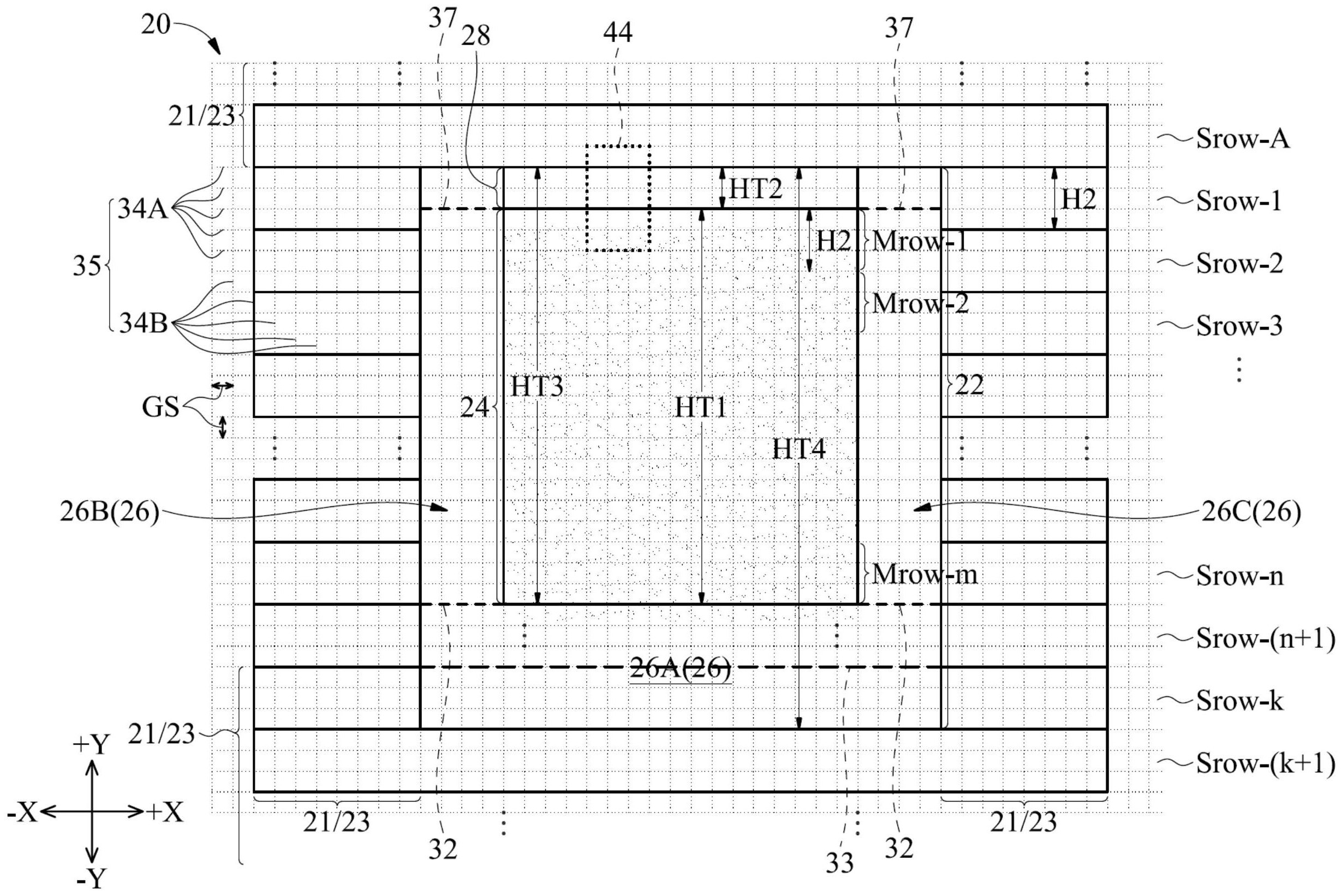

本发明的实施例提供了一种制造集成电路结构的方法,包括:布局标准单元区域, 在所述标准单元区域内具有矩形空间,其中,所述标准单元区域包括:第一行标准单元,具 有面向所述矩形空间的第一底部边界;和多个标准单元,具有面向所述矩形空间的侧边界, 其中,所述多个标准单元包括底行的标准单元;在所述矩形空间中布局存储器阵列,其中, 所述底行的第二底部边界和所述存储器阵列的第三底部边界与同一直线对准;以及在所述 矩形空间中布局填充单元区域,其中,所述填充单元区域包括:第一顶部边界,与所述第一 行标准单元的所述第一底部边界接触;和第四底部边界,与所述存储器阵列的第二顶部边 界接触。 本发明的另一实施例提供了一种集成电路结构,包括:多个标准单元,形成标准单 元行;静态随机存取存储器(SRAM)阵列;以及多个填充单元,在所述标准单元行和所述静态 随机存取存储器阵列之间形成填充单元行,其中,所述多个填充单元的第一高度等于所述 静态随机存取存储器阵列中的静态随机存取存储器单元的第二高度,并且其中,所述多个 填充单元的顶部边界与所述多个标准单元的底部边界接触,并且所述多个填充单元的底部 边界与所述静态随机存取存储器阵列的顶部边界接触。 本发明的又一实施例提供了一种集成电路结构,包括:静态随机存取存储器 (SRAM)单元,具有第一长度和第一高度;第一填充单元,具有等于所述第一长度的第二长度 和等于所述第一高度的第二高度,其中,所述第一填充单元包括多个第一半导体鳍,每个所 述第一半导体鳍从所述第一填充单元的第一边界延伸到第二边界;以及标准单元,其中,所 述第一填充单元位于所述静态随机存取存储器单元和所述标准单元之间。 附图说明 当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该强 调,根据工业中的标准实践,各个部件未按比例绘制并且仅用于说明的目的。实际上,为了 清楚的讨论,各个部件的尺寸可以任意地增大或减小。 图1示出了根据一些实施例的电路中的器件区域的示意图。 4 CN 111599803 A 说 明 书 2/11 页 图2示出了根据一些实施例的与设计网格相应的标准单元的边界。 图3示出了根据一些实施例的与设计网格相应的存储器单元的边界。 图4至图7示出了根据一些实施例的与设计网格相应的填充单元的边界。 图8示出了根据一些实施例的与设计网格相应的标准单元、填充单元set0和存储 器单元的邻接方案。 图9示出了根据一些实施例的与设计网格相应的标准单元、填充单元set3、填充单 元set0和存储器单元的邻接方案。 图10示出了根据一些实施例的与设计网格相应的标准单元、填充单元set6、填充 单元set0和存储器单元的邻接方案。 图11示出了根据一些实施例的与设计网格相应的标准单元、填充单元set3、填充 单元set6、填充单元set0和存储器单元的邻接。 图12至图14示出了根据一些实施例的一些电路的布局中的一些细节。 图15示出了根据一些实施例的包括两个存储器阵列的电路的器件区域。 图16示出了根据一些实施例的用于设计电路的工艺流程。