技术摘要:

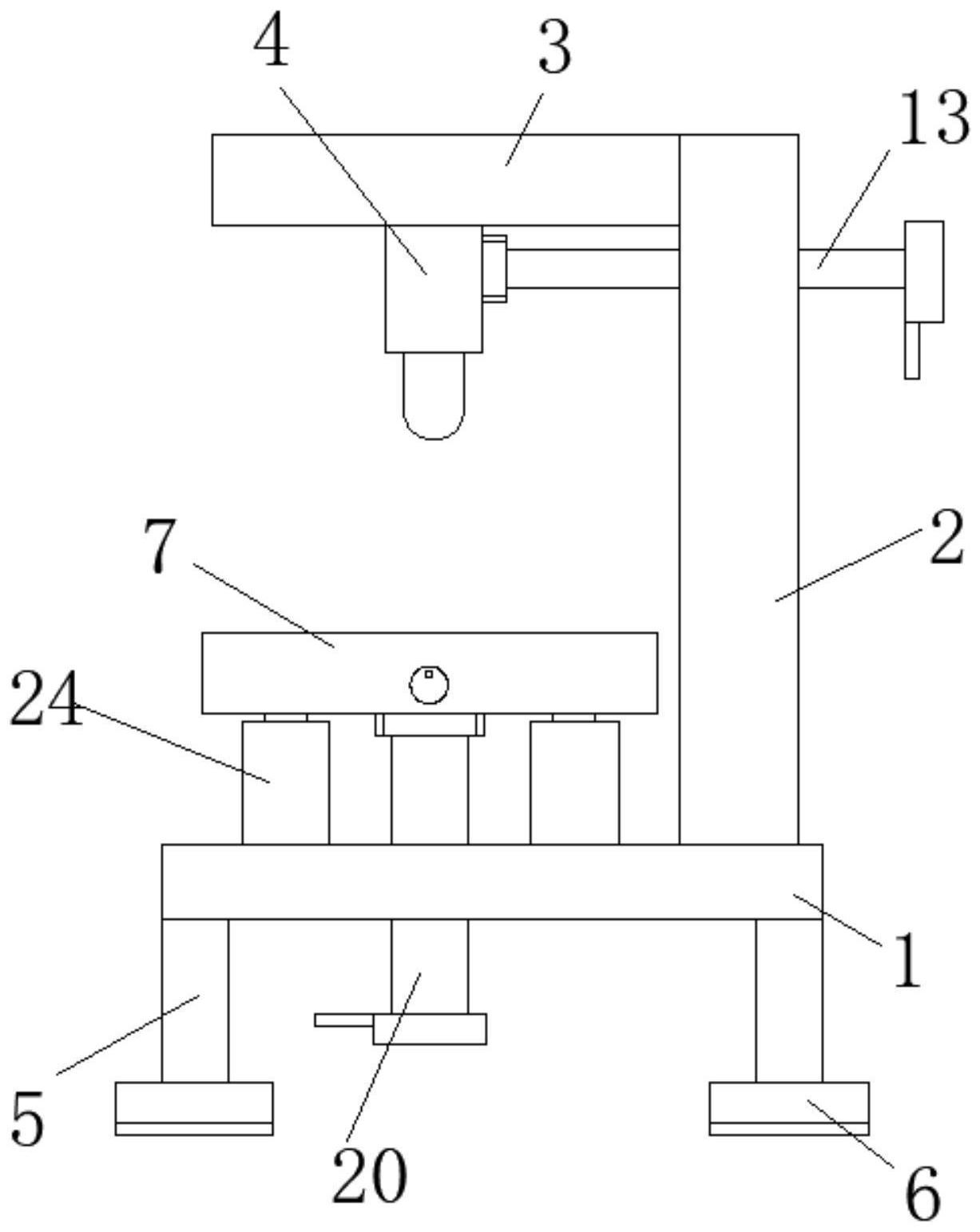

本发明公开的一种带限位结构的芯片测试装置,包括底板,所述底板的顶部设有第一支撑板,所述第一支撑板的底部与底板的顶部固定连接,所述底板的上方设有顶板,所述顶板的一侧与第一支撑板的一侧固定连接,所述顶板的底部设有芯片测试探针,所述芯片测试探针与第一支撑 全部

背景技术:

芯片封装不但为芯片提供隔离周围环境的保护,更进一步为芯片提供一个连接界 面。芯片的封装方式比较常见的有以下三种方式:QFN、BGA和LQFP。封装后的芯片需要用 Handler(处理器)来对芯片进行测试,同种型号的Handler(处理器)可以测试不同封装形式 的芯片。芯片是一种将电路制造在半导体芯片表面上的集成电路,集成电路芯片的测试分 类包括:晶圆测试、芯片测试和封装测试,芯片测试是在晶圆经过切割、减薄工序,成为一片 片独立的片之后的测试,其一般是将芯片放在测试平台上,用探针探到芯片中事先确定的 测试点,探针上可以通过直流电流和交流信号,可以对其进行各种电气参数测试,然而,现 有的芯片测试装置一般不具备限位机构,而部分有限位机构的测试装置,也不便于快速固 定芯片,以及便捷的完成芯片位置的调节,不便于实际操作。

技术实现要素:

本发明的主要目的在于提供一种带限位结构的芯片测试装置,可以有效解决背景 技术中问题。 为实现上述目的,本发明采取的技术方案为: 一种带限位结构的芯片测试装置,包括底板,所述底板的顶部设有第一支撑板,所述第 一支撑板的底部与底板的顶部固定连接,所述底板的上方设有顶板,所述顶板的一侧与第 一支撑板的一侧固定连接,所述顶板的底部设有芯片测试探针,所述芯片测试探针与第一 支撑板之间设有调节组件,所述底板的底部固定连接有若干支撑腿,所述支撑腿的底部固 定连接有固定板,所述底板和芯片测试探针之间设有测试板,所述测试板与底板之间设有 升降组件,所述测试板上设有限位机构,所述限位机构包括开设于测试板顶部的凹槽,所述 凹槽内设有滑板,所述凹槽内设有与滑板相配合的驱动组件,所述滑板的顶部固定连接有 两个第二支撑板,两个所述第二支撑板相靠近的一侧均设有夹板,所述夹板与第二支撑板 通过若干弹簧连接。 优选的,所述调节组件包括开设于第一支撑板一侧的第一螺纹孔,所述第一螺纹 孔内设有第一丝杆,所述第一支撑板远离芯片测试探针的一侧设有旋转块,所述第一丝杆 的一端与旋转块固定连接,所述第一丝杆的另一端与芯片测试探针通过第一轴承连接,所 述顶板的底部开设有第一滑槽,所述第一滑槽内设有第一滑块,所述第一滑块的底部与芯 片测试探针的顶部固定连接。 优选的,所述第一滑槽和第一滑块的横截面均为T形结构,所述旋转块的底部固定 连接有第一握把。 优选的,所述升降组件包括开设于底板顶部的第二螺纹孔,所述第二螺纹孔内设 有第二丝杆,所述第二丝杆的顶部与测试板的底部通过第二轴承连接,所述第二丝杆的底 4 CN 111579964 A 说 明 书 2/5 页 部与位于底板下方的第一转盘固定连接,所述底板的顶部固定连接有两个套管,所述套管 内设有限位杆,所述限位杆的顶端延伸至套管的外部,且所述限位杆的顶部与测试板的底 部固定连接。 优选的,所述第一转盘的一侧固定连接有第二握把。 优选的,所述驱动组件包括开设于滑板一侧的第三螺纹孔,所述第三螺纹孔内设 有第三丝杆,所述第三丝杆的一端与凹槽的一侧内壁通过第三轴承连接,所述第三丝杆的 另一端与位于测试板一侧的第二转盘固定连接。 优选的,所述凹槽的底部内壁开设有第二滑槽,所述第二滑槽内设有第二滑块,所 述第二滑块的顶部与滑板的底部固定连接,所述第二转盘远离测试板的一侧固定连接有手 柄。 优选的,所述滑板的顶部开设有第三滑槽,所述第三滑槽内设有第三滑块,所述第 三滑块的顶部与夹板的底部固定连接,所述第三滑槽和第三滑块的横截面均为T形结构。 优选的,两个所述夹板相靠近的一侧均固定连接有防滑垫。 与现有技术相比,本发明具有如下有益效果: 针对现有存在的弊端,通过设置底板、第一支撑板和升降组件的配合作用,可以自由调 节测试板的高度,进而便于调节位于两个夹板之间芯片的高度,便于对芯片进行测试,通过 设置第一支撑板、顶板、芯片测试探针和调节组件的配合作用,可以左右调节芯片测试探针 的位置,通过设置测试板、凹槽、滑板、第二支撑板、夹板、弹簧和驱动组件的配合作用,可以 前后调节滑板的位置,当两个夹板之间固定芯片时,芯片可以前后位置调节,进而芯片测试 探针可以探到芯片上不同位置的测试点,提高了测试范围,操作简单,便于实际使用,通过 设置第三滑槽和第三滑块的配合作用,使得夹板平稳的移动,避免夹板倾斜晃动,便于对芯 片的夹持固定,通过设置的防滑垫,减少芯片相对夹板滑动的可能,进一步的使得芯片较为 稳定的固定在两个夹板之间。 附图说明 图1为本发明一种带限位结构的芯片测试装置的整体结构示意图; 图2为本发明一种带限位结构的芯片测试装置调节组件的结构示意图; 图3为本发明一种带限位结构的芯片测试装置升降组件的结构示意图; 图4为本发明一种带限位结构的芯片测试装置限位机构的结构示意图; 图5为图4中A处的局部放大示意图。 图中:1、底板;2、第一支撑板;3、顶板;4、芯片测试探针;5、支撑腿;6、固定板;7、测 试板;8、凹槽;9、滑板;10、第二支撑板;11、夹板;12、第一螺纹孔;13、第一丝杆;14、第一滑 槽;15、第一滑块;16、第一轴承;17、旋转块;18、第一握把;19、第二螺纹孔;20、第二丝杆; 21、第二轴承;22、第一转盘;23、第二握把;24、套管;25、限位杆;26、第三螺纹孔;27、第三丝 杆;28、第三轴承;29、第二转盘;30、手柄;31、第二滑槽;32、第二滑块;33、弹簧;34、第三滑 槽;35、第三滑块;36、防滑垫。