技术摘要:

本发明提供了一种GaN器件及制备方法,制备方法包括如下步骤:提供GaN器件外延片,所述GaN器件外延片至少包括外延衬底和在所述外延衬底上外延生长的GaN沟道层,在所述GaN器件外延片上定义源区和漏区;在所述源区和所述漏区之间通过刻蚀所述GaN沟道层形成多个在垂直于所 全部

背景技术:

晶体管的跨导随栅极电压的变化呈钟形曲线,这主要由以下几个物理原因造成, 包括:(i)自热效应;(ii)动态源极接入电阻的增加;(iii)光学声子发射;以及(iv)接触势 垒。为了改善器件线性度,从设计上来讲,具有垂直堆叠多量子阱沟道器件的gm线性度较 好,但在实际应用中并不常用。而采用新材料的解决方案,包括氮(N)-极化表面的氮化镓 (GaN)和源极二次外延生长可以改善器件的线性品质因数,即输出三阶互调截点(OIP3)与 直流电源(PDC)的比率OIP3/PDC,但其对于线性度的改善仍有进一步提升的空间。 目前,对于晶体管的线性度问题及瓶颈,通常采用电路线性化技术来解决。例如, 采用微分叠加(DS)和抵消在低频条件下可以扩展晶体管的线性度。然而,上述解决方案在 高频条件下难以实施,且无法处理大功率信号。 因此,有必要提出一种新的GaN器件及制备方法,解决上述问题。

技术实现要素:

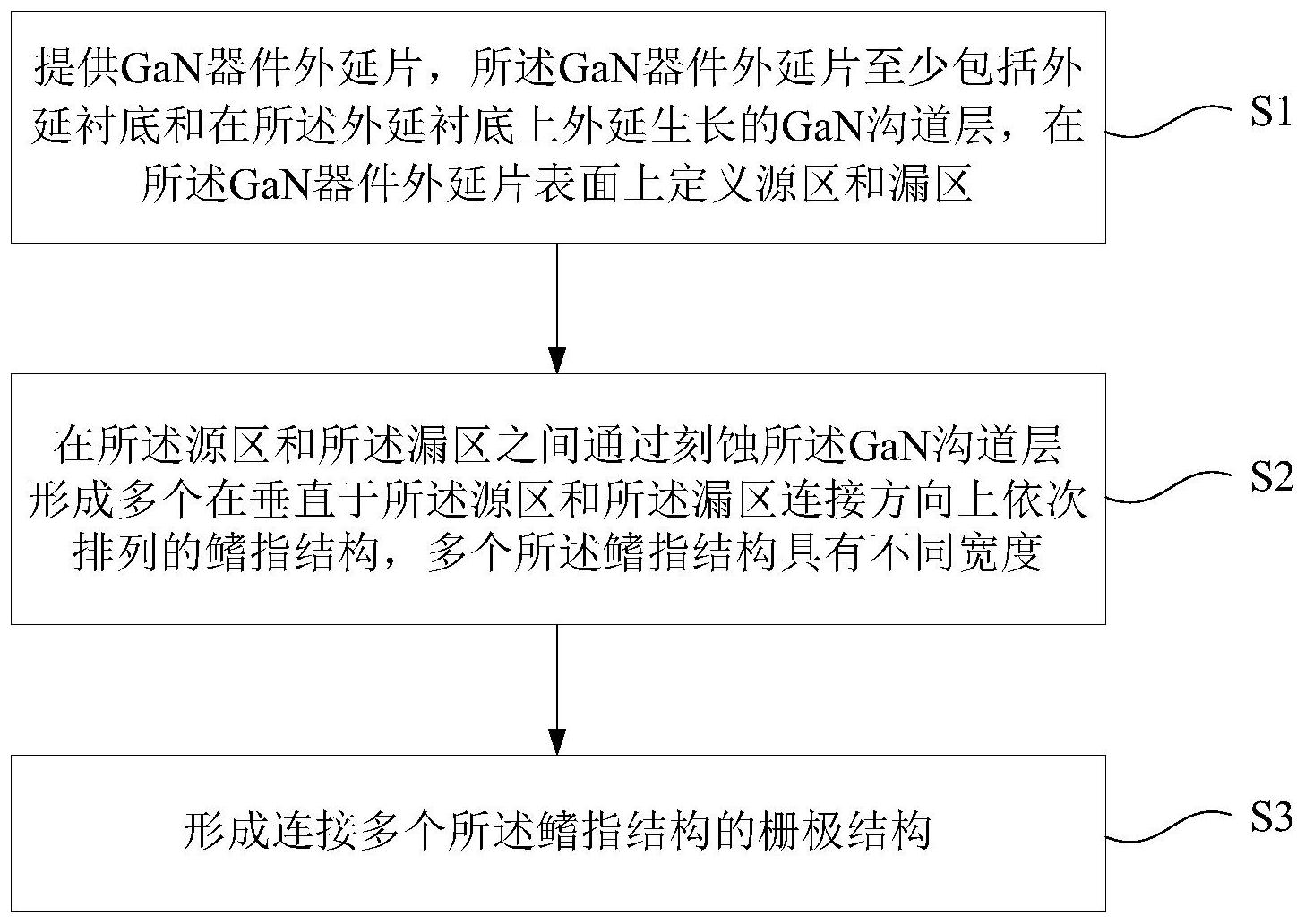

鉴于以上所述现有技术的缺点,本发明的目的在于提供一种GaN器件及制备方法, 用于解决现有技术中GaN器件非线性的问题。 为实现上述目的及其它相关目的,本发明提供了一种GaN器件的制备方法,其特征 在于,包括如下步骤: 提供GaN器件外延片,所述GaN器件外延片至少包括外延衬底和在所述外延衬底上 外延生长的GaN沟道层,在所述GaN器件外延片表面上定义源区和漏区; 在所述源区和所述漏区之间通过刻蚀所述GaN沟道层形成多个在垂直于所述源区 和所述漏区连接方向上依次排列的鳍指结构,多个所述鳍指结构具有不同宽度; 形成连接多个所述鳍指结构的栅极结构。 作为本发明的一种可选方案,多个所述鳍指结构的宽度沿排列方向依次增加。 作为本发明的一种可选方案,多个所述鳍指结构的宽度包括宽度依次增加的第一 宽度至第N宽度,N为大于1的正整数;具有第n宽度的所述鳍指结构的数量为N-(n-1)个,n为 1至N的正整数;N·(N 1)/2个所述鳍指结构按照第n宽度中n的大小依次排列。 作为本发明的一种可选方案,所述鳍指结构的两端分别直接连接所述源区和所述 漏区,或者所述鳍指结构的两端通过所述GaN沟道层连接所述源区和所述漏区。 作为本发明的一种可选方案,所述外延衬底和所述GaN沟道层之间还形成有成核 层和缓冲层,所述GaN沟道层上方还形成有势垒层。 作为本发明的一种可选方案,在所述GaN器件外延片表面上定义所述源区和所述 漏区后,还包括在所述源区上形成源极结构以及在所述漏区上形成漏极结构的步骤。 作为本发明的一种可选方案,所述源极结构和所述漏极结构包括与所述源区或所 4 CN 111584619 A 说 明 书 2/8 页 述漏区形成欧姆接触的金属叠层结构。 作为本发明的一种可选方案,形成所述鳍指结构的方法包括如下步骤: 在所述GaN器件外延片表面涂布负性光刻材料; 通过电子束光刻形成图形化的硬掩模; 以所述硬掩模作为刻蚀掩膜,通过干法刻蚀形成所述鳍指结构。 作为本发明的一种可选方案,所述负性光刻材料包括氢倍半硅氧烷。 作为本发明的一种可选方案,所述栅极结构包括栅极介质层和栅极金属电极。 作为本发明的一种可选方案,在形成所述栅极结构后,还包括在所述GaN器件上方 沉积钝化层的步骤。 本发明还提供了一种GaN器件,其特征在于,包括: 在外延衬底上外延生长的GaN沟道层,所述GaN沟道层上定义有源区和漏区; 形成于所述GaN沟道层中的多个依次排列的鳍指结构,多个所述鳍指结构具有不 同宽度; 连接多个所述鳍指结构的栅极结构。 作为本发明的一种可选方案,多个所述鳍指结构的宽度沿排列方向依次增加。 作为本发明的一种可选方案,多个所述鳍指结构的宽度包括宽度依次增加的第一 宽度至第N宽度,N为大于1的正整数;具有第n宽度的所述鳍指结构的数量为N-(n-1)个,n为 1至N的正整数;N·(N 1)/2个所述鳍指结构按照第n宽度中n的大小依次排列。 作为本发明的一种可选方案,所述鳍指结构的两端分别直接连接所述源区和所述 漏区,或者所述鳍指结构的两端通过所述GaN沟道层连接所述源区和所述漏区。 如上所述,本发明提供一种GaN器件及制备方法,具有以下有益效果: 本发明通过引入具有不同宽度的鳍指结构,实现跨导补偿作用,在栅压VGS的一定 变化范围内使跨导gm尽可能保持线性变化,从而得到高线性度的GaN器件,其无需通过额外 电路补偿设计进行线性优化,节省了成本,且制备工艺简单、可操作性强、重复性好、可靠性 高。 附图说明 图1显示为本发明实施例一中GaN器件的制备方法的流程图。 图2显示为本发明实施例一中提供的GaN器件外延片的截面示意图。 图3显示为本发明实施例一中提供的GaN器件外延片的俯视示意图。 图4显示为本发明实施例一中形成源极结构和漏极结构后的截面示意图。 图5显示为本发明实施例一中形成源极结构和漏极结构后的俯视示意图。 图6显示为本发明实施例一中通过电子束光刻形成硬掩模后的俯视示意图。 图7显示为本发明实施例一中刻蚀形成鳍指结构后的俯视示意图。 图8显示为本发明实施例一中图7中AA’方向的截面示意图。 图9显示为本发明实施例一中形成栅极结构后的俯视示意图。 图10显示为本发明实施例一中图9中AA’方向的截面示意图。 图11显示为本发明实施例一中不同鳍指宽度的器件跨导随栅压的变化关系图。 图12显示为本发明实施例二中增加刻蚀掩膜后的俯视示意图。 5 CN 111584619 A 说 明 书 3/8 页 图13显示为本发明实施例二中刻蚀形成鳍指结构后的俯视示意图。 图14显示为本发明实施例二中形成栅极结构后的俯视示意图。 元件标号说明 100 外延衬底 101 GaN沟道层 102 源区 102a 源极结构 103 漏区 103a 漏极结构 104 成核层 105 缓冲层 106 势垒层 107 硬掩模 108 鳍指结构 109 栅极介质层 110 栅极金属电极 201 GaN沟道层 202 源区 202a 源极结构 203 漏区 203a 漏极结构 206 势垒层 207 硬掩模 208 鳍指结构 209 栅极介质层 210 栅极金属电极 211 刻蚀掩膜 S1~S3 步骤1)~3)