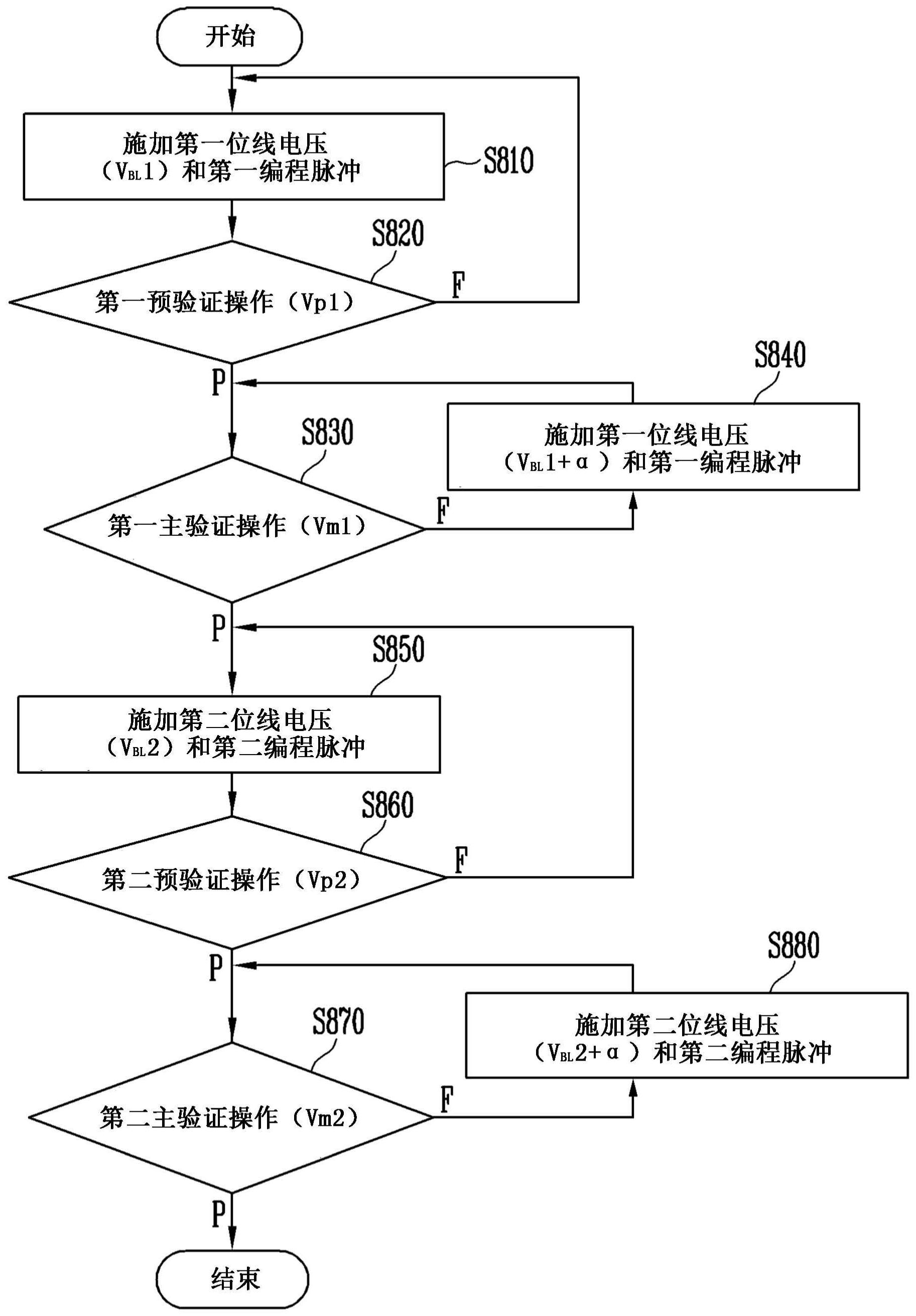

技术摘要:

本文可以提供半导体装置及操作半导体装置的方法。该方法可以包括:使用第一编程脉冲、第一位线电压、第一预验证电压和第一主验证电压对被选存储器单元执行第一编程操作,并且在第一预验证电压和第一主验证电压之间具有第一电平差;以及使用第二编程脉冲、第二位线电压 全部

背景技术:

半导体存储器装置是包括诸如硅(Si)、锗(Ge)、砷化镓(GaAs)、磷化铟(InP)等的 半导体的存储器装置。半导体存储器装置分为易失性存储器装置和非易失性存储器装置。 易失性存储器装置是当断电时其内存储的数据丢失的存储器装置。易失性存储器 装置的代表性示例包括静态RAM(SRAM)、动态RAM(DRAM)和同步DRAM(SDRAM)。非易失性存储 器装置是即使断电也保持其内所存储的数据的存储器装置。非易失性存储器装置的代表性 示例包括只读存储器(ROM)、可编程ROM(PROM)、电可编程ROM(EPROM)、电可擦除可编程ROM (EEPROM)、闪存、相变随机存取存储器(PRAM)、磁RAM(MRAM)、电阻RAM(RRAM)和铁电RAM (FRAM)。闪存分为NOR型和NAND型。由于消费者对更小、更强大的电子装置的需求不断增长, 因此非常期望显现出改进的特性的半导体存储器装置。

技术实现要素:

本发明公开的各个实施方式涉及具有改进的操作特性的半导体装置,以及操作该 半导体装置的方法。更具体地,本发明涉及一种改进了分布效率并减少了编程时间的半导 体装置的操作的改进的编程和验证方法。本发明具体适合于诸如例如NAND闪存之类的非易 失性存储器。 根据本发明的实施方式,提供了一种操作半导体装置的改进方法,该方法包括:使 用第一编程脉冲、第一位线电压、第一预验证电压和第一主验证电压对被选存储器单元执 行第一编程操作,并且在第一预验证电压和第一主验证电压之间具有第一电平差;以及使 用第二编程脉冲、第二位线电压、第二预验证电压和第二主验证电压对被选存储器单元执 行第二编程操作,并且在第二预验证电压与第二主验证电压之间具有第二电平差,其中,第 二电平差可以小于第一电平差,并且第二位线电压的电平可以高于第一位线电压的电平。 根据本发明的另一实施方式,一种操作半导体装置的方法可以包括:执行第一编 程操作,该第一编程操作使用第一编程脉冲执行编程操作并使用其间具有第一电平差的第 一预验证电压和第一主验证电压执行验证操作,并在被选存储器单元具有在第一预验证电 压和第一主验证电压之间的阈值电压时将第一位线电压施加到被选位线并将增加后的第 一编程脉冲施加到被选字线;以及执行第二编程操作,该第二编程操作使用第二编程脉冲 执行编程操作,并使用其间具有第二电平差的第二预验证电压和第二主验证电压执行验证 操作,并在被选存储器单元具有在第二预验证电压和第二主验证电压之间的阈值电压时将 第二位线电压施加到被选位线并将增加后的第二编程脉冲施加到被选字线,其中,当第二 电平差小于第一电平差时,第二位线电压的电平可以高于第一位线电压的电平。 根据本发明的又一实施方式,一种操作半导体装置的方法,半导体装置可以包括 6 CN 111554338 A 说 明 书 2/11 页 存储器串,该存储器串包括多个存储器单元并且联接在源极线和位线之间,该方法包括:将 第一位线电压施加到联接到被选存储器串的被选位线;将第一编程脉冲施加到联接到被选 存储器单元的被选字线;将第一预验证电压施加到被选字线;当使用第一预验证电压的第 一预验证操作通过时,将第一主验证电压施加到被选字线;当使用第一主验证电压的第一 主验证操作失败时,将增加后的第一位线电压施加到被选位线;以及当将增加后的第一位 线电压施加到被选位线时,将增加后的第一编程脉冲施加到被选字线,其中,随着第一预验 证电压与第一主验证电压之间的第一电平差越小,第一位线电压的增量可以越大。 本发明还涉及一种半导体装置,该半导体装置包括:存储器串,该存储器串联接于 源极线与位线之间,且包括多个存储器单元;外围电路,该外围电路被配置为使用第一编程 脉冲、第一位线电压、第一预验证电压和第一主验证电压对多个存储器单元执行第一编程 操作,其中第一预验证电压和第一主验证电压之间具有第一电平差,然后使用第二编程脉 冲、第二位线电压、第二预验证电压和第二主验证电压对多个存储器单元执行第二编程操 作,其中,在第二预验证电压和第二主验证电压之间具有第二电平差,以及控制逻辑,该控 制逻辑被配置为控制外围电路,使得第二电平差小于第一电平差,并且第二位线电压的电 平高于第一位线电压的电平。 通过以下结合附图的详细描述,本发明的这些和其他特征和优点对于本发明的领 域的技术人员将变得显而易见。 附图说明 图1是例示根据本发明公开的实施方式的半导体装置的配置的框图。 图2至图4是例示根据本发明公开的实施方式的半导体装置的单元阵列结构的电 路图。 图5A至图5C是用于描述根据本发明公开的实施方式的操作半导体装置的方法的 图。 图6是用于描述根据本发明公开的实施方式的操作半导体装置的方法的图。 图7A至图7B是用于描述根据本发明公开的实施方式的操作半导体装置的方法的 图。 图8是根据本发明公开的实施方式的操作半导体装置的方法的流程图。 图9是例示根据本发明公开的实施方式的存储器系统的配置的框图。 图10是例示根据本发明公开的实施方式的存储器系统的配置的框图。 图11是例示根据本发明公开的实施方式的计算系统的配置的框图。