技术摘要:

一种移位暂存器及其方法。本发明涉及一种电路,一电路包含:一输入电路级,用以在一第一相中接收一输入脉冲信号;一输出电路级,耦接至该输入电路级,用以根据一第一时脉信号在该第一相后的在一第二相中产生一输出脉冲信号;以及一辅助电路级,耦接至该输入电路级及该 全部

背景技术:

一移位暂存器可用以执行诸如资料暂存、用以输入二元资料之依序与平行输出的 延迟或转换等作业。举例来说,当用于OLED驱动器电路中,移位暂存器可用以根据一时脉信 号依序提供脉冲信号至复数个资料输出端,而使得能够一行接一行地输出资料驱动信号或 闸驱动信号以驱动相应的像素。

技术实现要素:

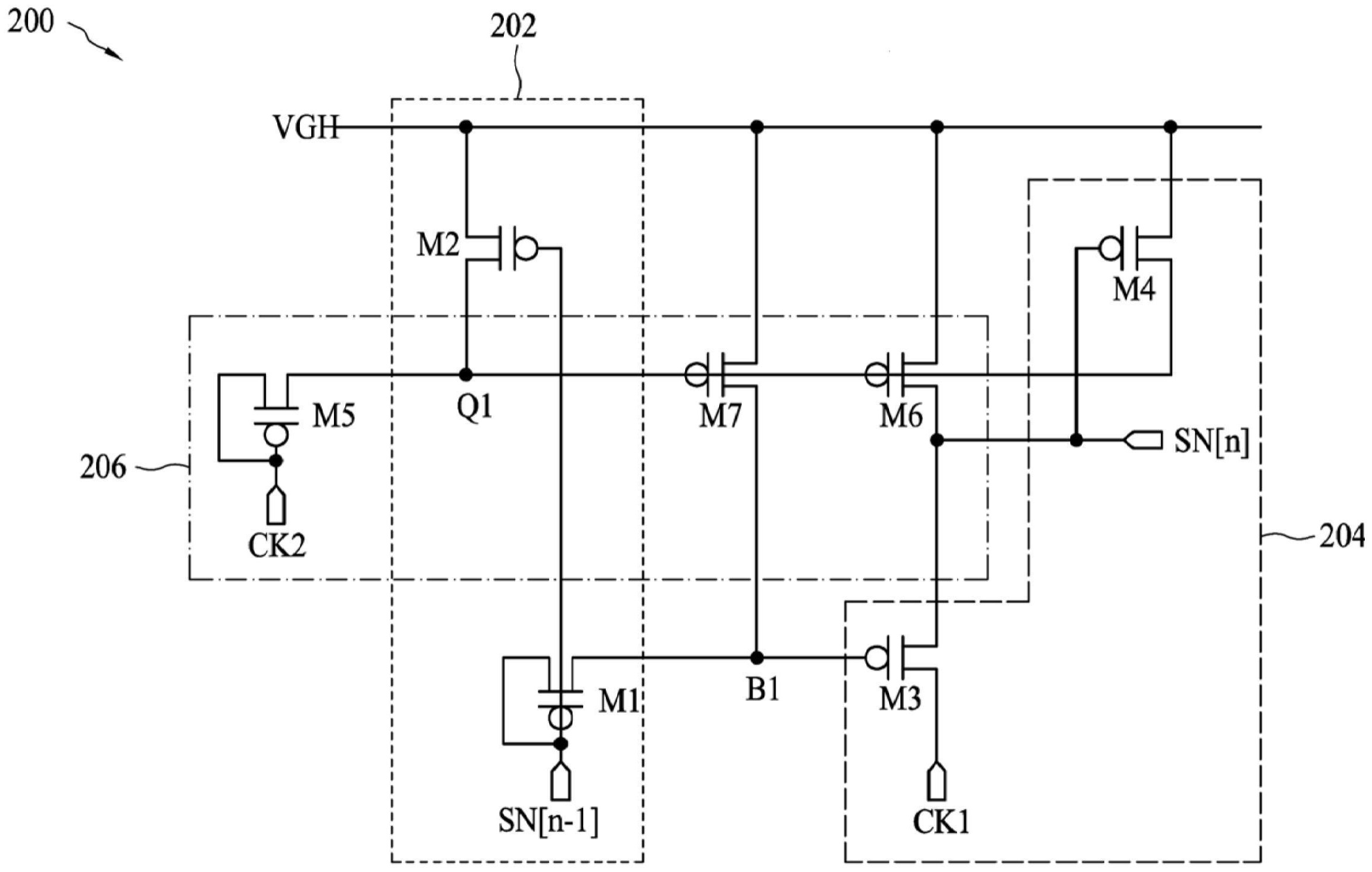

针对现有技术中存在的技术问题,本发明的实施方式提出一种电路,其包括一输 入电路级、一输出电路级以及一辅助电路级。输入电路级用以在一第一相中接收一输入脉 冲信号。输出电路级耦接至该输入电路级,用以根据一第一时脉信号在该第一相后的在一 第二相中产生一输出脉冲信号。辅助电路级耦接至该输入电路级及该输出电路级,用以根 据与该第一时脉信号不同的一第二时脉信号在该第二相后的一第三相中保持该输出脉冲 信号为一预定电压值。 在一实施例中,该输入脉冲信号装置该第一相中有一第一脉冲,其具有一第一脉 冲宽度;该第一时脉信号于该第二相中有一第二脉冲,其具有一第二脉冲宽度,且该第二脉 冲宽度等于该第一脉冲宽度。 在一实施例中,该第一时脉信号在该第二相中有一第一脉冲,其具有一第一脉冲 宽度;该输出脉冲信号在该第二相中有一第二脉冲,其具有一第二脉冲宽度,且该第二脉冲 宽度等于该第一脉冲宽度。 在一实施例中,该第一时脉信号在该第二相中有一第一脉冲,其具有一第一脉冲 宽度;该第二时脉信号在该第三相中有一第二脉冲,其具有一第二脉冲宽度,且该第二脉冲 宽度等于该第一脉冲宽度。 在一实施例中,该电路还包括一电容装置,耦接于该输出电路级及该输入电路级 间。 在一实施例中,该电路还包括一电容装置,耦接于该辅助电路级及一参考电压间。 在一实施例中,该输入电路级包括一第一晶体管,有一控制端用以接收该输入脉 冲信号、一第一连接端耦接至该控制端以及一第二连接端耦接至该输出级;以及一第二晶 体管,有一控制端用以接收该输入脉冲信号、一第一连接端耦接至一参考电压以及第二连 接端耦接至该辅助电路级。 在一实施例中,该输入电路级包括一第三晶体管,有一控制端耦接至该第一晶体 管的该第二连接端、一第一连接端用以接收该第一时脉信号、以及一第二连接端用以输出 该输出脉冲信号;以及一第四晶体管,有一控制端耦接至该第三晶体管的该第二连接端、一 第一连接端耦接至该参考电压以及一第二连接端耦接至该辅助电路级。 5 CN 111583986 A 说 明 书 2/11 页 在一实施例中,该输出电路级还包括一电容装置,有一第一端耦接至该第三晶体 管的该控制端以及一第二端耦接至该第三晶体管的该第二连接端。 在一实施例中,该辅助电路级包括一第五晶体管,有一控制端用以接收该第二时 脉信号、一第一连接端耦接至该控制端以及一第二连接端耦接至该第四晶体管的该第二连 接端;一第六晶体管,有一控制端耦接至该第五晶体管的该第二连接端、一第一连接端耦接 至该参考电压以及一第二连接端耦接至该第三晶体管的该控制端;以及一第七晶体管,有 一控制端耦接至该第五晶体管的该第二连接端、一第一连接端耦接至该参考电压以及一第 二连接端耦接至该第三晶体管的该第二连接端。 在一实施例中,该辅助电路级还包括一电容装置,有一第一端耦接至该第六晶体 管的该控制端以及一第二端耦接至该参考电压。 本发明的实施方式提供一种移位暂存器,其包括一第一电路及一第二电路。第一 电路用以根据一输入脉冲信号、一第一时脉信号及一第二时脉信号而产生一第一输出脉冲 信号。第一电路包括:一第一输入电路级,用以在一第一相中接收输入脉冲信号;一第一输 出电路级,耦接至第一输入电路级,用以根据第一时脉信号在第一相后的一第二相中产生 第一输出脉冲信号;以及一第一辅助电路级,耦接至第一输入电路级及第一输出电路级,用 以根据与第一时脉信号不同的第二时脉信号在第二相后的一第三相中保持第一输出脉冲 信号为一预定电压值。第二电路用以根据第一输出脉冲信号、第一时脉信号及第二时脉信 号而产生一第二输出脉冲信号。 在一实施例中,该第二电路包括一第二输入电路级,用以在该第二相中接收该第 一输出脉冲信号;一第二输出电路级,耦接至该第二输入电路级,用以在该第二相后的该第 三相中根据该第一时脉信号产生该第二输出脉冲信号;以及一第二辅助电路级,耦接至该 第二输入电路级及该第二输出电路级,用以在该第三相后的一第四相中根据不同的该第二 时脉信号保持该第二输出脉冲信号为该预定电压值。 在一实施例中,该第一输入电路级包括:一第一晶体管,有一控制端接收该输入脉 冲信号、一第一连接端耦接至该控制端以及一第二连接端耦接至该第一输出级;以及一第 二晶体管,有一控制端接收该输入脉冲信号、一第一连接端耦接至一参考电压以及一第二 连接端耦接至该第一辅助电路级。 在一实施例中,该第一输出电路级包括一第三晶体管,有一控制端耦接至该第一 晶体管的该第二连接端、一第一连接端用以接收该第一时脉信号,以及一第二连接端用以 输出该第一输出脉冲信号;以及一第四晶体管,有一控制端耦接至该第三晶体管的该第二 连接端、一第一连接端耦接至该参考电压以及一第二连接端耦接至该第一辅助电路级。 在一实施例中,该第一辅助电路级包括一第五晶体管,有一控制端接收该第二时 脉信号、一第一连接端耦接至该控制端以及一第二连接端耦接至该第四晶体管的该第二连 接端;一第六晶体管,有一控制端耦接至该第五晶体管的该第二连接端、一第一连接端耦接 至该参考电压以及一第二连接端耦接至该第三晶体管的该控制端;以及一第七晶体管,有 一控制端耦接至该第五晶体管的该第二连接端、一第一连接端耦接至该参考电压以及一第 二连接端耦接至该第三晶体管的该第二连接端。 本发明的实施方式提出一种方法,其包括:排置一输入电路级,以在一第一相中接 收一输入脉冲信号;排置一输出电路级,以根据一第一时脉信号在第一相后的一第二相中 6 CN 111583986 A 说 明 书 3/11 页 产生一输出脉冲信号;以及排置一辅助电路级,以根据与第一时脉信号不同的第二时脉信 号在第二相后的一第三相中保持输出脉冲信号为一预定电压值。 在一实施例中,该方法还包括排置一电容装置以耦接于该输出电路级及该输入电 路级间。 在一实施例中,该方法还包括排置一电容装置以耦接于该辅助电路级及一参考电 压间。 在一实施例中,该输入脉冲信号于该第一相中有一第一脉冲其具有一第一脉冲宽 度、该第一时脉信号于该第二相中有一第二脉冲其具有一第二脉冲宽度,且该第二脉冲宽 度等于该第一脉冲宽度。 附图说明 下面,将结合附图对本发明的优选实施方式进行进一步详细的说明,其中: 图1为根据本发明某些实施方式的移位暂存器的示意图。 图2为根据本发明某些实施方式的暂存电路的示意图。 图3的时序图绘示了根据某些实施方式的暂存电路的信号波形。 图4A为根据某些实施方式,在第一相中的暂存电路。 图4B的时序图绘示了根据某些实施方式,在第一相中的暂存电路的信号波形。 图5A为根据某些实施方式,在第二相中的暂存电路。 图5B的时序图绘示了根据某些实施方式,在第二相中的暂存电路的信号波形。 图6A为根据某些实施方式,在第三相中的暂存电路。 图6B的时序图绘示了根据某些实施方式,在第三相中的暂存电路的信号波形。 图7绘示根据某些实施方式的晶体管的漏电流。 图8为根据本发明某些实施方式的暂存电路的示意图。 图9A为根据某些实施方式,在第二相中的暂存电路。 图9B的时序图绘示了根据某些实施方式,在第二相中的暂存电路的信号波形。 图10A为根据某些实施方式,在第三相中的暂存电路。 图10B的时序图绘示了根据某些实施方式,在第三相中的暂存电路的信号波形。 图11的流程图绘示了根据某些实施方式,用以产生一输出脉冲信号的方法。 100 移位暂存器 102_1-102_n、200、800 暂存电路 202、802 输入电路级 204、804 输出电路级 206、806 辅助电路级 300 信号波形 402、404、502、504、602、604、902、904、1002、1004 脉冲 702、704 曲线 1100 方法 B1、Q1 端 C1、C2 电容装置 7 CN 111583986 A 说 明 书 4/11 页 CK1、CK2、CK3 时脉信号 M1-M7、M1’-M7’ 晶体管 P1、P2、P3 相 SN[START] 初始输入信号 SN[1]-SN[n] 输出脉冲信号 t1-t6、t1’-t6’ 时间点 |Vds| 晶体管的漏极与源极间之电压 差 VGH 参考电压 VGL 接地电压 |Vgs| 晶体管的栅极与源极间之电压 差 Vth 阈值电压 W1、W2、W3 脉冲宽度