技术摘要:

本发明公开了一种基于动态可重配技术的块状存储单元,涉及可编程逻辑器件领域,该块状存储单元通过特殊的物理布局和设计,其工作模式可以基于动态可重配技术在高速和普通两者之间动态切换,当需要使用高速处理单元时可以工作在高速工作模式下,两个块状SRAM并行工作, 全部

背景技术:

可编程逻辑器件具有开发周期短、成本低、风险小、集成度高、灵活性大、便于电子 系统维护和升级等优点,因此受到了广大终端产品用户的青睐,成为了集成电路芯片的主 流,且被广泛应用在各种领域如通信、控制、视频、信息处理、电子、互联网、汽车以及航空航 天等。 可编程逻辑器件主要包含控制系统、可编程逻辑单元、数字信号处理DSP、存储单 元块状SRAM以及一些高速接口、时钟模块和IP核等。FPGA是一种灵活通用性的可编程逻辑 器件,随着FPGA的发展,CPU、AI等单元也集成入FPGA,CPU需要大量存储高速cache,cache的 速率是影响CPU性能的一个关键。如果仅处于性能考虑而单独给CPU、AI配置大量专用高速 SRAM,会使得FPGA被高速SRAM消耗大量面积,这种方法复用率低、低功耗成效差的特点与可 编程逻辑器件的灵活性相悖,由此可见,如何兼顾性能和面积对于可编程逻辑器件来说是 一个巨大的挑战。

技术实现要素:

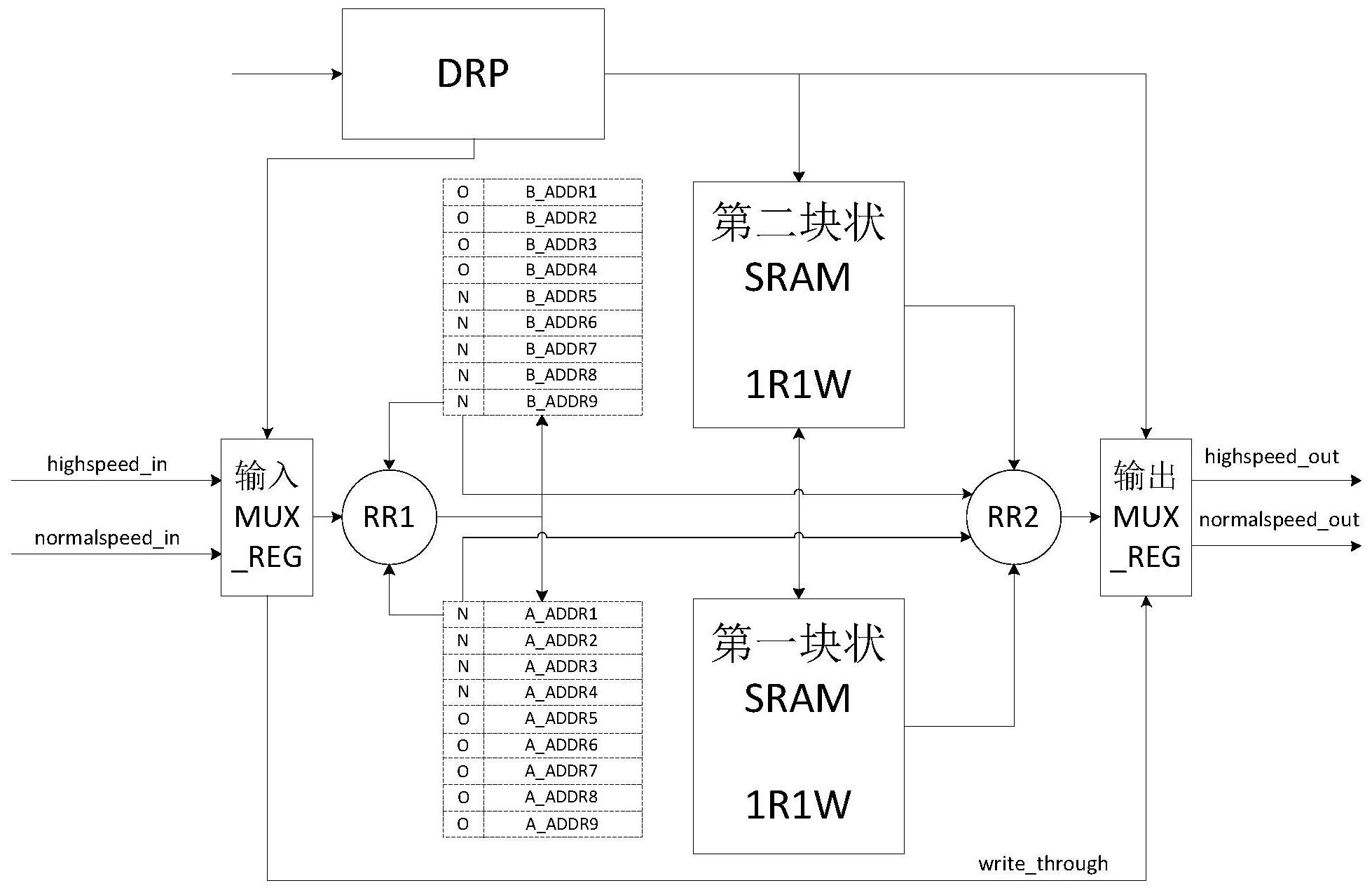

本发明人针对上述问题及技术需求,提出了一种基于动态可重配技术的块状存储 单元,块状存储单元包括动态重配置接口、第一块状SRAM、第二块状SRAM以及读写控制模 块,两块SRAM完全相同,读写控制模块提供高速接口总线和普通接口总线;动态重配置接口 的输入端获取配置参数、输出端连接读写控制模块、第一块状SRAM和第二块状SRAM,动态重 配置接口根据获取到的配置参数配置读写控制模块、第一块状SRAM和第二块状SRAM的配置 位,使得块状存储单元在高速工作模式和普通工作模式之间动态切换; 当块状存储单元处于高速工作模式时,第一块状SRAM和第二块状SRAM在内部的地 址控制模块的控制下并行工作,第一块状SRAM和第二块状SRAM占用相同的地址,块状存储 单元的有效地址宽度为第一块状SRAM的有效地址宽度;第一块状SRAM和第二块状SRAM的读 写端口通过读写控制模块选择控制,读写控制模块通过高速接口总线获取写数据并选择控 制写入其中一个块状SRAM中,和/或,读写控制模块选择控制从其中一个块状SRAM中获取读 数据并输出至高速接口总线;读写控制模块按内部的寄存器的性能进行读写数据; 当块状存储单元处于普通工作模式时,第一块状SRAM和第二块状SRAM在内部的地 址控制模块的控制下串行工作,第一块状SRAM占用低位地址,第二块状SRAM占用高位地址, 块状存储单元的有效地址宽度为第一块状SRAM的有效地址宽度与第二块状SRAM的有效地 址宽度之和;读写控制模块处于旁路状态,普通接口总线中的写数据写入块状存储单元中, 和/或,块状存储单元的读数据输出至普通接口总线。 其进一步的技术方案为,两个块状SRAM内部的地址控制模块包括地址指示标志电 4 CN 111599390 A 说 明 书 2/5 页 路; 当块状存储单元处于高速工作模式时,地址指示标志电路指示各个地址的指示标 志位的状态为新状态或旧状态,且两个块状SRAM中对于同一个地址的指示标志位的状态始 终相反;读写控制模块写入写数据后,地址指示标志电路更新两个块状SRAM中的指示标志 位的状态;读写控制模块根据两个块状SRAM中的指示标志位的状态获取读数据; 当块状存储单元处于普通工作模式时,两个块状SRAM内部的地址指示标志电路均 处于旁路状态。 其进一步的技术方案为,读写控制模块包括读控制模块和写控制模块,写控制模 块包括输入MUX_REG和输入选择调度器,输入MUX_REG内部包括写寄存器,输入MUX_REG根据 输入选择调度器选择控制写入获取到的写数据;读控制模块包括输出MUX_REG和输出选择 调度器,输出MUX_REG内部包括读寄存器,输出MUX_REG根据输出选择调度器选择控制获取 读数据;动态重配置接口的输出端连接输入MUX_REG和输出MUX_REG。 其进一步的技术方案为,两个块状SRAM的端口为1R1W,在读写一个块状SRAM时,块 状SRAM采用握手接口,当读写未完成时给出忙碌指示信号,读写控制模块采用乒乓操作两 个块状SRAM; 输入MUX_REG通过输入选择调度器查询未给出忙碌指示信号的处于空闲状态的块 状SRAM并写入获取到的写数据,地址指示标志电路将写入数据的的块状SRAM的相应地址的 指示标志位的状态置为新状态、将另一个块状SRAM的同一地址的指示标志位的状态置为旧 状态; 输出MUX_REG通过输出选择调度器查询相应地址的地址标志位的状态为新状态的 块状SRAM并获取读数据输出。 其进一步的技术方案为,输入MUX_REG利用写寄存器对获取到的写数据寄存一拍 后选择控制写入其中一个块状SRAM中;输出MUX_REG利用读寄存器对获取到的读数据寄存 一拍后输出。 其进一步的技术方案为,当输出MUX_REG连续两个周期从同一个块状SRAM中获取 到读数据时,输出MUX_REG利用读寄存器对第一个周期获取到的读数据寄存一拍后输出、对 第二个周期获取到的读数据直接输出。 其进一步的技术方案为,当出现读写同地址同周期的情况时,块状存储单元支持 写穿透模式,输入MUX_REG将获取到的写数据直接传输输出MUX_REG输出,或者,输入MUX_ REG利用写寄存器对获取到的写数据寄存一拍后传输到输出MUX_REG输出。 其进一步的技术方案为,当块状存储单元从普通工作模式切换至高速工作模式 时,块状存储单元保留其中一个块状SRAM中的数据,并将保留数据的块状SRAM中所有地址 的指示标志位都置为新状态,将另一个块状SRAM中所有地址的指示标志位都置为旧状态。 其进一步的技术方案为,块状存储单元用于FPGA中,块状存储模块靠近FPGA内部 的高速处理单元布设,高速接口总线连接高速处理单元,高速处理单元包括CPU和AI中的至 少一种,普通接口总线连接FPGA内部的互连单元。 本发明的有益技术效果是: 本申请公开了一种基于动态可重配技术的块状存储单元,该块状存储单元通过特 殊的物理布局和设计,其工作模式可以在高速和普通两者之间动态切换,当需要使用高速 5 CN 111599390 A 说 明 书 3/5 页 处理单元时可以工作在高速工作模式下,两个块状SRAM并行工作,其最高性能可达到该工 艺节点寄存器REG的性能,系统整体性能得到提升;当无需使用高速处理单元时可以工作在 普通工作模式下,两个块状SRAM串行工作配置成普通的SRAM复用给基本逻辑单元。通过两 个块状SRAM可以实现两种工作模式的切换,复用率高,可以达到性能和资源的平衡,适用于 多种使用场景,灵活便利适应各规模的FPGA。 附图说明 图1是本申请的块状存储单元的逻辑结构示意图。 图2是本申请的块状存储单元两种工作模式下的有效地址宽度示意图。 图3是本申请的块状存储单元在FPGA中的布设示意图。