技术摘要:

本发明提供一种沟槽隔离结构的形成方法及沟槽隔离结构。所述形成方法针对基片上较窄的一类沟槽和较宽的二类沟槽,先在预处理基片上形成填孔能力较弱的第一填充层,第一填充层悬空沉积在一类沟槽的开口处,且覆盖二类沟槽的内表面,之后进行第一平坦化工艺将高于预处理 全部

背景技术:

在集成电路制造中,对于在基底上制作的各个独立器件例如不同的存储单元之间 的隔离,多采用形成STI(Shallow Trench Isolation,浅沟槽隔离)的方法。一种常用的制 作STI的方法包括以下过程:先在基底上形成垫氧化层和氮化硅层;然后在选定区域依次刻 蚀氮化硅层、垫氧化层以及基底从而形成隔离沟槽;接着在基底上沉积隔离介质并进行CMP (Chemical Mechanical Polishing,化学机械研磨),使得填充在隔离沟槽中的隔离介质和 氮化硅层基本齐平。 在上述STI的制作过程中,为了填满隔离沟槽并留出CMP处理的窗口,在CMP之前, 沉积在基底上的隔离介质较厚,且隔离介质常常是起伏不平的,相对来讲,对于同一基底, 在隔离沟槽较窄而氮化硅(作为研磨阻挡材料)分布较密集的区域,高于氮化硅层的隔离介 质较厚,而在隔离沟槽较宽而氮化硅分布较稀疏的区域,高于氮化硅层的隔离介质较薄。为 了达到使填充在隔离沟槽中的隔离介质均能和氮化硅层基本齐平的目的,CMP的时间很长, 所获得的STI表面平整度较差,尤其是,在隔离沟槽较宽而氮化硅分布较稀疏的区域,往往 容易产生较为明显的凹陷(dishing)。STI的平整度会影响后续在基底上制作的元器件的性 能。 为了减小CMP后在隔离介质上形成的凹陷,在CMP之前,一种方法是利用图形化的 光阻进行保护,把厚度较大的隔离介质去掉一部分,以缩短CMP时间。还有一种方法是在宽 隔离沟槽中增加研磨阻挡结构而获得多个密集的窄沟槽(dummy trench),避免稀疏区域的 隔离介质在CMP过程中产生凹陷。但是这些方法均需用到光阻及光刻工艺,过程复杂且成本 较高。

技术实现要素:

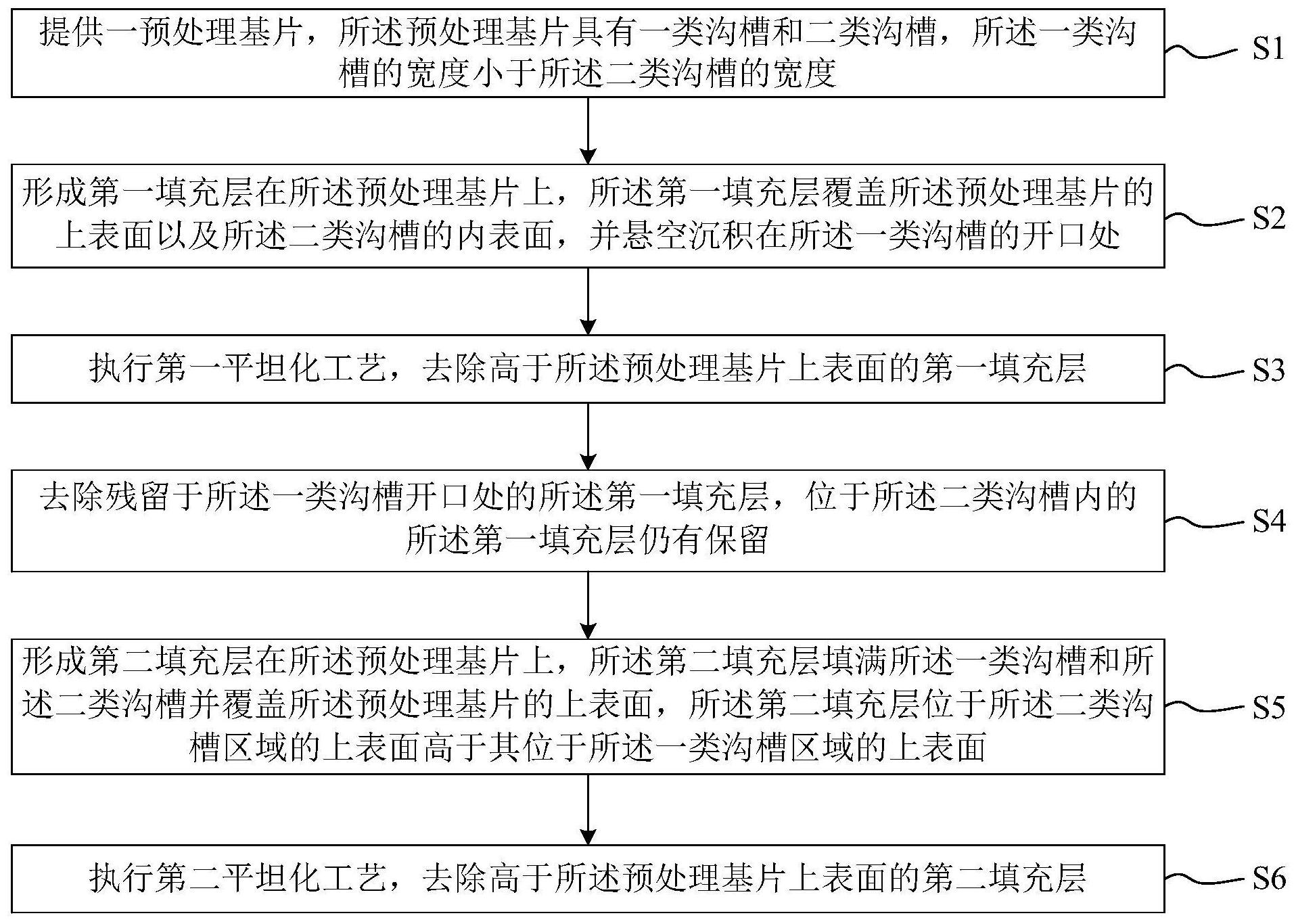

为了提高沟槽隔离结构的表面平整度,简化工艺,本发明提供一种沟槽隔离结构 的形成方法。本发明另外提供一种半导体器件。 一方面,本发明提供一种沟槽隔离结构的形成方法,包括以下步骤: 提供一预处理基片,所述预处理基片具有一类沟槽和二类沟槽,所述一类沟槽的 宽度小于所述二类沟槽的宽度; 形成第一填充层在所述预处理基片上,所述第一填充层覆盖所述预处理基片的上 表面以及所述二类沟槽的内表面,并悬空沉积在所述一类沟槽的开口处; 执行第一平坦化工艺,去除高于所述预处理基片上表面的所述第一填充层; 去除残留于所述一类沟槽开口处的所述第一填充层,位于所述二类沟槽内的所述 第一填充层仍有保留; 3 CN 111584419 A 说 明 书 2/9 页 形成第二填充层在所述预处理基片上,所述第二填充层填满所述一类沟槽和所述 二类沟槽并覆盖所述预处理基片的上表面,所述第二填充层位于所述二类沟槽区域的上表 面高于其位于所述一类沟槽区域的上表面;以及, 执行第二平坦化工艺,去除高于所述预处理基片上表面的所述第二填充层。 可选的,在形成所述第一填充层之前,还包括: 形成保护层在所述预处理基片上,所述保护层保形地覆盖所述一类沟槽和所述二 类沟槽的内表面以及所述预处理基片的上表面。 可选的,所述保护层包括线形氧化层和线形氮化层,所述线形氧化层保形地覆盖 所述一类沟槽和所述二类沟槽的内表面以及所述预处理基片的上表面,所述线形氮化层保 形地覆盖所述线形氧化层的表面。 可选的,在去除残留于所述一类沟槽开口处的所述第一填充层时,所述第一填充 层和所述线形氮化层的刻蚀选择比大于10。 可选的,所述第一填充层采用PE-TEOS工艺或者LP-TEOS工艺形成。 可选的,去除残留于所述一类沟槽开口处的所述第一填充层的方法包括依次执行 的湿法蚀刻和超声波清洗。 可选的,所述第二填充层采用高密度等离子体沉积工艺或高深宽比化学气相沉积 工艺形成。 可选的,所述第一平坦化工艺和所述第二平坦化工艺均采用化学机械研磨。 可选的,所述二类沟槽的宽度是所述一类沟槽宽度的至少五倍。 一方面,本发明提供一种沟槽隔离结构,所述沟槽隔离结构利用上述形成方法形 成。 本发明提出的沟槽隔离结构的形成方法,具有以下优点: 一方面,所述形成方法针对预处理基片上的一类沟槽和二类沟槽,先形成第一填 充层,第一填充层的填孔能力较弱,由于第一沟槽的深宽比较大,因此第一填充层只能悬空 沉积在一类沟槽的开口处,由于二类沟槽较宽,深宽比相对较小,因此第一填充层能够覆盖 二类沟槽的内表面,之后进行第一平坦化工艺将高于预处理基片上表面的第一填充层去 除,然后去除位于一类沟槽开口处的第一填充层,保留在二类沟槽内表面的第一填充层抬 高了二类沟槽的底面,在形成第二填充层时,由于二类沟槽底面被抬高,可以使第二填充层 位于所述二类沟槽区域的上表面高于位于所述一类沟槽区域的上表面,在执行第二平坦化 工艺时,二类沟槽区域的研磨量较一类沟槽区域大,从而在完成第二平坦化工艺后,在二类 沟槽区域发生凹陷(dishing)问题的风险较低,有助于提高沟槽隔离结构的表面平整度; 另一方面,所述形成方法中,由于先利用第一填充层抬高了二类沟槽的底面,第二 填充层的厚度可以沉积得较薄,只要能够填满一类沟槽和二类沟槽并保留一定的平坦化窗 口即可,进而,第二平坦化工艺的时间相对于现有的CMP工艺可以缩短,有助于提高所形成 的沟槽隔离结构的表面平整度; 再一方面,所述形成方法在第二平坦化工艺前,二类沟槽区域上方的第二填充材 料比二类沟槽区域周围沉积的更厚,该过程不需要采用光阻及光刻工艺,实施方便,成本较 低。 本发明提出的沟槽隔离结构利用上述方法形成,由于利用上述形成方法可以得到 4 CN 111584419 A 说 明 书 3/9 页 平整度较佳的表面,因而沟槽隔离结构的质量较高。 附图说明 图1A至图1D是利用现有的一种STI形成方法制作STI的剖面示意图。 图2是本发明实施例的沟槽隔离结构的形成方法的流程示意图。 图3A至图3G是利用本发明实施例的沟槽隔离结构的形成方法在形成过程中的剖 面结构示意图。 附图标记说明: 100、200-半导体衬底;101、201-垫氧化层;102-氮化硅层;202-硬掩膜层;10-隔离 沟槽;103-隔离介质;11-凹陷;20-一类沟槽;30-二类沟槽;203-线形氧化层;204-线形氮化 层;205-第一填充层;206-第二填充层。