技术摘要:

本发明的范例实施例提供一种信号校正电路、存储器存储装置及信号校正方法。所述信号校正电路包括第一相位内插器、第二相位内插器、相位检测器、控制电路及延迟电路。第一相位内插器用以接收多个第一信号并根据第一信号产生多个第一正交信号。第二相位内插器用以根据第 全部

背景技术:

数码相机、移动电话与MP3播放器在这几年来的成长十分迅速,使得消费者对存储 媒体的需求也急速增加。由于可复写式非易失性存储器模块(rewritable non-volatile memory module)(例如,快闪存储器)具有数据非易失性、省电、体积小,以及无机械结构等 特性,所以非常适合内建于上述所举例的各种可携式多媒体装置中。 在信号传输过程中,时脉信号中的同相(in phase)分量信号与正交(quadrature) 分量信号彼此可能不匹配,例如,同相分量信号与正交分量信号之间的相位差可能不为90 度,从而影响信号分析效能。在某些应用中,虽可通过互斥或(Exclusive OR,XOR)闸来检测 同相分量信号与正交分量信号之间的不匹配,但在实务上,互斥或闸的非理想效应可能会 降低检测结果的正确性,进而降低。

技术实现要素:

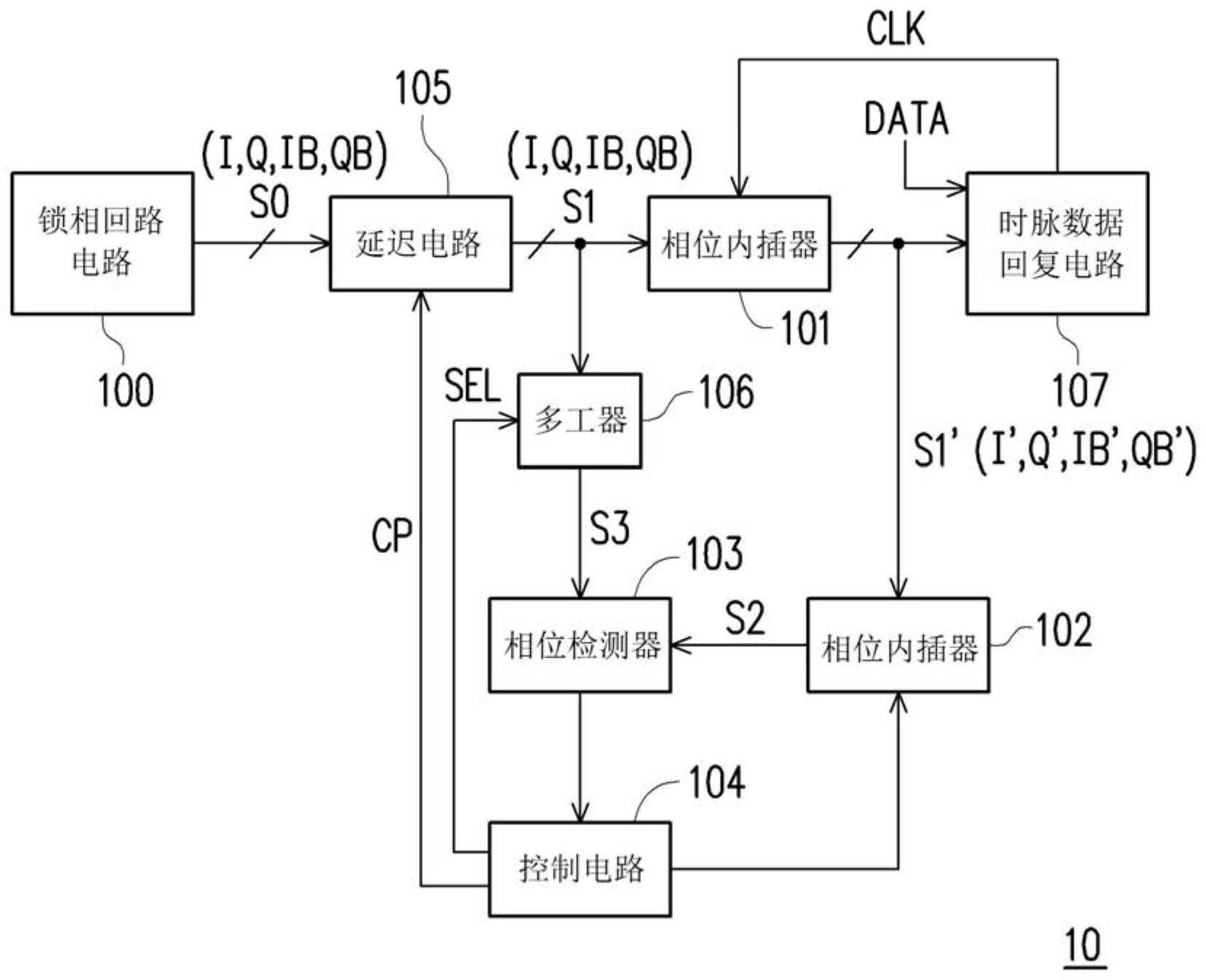

本发明提供一种信号校正电路、存储器存储装置及信号校正方法,可提高对于不 匹配的信号的校正效率。 本发明的范例实施例提供一种信号校正电路,其包括第一相位内插器、第二相位 内插器、相位检测器、控制电路及延迟电路。第一相位内插器用以接收多个第一信号并根据 所述第一信号产生多个第一正交信号。第二相位内插器连接至所述第一相位内插器并用以 根据所述第一正交信号产生第二信号。相位检测器连接至所述第二相位内插器并用以检测 所述第二信号与所述第一信号的其中之一之间的相位差。控制电路连接至所述相位检测器 并用以根据所述相位差产生校正参数。延迟电路连接至所述第一相位内插器与所述控制电 路并用以根据所述校正参数调整所述第一信号的至少其中之一,以使所述第一信号包括多 个第二正交信号。 在本发明的一范例实施例中,所述第一相位内插器根据所述第一信号产生所述第 一正交信号的操作包括:对所述第一信号中的同相分量信号与正交分量信号执行相位内 插,以产生所述第一正交信号的其中之一。 在本发明的一范例实施例中,所述控制电路根据所述相位差产生所述校正参数的 操作包括:根据所述相位差与所述第一信号中的同相分量信号与正交分量信号之间的预设 正交关系,产生所述校正参数。 在本发明的一范例实施例中,所述控制电路根据所述相位差与所述第一信号中的 所述同相分量信号与所述正交分量信号之间的所述预设正交关系,产生所述校正参数的操 作包括:将所述第二信号的相位设定为第一相位;获得所述第一相位与所述同相分量信号 的相位之间的第一差值;将所述第二信号的所述相位设定为第二相位;获得所述第二相位 5 CN 111585547 A 说 明 书 2/11 页 与所述正交分量信号的相位之间的第二差值;以及根据所述第一差值、所述第二差值及所 述同相分量信号与所述正交分量信号之间的所述预设正交关系,产生所述校正参数。 在本发明的一范例实施例中,所述延迟电路根据所述校正参数调整所述第一信号 的所述至少其中之一,以使所述第一信号包括所述第二正交信号的操作包括:根据所述校 正参数延迟所述第一信号中的同相分量信号与正交分量信号的至少其中之一,以使所述同 相分量信号与所述正交分量信号彼此正交。 在本发明的一范例实施例中,所述的信号校正电路还包括多工器,其连接至所述 延迟电路与所述相位检测器。所述多工器用以根据选择信号将所述第一信号的所述其中之 一传递至所述相位检测器。 在本发明的一范例实施例中,所述的信号校正电路还包括时脉数据回复电路,其 连接至所述第一相位内插器。所述时脉数据回复电路用以接收所述第二正交信号与数据信 号并产生输出时脉。 本发明的范例实施例另提供一种存储器存储装置,其包括连接接口单元、可复写 式非易失性存储器模块及存储器控制电路单元。所述连接接口单元用以连接至主机系统。 所述存储器控制电路单元连接至所述连接接口单元与所述可复写式非易失性存储器模块。 所述连接接口单元包括信号校正电路。所述信号校正电路用以接收多个第一信号并根据所 述第一信号产生多个第一正交信号。所述信号校正电路还用以根据所述第一正交信号产生 第二信号。所述信号校正电路还用以检测所述第二信号与所述第一信号的其中之一之间的 相位差。所述信号校正电路还用以根据所述相位差产生校正参数。所述信号校正电路还用 以根据所述校正参数调整所述第一信号的至少其中之一,以使所述第一信号包括多个第二 正交信号。 在本发明的一范例实施例中,所述信号校正电路根据所述第一信号产生所述第一 正交信号的操作包括:对所述第一信号中的同相分量信号与正交分量信号执行相位内插, 以产生所述第一正交信号的其中之一。 在本发明的一范例实施例中,所述信号校正电路根据所述相位差产生所述校正参 数的操作包括:根据所述相位差与所述第一信号中的同相分量信号与正交分量信号之间的 预设正交关系,产生所述校正参数。 在本发明的一范例实施例中,所述信号校正电路根据所述相位差与所述第一信号 中的所述同相分量信号与所述正交分量信号之间的所述预设正交关系,产生所述校正参数 的操作包括:将所述第二信号的相位设定为第一相位;获得所述第一相位与所述同相分量 信号的相位之间的第一差值;将所述第二信号的所述相位设定为第二相位;获得所述第二 相位与所述正交分量信号的相位之间的第二差值;以及根据所述第一差值、所述第二差值 及所述同相分量信号与所述正交分量信号之间的所述预设正交关系,产生所述校正参数。 在本发明的一范例实施例中,所述信号校正电路根据所述校正参数调整所述第一 信号的所述至少其中之一,以使所述第一信号包括所述第二正交信号的操作包括:根据所 述校正参数延迟所述第一信号中的同相分量信号与正交分量信号的至少其中之一,以使所 述同相分量信号与所述正交分量信号彼此正交。 在本发明的一范例实施例中,所述信号校正电路还用以经由多工器将所述第一信 号的所述其中之一传递至相位检测器,以检测所述第二信号与所述第一信号的所述其中之 6 CN 111585547 A 说 明 书 3/11 页 一之间的所述相位差。 在本发明的一范例实施例中,所述信号校正电路还用以接收所述第二正交信号与 数据信号并产生输出时脉。 本发明的范例实施例另提供一种信号校正方法,其用于存储器存储装置。所述信 号校正方法包括:接收多个第一信号并根据所述第一信号产生多个第一正交信号;根据所 述第一正交信号产生第二信号;检测所述第二信号与所述第一信号的其中之一之间的相位 差;根据所述相位差产生校正参数;以及根据所述校正参数调整所述第一信号的至少其中 之一,以使所述第一信号包括多个第二正交信号。 在本发明的一范例实施例中,根据所述第一信号产生所述第一正交信号的步骤包 括:对所述第一信号中的同相分量信号与正交分量信号执行相位内插,以产生所述第一正 交信号的其中之一。 在本发明的一范例实施例中,根据所述相位差产生所述校正参数的步骤包括:根 据所述相位差与所述第一信号中的同相分量信号与正交分量信号之间的预设正交关系,产 生所述校正参数。 在本发明的一范例实施例中,根据所述相位差与所述第一信号中的所述同相分量 信号与所述正交分量信号之间的所述预设正交关系,产生所述校正参数的步骤包括:将所 述第二信号的相位设定为第一相位;获得所述第一相位与所述同相分量信号的相位之间的 第一差值;将所述第二信号的所述相位设定为第二相位;获得所述第二相位与所述正交分 量信号的相位之间的第二差值;以及根据所述第一差值、所述第二差值及所述同相分量信 号与所述正交分量信号之间的所述预设正交关系,产生所述校正参数。 在本发明的一范例实施例中,根据所述校正参数调整所述第一信号的所述至少其 中之一,以使所述第一信号包括所述第二正交信号的步骤包括:根据所述校正参数延迟所 述第一信号中的同相分量信号与正交分量信号的至少其中之一,以使所述同相分量信号与 所述正交分量信号彼此正交。 在本发明的一范例实施例中,所述的信号校正方法还包括:经由多工器将所述第 一信号的所述其中之一传递至相位检测器,以检测所述第二信号与所述第一信号的所述其 中之一之间的所述相位差。 在本发明的一范例实施例中,所述的信号校正方法还包括:由时脉数据回复电路 接收所述第二正交信号与数据信号并产生输出时脉。 基于上述,第一相位内插器可接收多个第一信号并根据所述第一信号产生多个第 一正交信号。第二相位内插器可根据所述第一正交信号产生第二信号。相位检测器可检测 所述第二信号与所述第一信号的其中之一之间的相位差。控制电路可根据所述相位差产生 校正参数。然后,延迟电路可根据所述校正参数调整所述第一信号的至少其中之一,以使所 述第一信号包括多个第二正交信号。藉此,可有效将第一信号中可能不匹配的信号校正为 正交信号,从而提高对于不匹配之信号的校正效率。 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详 细说明如下。 7 CN 111585547 A 说 明 书 4/11 页 附图说明 图1是根据本发明的一范例实施例所示出的信号校正电路的示意图; 图2是根据本发明的一范例实施例所示出的第一信号的相位的示意图; 图3是根据本发明的一范例实施例所示出的第一正交信号的相位的示意图; 图4是根据本发明的一范例实施例所示出的决定校正参数的示意图; 图5是根据本发明的一范例实施例所示出的调整第一信号的相位的示意图; 图6是根据本发明的一范例实施例所示出的信号校正方法的流程图; 图7是根据本发明的一范例实施例所示出的主机系统、存储器存储装置及输入/输 出(I/O)装置的示意图; 图8是根据本发明的另一范例实施例所示出的主机系统、存储器存储装置及I/O装 置的示意图; 图9是根据本发明的另一范例实施例所示出的主机系统与存储器存储装置的示意 图; 图10是根据本发明的一范例实施例所示出的存储器存储装置的概要方块图。 附图标记说明 10:信号校正电路 100:锁相回路电路 101、102:相位内插器 103:相位检测器 104:控制电路 105:延迟电路 106:多工器 107:时脉数据回复电路 S601:步骤(接收多个第一信号并根据第一信号产生多个第一正交信号) S602:步骤(根据第一正交信号产生第二信号) S603:步骤(检测第二信号与第一信号的其中之一之间的相位差) S604:步骤(根据相位差产生校正参数) S605:步骤(根据校正参数调整第一信号的至少其中之一,以使第一信号包括多个 第二正交信号) 71、91:主机系统 710:系统总线 711:处理器 712:随机存取存储器 713:只读存储器 714:数据传输接口 72:输入/输出(I/O)装置 80:主机板 801:U盘 802:存储卡 8 CN 111585547 A 说 明 书 5/11 页 803:固态硬盘 804:无线存储器存储装置 805:全球定位系统模块 806:网络接口卡 807:无线传输装置 808:键盘 809:屏幕 810:喇叭 92:SD卡 93:CF卡 94:嵌入式存储装置 941:嵌入式多媒体卡 942:嵌入式多芯片封装存储装置 1002:连接接口单元 1004:存储器控制电路单元 1006:可复写式非易失性存储器模块