技术摘要:

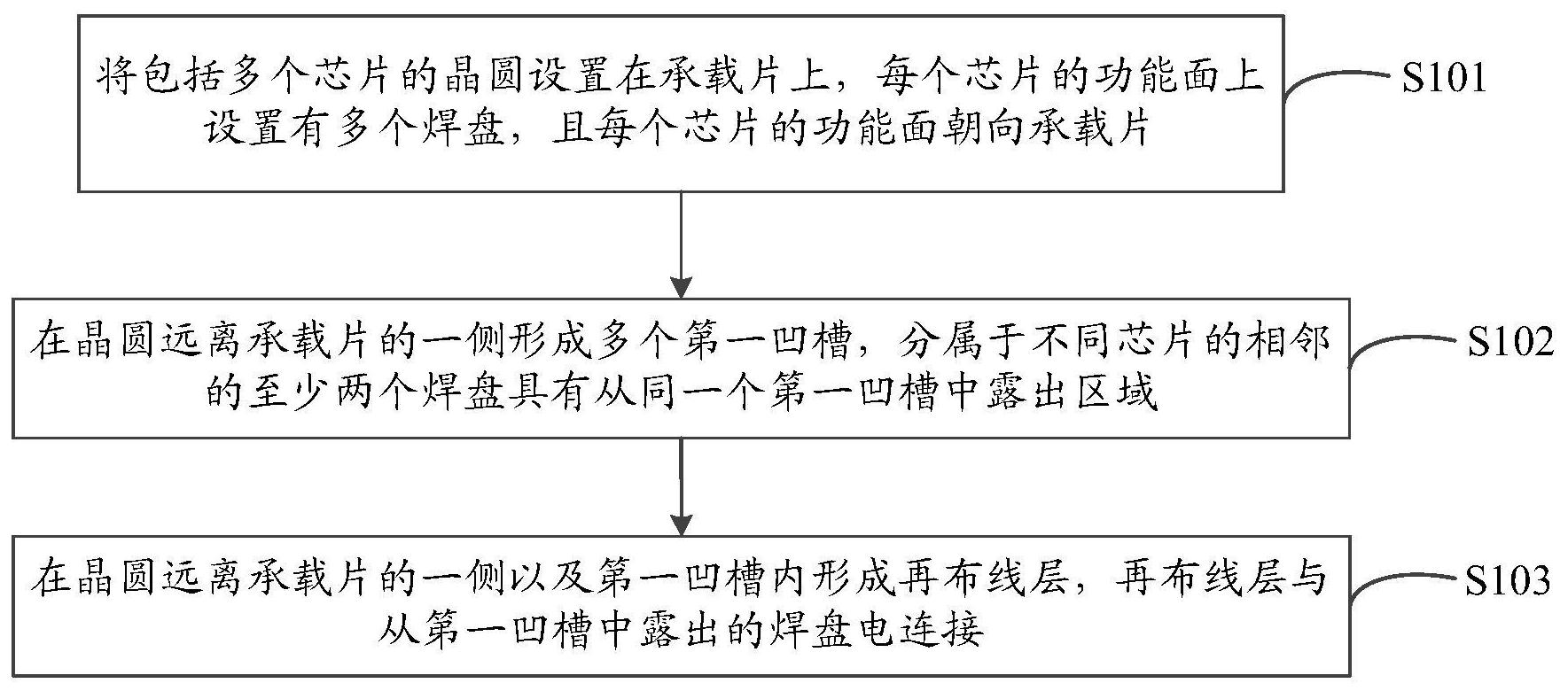

本申请公开了一种晶圆级封装方法,该方法包括:将包括多个芯片的晶圆设置在承载片上,每个芯片的功能面上设置有多个焊盘,且每个芯片的功能面朝向承载片;在晶圆远离承载片的一侧形成多个第一凹槽,分属于不同芯片的相邻的至少两个焊盘具有从同一个第一凹槽中露出区域 全部

背景技术:

晶圆级封装(WLP,Wafer Level Package)的一般定义为直接在晶圆上进行大多数 或是全部的封装测试程序,之后再进行切割制成单颗组件。其主要应用于手机放大器与前 端模块、CMOS图像传感器等各式半导体产品。 在进行晶圆级封装时,有些芯片需要在芯片背面上开设通孔并将芯片正面的信号 从通孔内引到芯片的背面,对于这类芯片,由于开设通孔的尺寸小,工艺较复杂且难度较 大,在封装制备过程中容易出现裂片等问题,芯片的良品率较低。

技术实现要素:

本申请主要解决的技术问题是提供一种晶圆级封装方法,在开设第一凹槽时,第 一凹槽横跨两个芯片上相邻的焊盘,第一凹槽的尺寸较大能够降低开设凹槽时对精度的要 求,减小芯片在加工过程中断裂的风险 为解决上述技术问题,本申请采用的一个技术方案是:提供一种晶圆级封装方法, 该晶圆级封装方法包括: 将包括多个芯片的晶圆设置在承载片上,每个所述芯片的功能面上设置有多个焊 盘,且每个所述芯片的所述功能面朝向所述承载片;在所述晶圆远离所述承载片的一侧形 成多个第一凹槽,分属于不同芯片的相邻的至少两个所述焊盘具有从同一个所述第一凹槽 中露出区域;在所述晶圆远离所述承载片的一侧以及所述第一凹槽内形成再布线层,所述 再布线层与从所述第一凹槽中露出的所述焊盘电连接。 其中,所述在所述晶圆远离所述承载片的一侧形成多个第一凹槽,包括:利用蚀刻 工艺在所述晶圆远离所述承载片的一侧形成多个所述第一凹槽,且所述焊盘从所述第一凹 槽中露出的区域面积超过所述焊盘面积的一半。 其中,所述将包括多个芯片的晶圆设置在承载片上,包括:利用键合胶将所述多个 芯片的所述功能面与所述承载片固定连接;研磨所述晶圆远离所述承载片的一侧以使所述 晶圆的厚度减小。 其中,所述在所述晶圆远离所述承载片的一侧以及所述第一凹槽内形成再布线层 之前包括:在所述晶圆远离所述承载片的一侧形成绝缘层,所述绝缘层对应所述第一凹槽 的位置设置有第一开口,所述第一凹槽位置处的所有所述焊盘包括从所述第一开口中露出 的部分;所述在所述晶圆远离所述承载片的一侧以及所述第一凹槽内形成再布线层,包括: 在所述绝缘层和从所述绝缘层中露出的所述焊盘表面形成所述再布线层。 其中,所述第一开口的宽度小于所述第一凹槽的宽度,所述绝缘层覆盖所述晶圆 远离所述承载片的一侧以及所述第一凹槽的侧壁,所述再布线层与从所述第一开口中露出 的所述焊盘的表面电连接。 4 CN 111554585 A 说 明 书 2/9 页 其中,所述在所述晶圆远离所述承载片的一侧以及所述第一凹槽内形成再布线层 之后,包括:在所述再布线层上形成保护层,所述保护层覆盖所述再布线层以及未被所述再 布线层覆盖的所述焊盘;在所述保护层表面形成第二开口,所述再布线层从所述第二开口 中露出;在所述第二开口内形成焊球。 其中,所述在所述第二开口内形成焊球之后,还包括:在所述承载片设置有所述晶 圆一侧形成第一塑封层,所述焊球从所述第一塑封层中露出;切割掉相邻所述芯片之间的 部分所述承载片、所述晶圆以及所述第一塑封层。 其中,所述在所述第二开口内形成焊球之后,还包括:切割掉相邻所述芯片之间的 部分所述承载片以及所述晶圆,以获得包含单颗所述芯片的芯片封装体。 其中,所述切割掉相邻所述芯片之间的部分所述承载片以及所述晶圆,以获得包 含单颗所述芯片的芯片封装体之后,包括:将多个所述芯片封装体黏贴在载板上;在所述芯 片封装体的两侧以及所述芯片封装体远离所述载板的一侧形成第二塑封层,所述焊球从所 述第二塑封层中露出。 其中,所述在所述芯片封装体的两侧以及所述芯片封装体远离所述载板的一侧形 成第二塑封层之后,包括:切割掉相邻的所述芯片封装体之间的所述第二塑封层;将所述载 板去除。 本申请的有益效果是:本申请在晶圆上背离芯片功能面的一侧开设第一凹槽,该 第一凹槽横跨两个芯片上相邻的焊盘,分属于不同芯片的相邻的至少两个焊盘具有从同一 个第一凹槽中露出区域,进而在晶圆背面以及第一凹槽内形成再布线层,将芯片的功能面 上的信号引到芯片的非功能面一侧,在开设第一凹槽时第一凹槽的尺寸较大能够降低开设 凹槽时对精度的要求,减小了芯片在加工过程中断裂的风险。 附图说明 为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使 用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于 本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他 的附图。其中: 图1是本申请晶圆级封装方法一实施方式的流程示意图; 图2a是图1中步骤S101对应的一实施方式的剖视结构示意图; 图2b是图1中步骤S102对应的一实施方式的剖视结构示意图; 图2c是图1中步骤S103对应的一实施方式的剖视结构示意图; 图3是图1中步骤S103之后对应的一实施方式的流程示意图; 图4a是图3中步骤S201对应的一实施方式的剖视结构示意图; 图4b是图3中步骤S202对应的一实施方式的剖视结构示意图; 图4c是图3中步骤S203对应的一实施方式的剖视结构示意图; 图5是图3中步骤S203之后对应的一实施方式的流程示意图; 图6a是图5中步骤S301对应的一实施方式的剖视结构示意图; 图6b是图5中步骤S302对应的一实施方式的剖视结构示意图; 图7是图3中步骤S203之后对应的另一实施方式的流程示意图; 5 CN 111554585 A 说 明 书 3/9 页 图8a是图7中步骤S401对应的一实施方式的剖视结构示意图; 图8b是图7中步骤S402对应的一实施方式的剖视结构示意图; 图8c是图7中步骤S403对应的一实施方式的剖视结构示意图; 图8d是图7中步骤S403之后对应的一实施方式的剖视结构示意图; 图8e是去除图8d中的载板后获得的芯片封装体一实施方式的剖视结构示意图; 图9是本申请晶圆级封装体一实施方式的剖视结构示意图; 图10是本申请晶圆级封装体另一实施方式的剖视结构示意图; 图11是本申请芯片封装体一实施方式的剖视结构示意图; 图12是本申请芯片封装体另一实施方式的剖视结构示意图。