技术摘要:

本发明提供的可软件定义的存算一体芯片的运算控制方法和装置,根据运算任务获取配置信息和有限状态机信息;根据配置信息配置芯片中各模块,实现芯片中电路结构的动态配置;根据有限状态机信息控制芯片中各模块的工作时序,以利用配置后的芯片结构实现运算任务。其中, 全部

背景技术:

闪存是一种非易失性存储器,其通过调控闪存晶体管的阈值电压来实现数据的存 储。根据闪存晶体管和阵列结构的不同,闪存主要分为NOR-型闪存和NAND-型闪存。NAND-型 闪存的读写以页和块为单位,其容量大、成本低,广泛应用于大规模独立式存储器;NOR-型 闪存支持数据的随机存取,与NAND-型闪存相比,密度较低、容量较小、成本较高,主要应用 于嵌入式存储器。 近年来,为了解决传统冯诺依曼计算体系结构瓶颈,存内计算(Computing-In- Memory,CIM)芯片结构得到人们的广泛关注,其基本思想是直接利用存储器进行逻辑计算, 从而减少存储器与处理器之间的数据传输量以及传输距离,降低功耗的同时提高性能。 现有存算一体芯片结构一经定制,其电路结构即被固定下来,不能根据实际任务 进行灵活调节,不能适应实际多变的神经网络运算的需要。近年来,软件定义芯片技术受到 业界的广泛青睐,其核心思想是根据实际应用需求,对芯片结构进行动态重构,通过软件定 义方法控制重构后的芯片,完成不同的任务,从而实现高灵活性,低成本。但是,到目前为 止,还没有可软件定义的存算一体芯片及其控制方法。

技术实现要素:

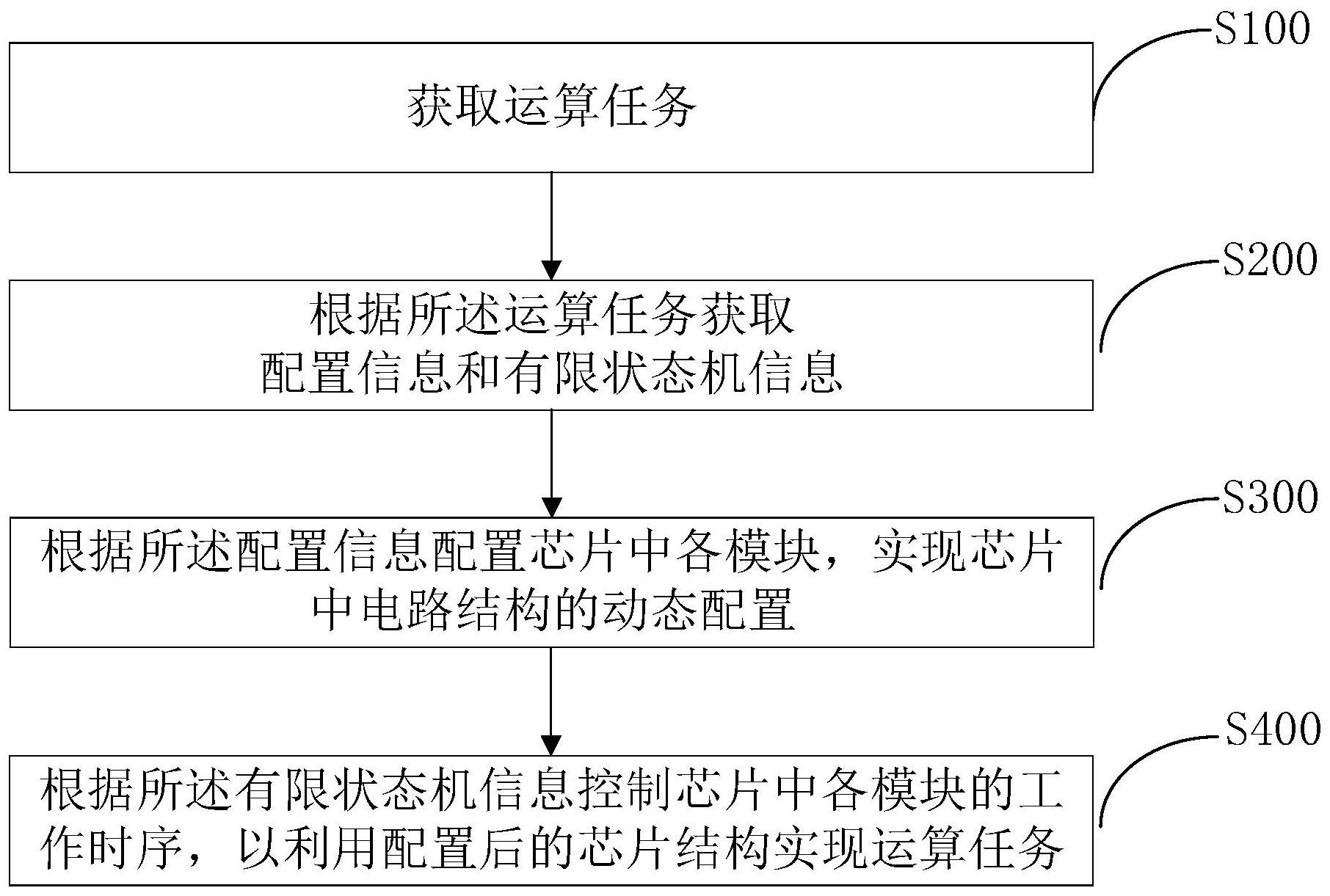

有鉴于此,本发明提供了一种可软件定义的存算一体芯片的运算控制方法和装 置,能够根据运算任务灵活调节芯片结构,适用各种复杂运算场合,尤其适用于神经网络运 算,且ADC、DAC、寄存器、可编程算术运算单元等外围电路能够实现复用,进而减小了电路面 积,适应集成化、小型化的需要。 为了实现上述目的,本发明采用如下技术方案: 第一方面,提供一种可软件定义的存算一体芯片的运算控制方法,包括: 获取运算任务; 根据该运算任务获取配置信息和有限状态机信息; 根据该配置信息配置芯片中各模块,实现芯片中电路结构的动态配置; 根据该有限状态机信息控制芯片中各模块的工作时序,以利用配置后的芯片结构 实现运算任务。 第二方面,提供一种可软件定义的存算一体芯片的运算控制装置,包括: 运算任务获取模块,获取运算任务; 配置信息获取模块,根据该运算任务获取配置信息和有限状态机信息; 芯片结构控制模块,根据该配置信息配置芯片中各模块,实现芯片中电路结构的 动态配置; 5 CN 111611197 A 说 明 书 2/14 页 工作时序控制模块,根据该有限状态机信息控制芯片中各模块的工作时序,以利 用配置后的芯片结构实现运算任务。 存储模块,存储配置信息、运算数据与控制指令; 本发明提供的可软件定义的存算一体芯片的运算控制方法和装置,根据运算任务 获取配置信息和有限状态机信息;根据配置信息配置芯片中各模块,实现芯片中电路结构 的动态配置;根据有限状态机信息控制芯片中各模块的工作时序,以利用配置后的芯片结 构实现运算任务。其中,能够根据运算任务灵活调节芯片结构,适用各种复杂运算场合,尤 其适用于神经网络运算,且ADC、DAC、寄存器、可编程算术运算单元等外围电路能够实现复 用,进而减小了电路面积,适应集成化、小型化的需要。 为让本发明的上述和其他目的、特征和优点能更明显易懂,下文特举较佳实施例, 并配合所附图式,作详细说明如下。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本 发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以 根据这些附图获得其他的附图。 图1为本发明实施例的运算控制方法的流程图; 图2为采用本发明实施例的运算控制方法进行控制的可软件定义的存算一体芯片 的结构图一; 图3为本发明实施例的运算控制方法的流程图二; 图4为采用本发明实施例的运算控制方法进行控制的可软件定义的存算一体芯片 的结构图二; 图5为本发明实施例的运算控制方法的流程图三; 图6示出了一种典型的神经网络结构; 图7示出了图5中步骤S210的具体步骤; 图8为采用本发明实施例的运算控制方法进行控制的可软件定义的存算一体芯片 的结构图三; 图9为本发明实施例的运算控制方法的流程图四; 图10为本发明实施例的运算控制方法的流程图五; 图11为采用本发明实施例的运算控制方法进行控制的可软件定义的存算一体芯 片的结构图四; 图12为本发明实施例中可软件定义的存算一体芯片中闪存处理子阵列的结构图 一; 图13为本发明实施例中可软件定义的存算一体芯片中闪存处理子阵列的结构图 二; 图14为本发明实施例中可软件定义的存算一体芯片中闪存处理子阵列的结构图 三; 图15为步骤S322的具体步骤; 6 CN 111611197 A 说 明 书 3/14 页 图16为采用本发明实施例的运算控制方法进行控制的可软件定义的存算一体芯 片的结构图五; 图17为本发明实施例中可软件定义的存算一体芯片中可编程算术运算单元30的 结构图; 图18为本发明实施例可软件定义的存算一体芯片中可编程算术运算子单元的结 构图; 图19为本发明实施例可软件定义的存算一体芯片中可编程算术运算模块实现复 合运算的示意图; 图20为本发明实施例一种可软件定义的存算一体芯片的运算控制装置的结构图 一。