技术摘要:

本申请实施例提供一种数据处理方法、网络设备、主控板及逻辑芯片,该方法包括:在使能训练过程中,确定采样时钟,采样时钟是原始时钟的N倍;原始时钟是业务板通过数据总线向主控板发送数据时使用的时钟;根据采样时钟对业务板发送的原始训练数据进行采样,得到多个采样 全部

背景技术:

网络设备(如路由器、交换机等)可以包括主控板和业务板(也可以称为子卡),主 控板可通过低电压差分信号(Low Voltage Differential Signaling,LVDS)总线与业务板 连接。例如,主控板通过LVDS总线1与业务板1连接,主控板通过LVDS总线2与业务板2连接, 每个LVDS总线之间均是相互独立的。 LVDS总线由3对差分线组成,如差分线A、差分线B和差分线C。主控板向业务板发送 数据时,通过差分线A向业务板发送时钟信号,并通过差分线B向业务板发送数据。业务板通 过差分线A接收到时钟信号后,根据该时钟信号从差分线B接收数据,从而正确接收数据。但 是,业务板向主控板发送数据时,业务板通过差分线C向主控板发送数据,而无法向主控板 发送时钟信号,导致主控板无法利用时钟信号从差分线C接收数据,从而无法正确接收数 据。

技术实现要素:

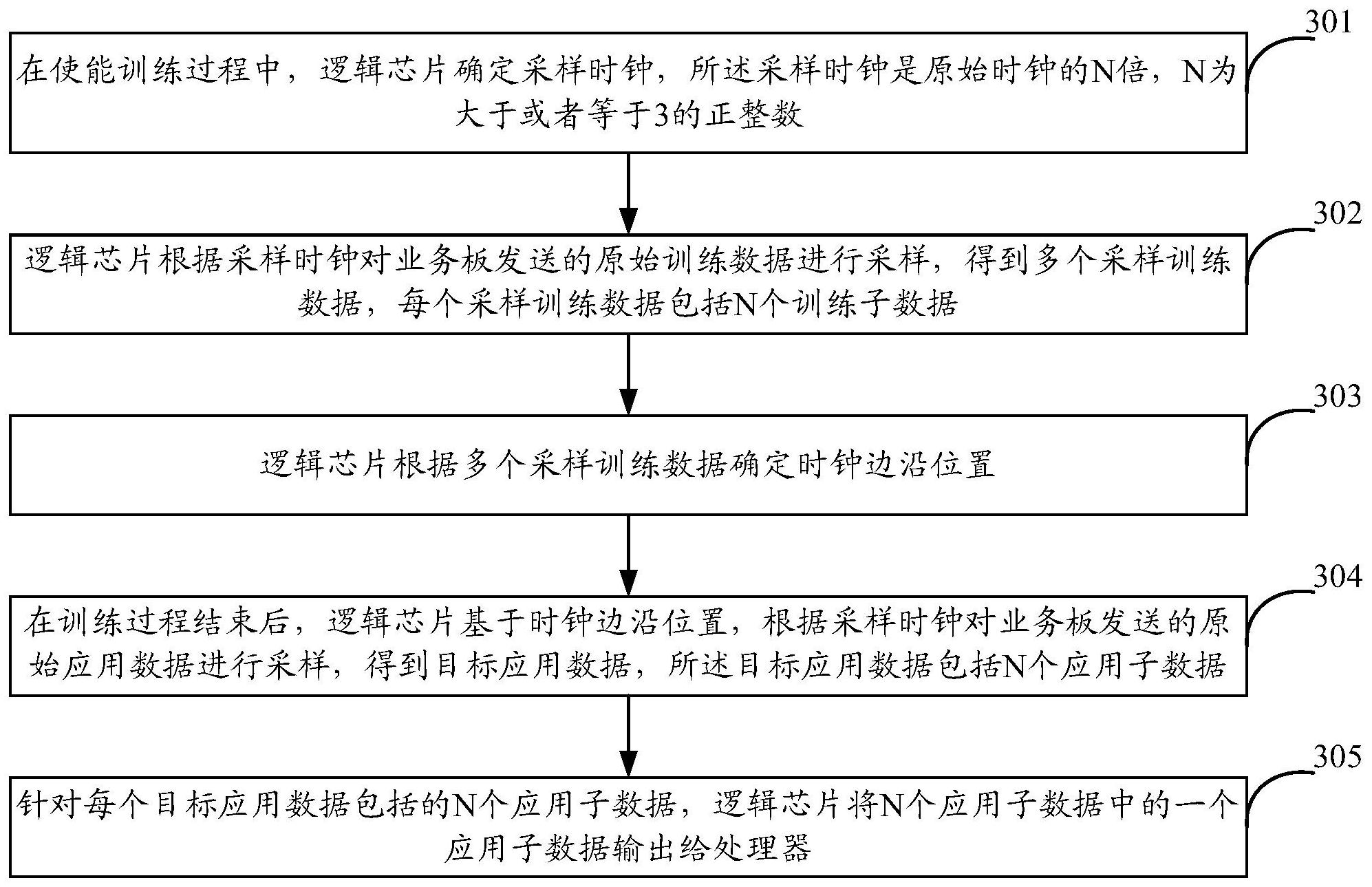

本申请提供一种数据处理方法,网络设备包括主控板和业务板,所述主控板通过 数据总线与所述业务板连接,所述主控板包括逻辑芯片以及处理器,所述方法应用于所述 逻辑芯片,所述方法包括: 在使能训练过程中,确定采样时钟,所述采样时钟是原始时钟的N倍,所述N为大于 或者等于3的正整数;其中,所述原始时钟是所述业务板通过所述数据总线向所述主控板发 送数据时使用的时钟;根据所述采样时钟对所述业务板发送的原始训练数据进行采样,得 到多个采样训练数据,每个采样训练数据包括N个训练子数据;根据所述多个采样训练数据 确定时钟边沿位置; 在训练过程结束后,基于所述时钟边沿位置,根据所述采样时钟对所述业务板发 送的原始应用数据进行采样,得到目标应用数据,所述目标应用数据包括N个应用子数据; 将所述N个应用子数据中的一个应用子数据输出给处理器。 本申请提供一种逻辑芯片,应用于主控板,所述主控板通过数据总线与业务板连 接,所述主控板还包括处理器,所述逻辑芯片包括: 确定模块,用于在使能训练过程中,确定采样时钟,所述采样时钟是原始时钟的N 倍,N为大于或等于3的正整数;所述原始时钟是所述业务板通过所述数据总线向所述主控 板发送数据时使用的时钟; 采样模块,用于根据所述采样时钟对所述业务板发送的原始训练数据进行采样, 得到多个采样训练数据,每个采样训练数据包括N个训练子数据; 所述确定模块,还用于根据所述多个采样训练数据确定时钟边沿位置; 4 CN 111600784 A 说 明 书 2/13 页 所述采样模块,还用于在训练过程结束后,基于所述时钟边沿位置,根据所述采样 时钟对所述业务板发送的原始应用数据进行采样,得到目标应用数据,所述目标应用数据 包括N个应用子数据; 输出模块,用于将所述N个应用子数据中的一个应用子数据输出给处理器。 本申请提供一种主控板,所述主控板通过数据总线与业务板连接,所述主控板包 括上述的逻辑芯片和处理器;其中: 所述处理器,用于从所述逻辑芯片获取一个应用子数据。 本申请提供一种网络设备,所述网络设备包括主控板和业务板,所述主控板通过 数据总线与所述业务板连接,所述主控板包括上述的逻辑芯片和处理器。 由以上技术方案可见,本申请实施例中,能够利用原始训练数据自动训练时钟边 沿位置,继而利用时钟边沿位置正确采样应用数据,保证读写操作的稳定性。虽然主控板无 法利用时钟信号接收数据,主控板也能够正确接收数据。 附图说明 为了更加清楚地说明本申请实施例或者现有技术中的技术方案,下面将对本申请 实施例或者现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的 附图仅仅是本申请中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据本申 请实施例的这些附图获得其他的附图。 图1A和图1B是本申请一种实施方式中的网络设备的硬件结构图; 图2A和图2B是本申请一种实施方式中的数据采样的示意图; 图3是本申请一种实施方式中的数据处理方法的流程图; 图4A和图4B是本申请一种实施方式中的原始训练数据采样的示意图; 图5是本申请一种实施方式中的移位组合的示意图; 图6是本申请一种实施方式中的逻辑芯片的硬件结构图; 图7是本申请一种实施方式中的网络设备的硬件结构图。