技术摘要:

本发明公开了一种大动态范围半浮栅图像传感器,包括像素阵列、电流处理列级电路和电压处理列级电路,所述像素阵列包括多个像素,每个所述像素均包括半浮栅晶体管和第一电压转换电路,所述第一电压转换电路用于将半浮栅晶体管输出的电流信号转换为电压信号,并分别采样 全部

背景技术:

浮栅器件自从首次提出便一直广泛应用于各类非易失性存储器中,近年来,半浮 栅器件正逐步被应用于图像传感器之中。半浮栅器件可用简单的1T结构实现传统3T CMOS 图像传感器的功能,能够提高填充因子,增大集成度;半浮栅1T像素工作过程中用浮栅来存 储光生电荷,能够输出随光强大小变化的MOS管电流,用以表征图像信息;电流信号可以通 过列级电容跨阻放大器,利用输入电流在反馈电容上积分使之转换为电压信号,其后再由 其他处理电路处理后读出。 动态范围是图像传感器的重要性能参数之一,是表征图像传感器应用环境范围的 指标,由满阱电荷与读出噪声的比值决定。在低背景成像条件下,需要较高的转换增益以及 较低的读出噪声才能够读出微弱的光生信号;在高背景成像条件下,需要较大的满阱电荷 容量才能够储存有效光生信号,避免溢出。因此,对于要求可同时应用于低背景成像条件与 高背景成像条件的大动态范围图像传感器,往往较难设计。 对于半浮栅图像传感器,满阱电荷与转换增益均与光电二极管电容大小直接相 关,很难同时兼顾大满阱与高增益;另外,关于噪声,现有技术可以通过在列级电路中放置 相关电路,能够实现对半浮栅1T像素输出电流的列级相关双采样操作,但由于相关双采样 不是像素级,在消除KTC噪声与固定模式噪声方面有一定的局限。

技术实现要素:

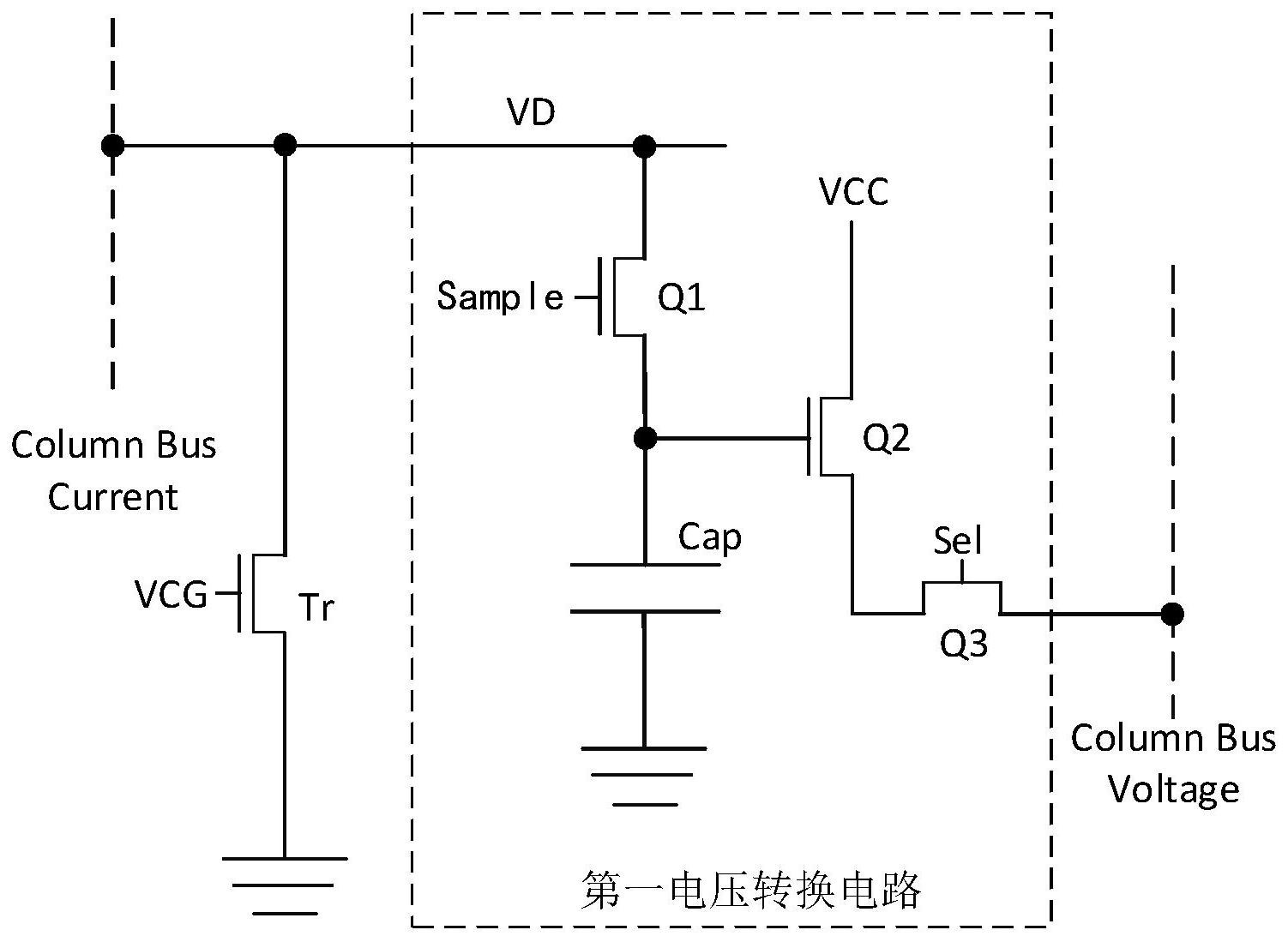

本发明要解决的技术问题是提供了一种同时适用于高背景成像和低背景成像的 大动态范围半浮栅图像传感器。 本发明的技术方案如下: 一种大动态范围半浮栅图像传感器,包括像素阵列、电流处理列级电路和电压处 理列级电路,所述像素阵列包括多个像素,每个所述像素均包括半浮栅晶体管和第一电压 转换电路,所述半浮栅晶体管的源极接地,栅极用于接收该像素对应的第一像素控制信号, 漏极用于接收该像素对应的第二像素控制信号,所述半浮栅晶体管的漏极还通过该像素对 应的像素列级电流总线与所述电流处理列级电路电连接; 每一像素的半浮栅晶体管的漏极还与其第一电压转换电路电连接,所述第一电压 转换电路还通过该像素对应的像素列级电压总线与所述电压处理列级电路电连接,所述第 一电压转换电路用于将半浮栅晶体管输出的电流信号转换为电压信号,并分别采样输出复 位电压和信号电压。 进一步的,所述第一电压转换电路包括采样控制晶体管、电平调节晶体管、输出控 制晶体管和采样电容,所述采样控制晶体管的漏极与半浮栅晶体管的漏极电连接,所述采 样控制晶体管的栅极用于接收一采样控制信号,所述采样控制晶体管的源极与采样电容的 4 CN 111601056 A 说 明 书 2/6 页 正极板电连接,所述采样电容的负极板接地,所述电平调节晶体管的漏极连接供电电压 VCC,栅极与采样电容的正极板电连接,源极与输出控制晶体管的漏极电连接,所述输出控 制晶体管的栅极用于接收一行选信号,源极通过该像素对应的像素列级电压总线与电压处 理列级电路电连接。 进一步的,所述第一电压转换电路的转换增益由采样电容的容值决定。 进一步的,所述半浮栅晶体管的工作过程按时间顺序分为像素复位阶段、复位电 流输出阶段、积分阶段和信号电流输出阶段; 在像素复位阶段的起始时刻,与该像素对应的第一像素控制信号为高电平,与该 像素对应的第二像素控制信号、采样控制信号和输出控制信号均为低电平,使半浮栅晶体 管复位; 在复位电流输出阶段的起始时刻,与该像素对应的第二像素控制信号和采样控制 信号转换为高电平,使半浮栅晶体管输出复位电流,采样电容被复位; 在积分阶段的起始时刻,与该像素对应的第一像素控制信号和采样控制信号转换 为低电平,使半浮栅晶体管处于积分状态;在积分阶段的末期,与该像素对应的输出控制信 号先转换为高电平,然后,与该像素对应的采样控制信号输出一个高电平脉冲,对采样电容 的复位电压进行采样,并输出给所述电压处理列级电路; 在信号电流输出阶段的起始时刻,与该像素对应的第一像素控制信号转换为高电 平,使半浮栅晶体管输出光响应信号电流,采样电容将光响应信号电流转换为光响应信号 电压;然后,与该像素对应的采样控制信号再次输出一个高电平脉冲,对光响应信号电压进 行采样并输出给所述电压处理列级电路。 一种大动态范围半浮栅图像传感器,包括像素阵列、电流处理列级电路和电压处 理列级电路,所述像素阵列包括多个像素子阵列,每个所述像素子阵列均包括第二电压转 换电路和多个像素,每一像素均包括一个半浮栅晶体管,每一像素的半浮栅晶体管的源极 均接地,栅极分别用于接收该像素对应的第一像素控制信号,所述像素子阵列的第一行像 素中,每一像素的半浮栅晶体管的漏极分别用于接收该像素对应的第二像素控制信号,所 述像素子阵列的非第一行像素中,每一像素的半浮栅晶体管的漏极分别与第一行像素中该 列像素的半浮栅晶体管的漏极电连接,所述像素子阵列中每一列像素的半浮栅晶体管的漏 极还分别通过对应的像素列级电流总线与所述电流处理列级电路电连接; 所述像素子阵列的每一列像素中,每一像素的半浮栅晶体管的漏极均与第二电压 转换电路电连接,所述第二电压转换电路还通过该像素子阵列对应的像素列级电压总线与 所述电压处理列级电路电连接,所述第二电压转换电路用于将各像素输出的电流信号进行 累加并转换为电压信号,并分别采样输出累加后的复位电压和信号电压。 进一步的,所述第二电压转换电路包括电平调节晶体管、输出控制晶体管、采样电 容和多个采样控制晶体管,每一所述采样控制晶体管分别与该像素子阵列的一列像素相对 应,每一列像素的半浮栅晶体管的漏极均与对应的采样控制晶体管的漏极电连接,每一采 样控制晶体管的栅极均用于接收一采样控制信号,源极均与采样电容的正极板电连接,所 述采样电容的负极板接地,所述电平调节晶体管的漏极连接供电电压VCC,栅极与采样电容 的正极板电连接,源极与输出控制晶体管的漏极电连接,所述输出控制晶体管的栅极用于 接收一行选信号,源极通过对应的像素列级电压总线与所述电压处理列级电路电连接。 5 CN 111601056 A 说 明 书 3/6 页 进一步的,所述第二电压转换电路的转换增益由采样电容的容值决定。 进一步的,所述像素子阵列为2×2的阵列。 有益效果:本发明中,对在半浮栅图像传感器中增加了电压列级处理电路,在各像 素或像素子阵列中增加了电压转换电路,使图像传感器能够兼顾大满阱电荷容量和高转换 增益,同时实现了像素级相关双采样,降低了读出噪声,在高背景和低背景下均可成像,极 大的扩展了半浮栅图像传感器的应用范围;另外,还可以实现像素间的Binning,进一步扩 展图像传感器的动态范围。。 附图说明 图1为本发明的结构框图; 图2为本发明一个实施例的电路结构图; 图3为图2中控制信号的时序图; 图4为本发明另一实施例的电路结构图。