技术摘要:

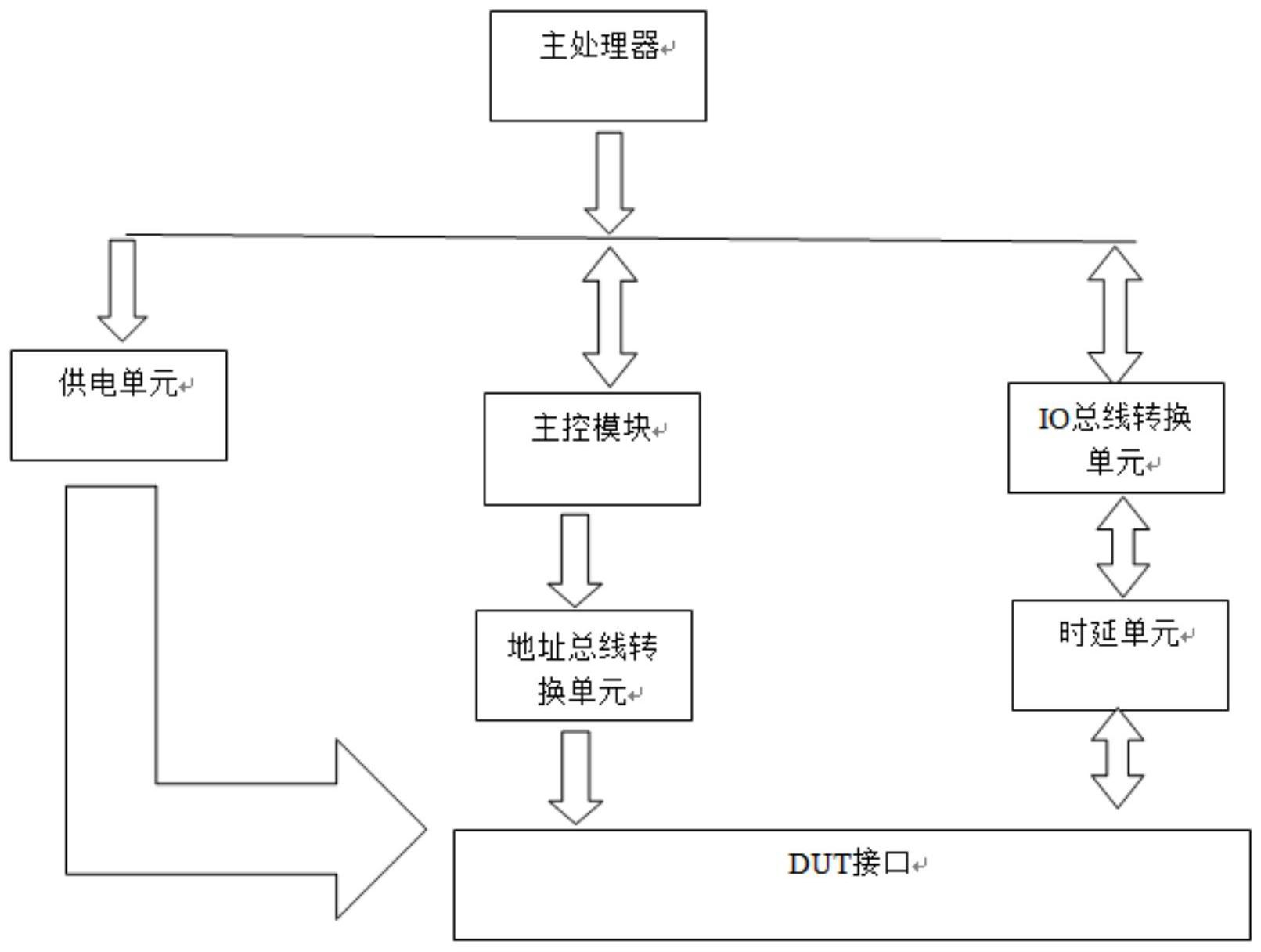

本发明公开了一种集成电路测试仪,该测试仪包括主处理器、主控模块、被测试芯片接口,还包括供电单元,时延单元,主控模块经过时延单元把产生的被测试芯片所需要的数据信号提供给被测试芯片,或者主控模块通过时延单元读取被测试芯片提供的数据信号,时延单元同地址信号 全部

背景技术:

在大规模集成电路产品测试开发过程中,均涉及到使用测试平台的选择问题。针 对SOC(系统级芯片),NVM(非挥发性存储器件)的测试,目前市场上的主流测试仪有泰瑞达 的J750系列,爱德万的93000系列,T2000,IMS,T6/T5系列等等。这些测试仪针对测试速度方 面,基本要靠改变测试仪内部CPU的运行速度来实现测试速度的提升。在进行产品的速度测 试时,根据测试仪CPU所能提供的速度,在程序中设定相应的Timing set(时序设置)来进行 针对产品的速度测试。测试仪一般只能在一个测试向量中定义多组不同的Timing set,实 现不同速度的测试;或者在不同的测试向量中定义不同的Timing set,实现不同速度的测 试;又或者在测试向量中定义相同的Timing set,在主程序测试不同的项目中,改变Timing set的值,实现不同速度的测试。不能做到在整个测试程序所有测试项目实现任意时间点实 时变动速度的测试。

技术实现要素:

本发明要解决的技术问题是提供一种集成电路测试仪,所述集成电路测试仪能便 捷实现任意时间点读写速度变动的测试。可真实的模拟芯片在实际使用中的各种恶劣条 件。 为解决上述技术问题,本发明地集成电路测试仪,包括主处理器、主控模块、被测 试芯片接口,供电单元,时延单元。 时延单元同地址信号配合控制读写被测试芯片数据信号的速度,其速度变动范围 及每次变动的时间间隔在测试程序主程序中定义。 当测试程序下载并开始测试时,主处理器通过对时延单元的操控实现测试中测试 速度实时变动的控制。 在整个测试程序的测试流程中均可实现测试项目速度变动的测试。改动测试速度 变动测试只要在测试程序的主程序控制,无需修改测试向量。 在一个测试程序的测试流程中,当监控到有测试速度变动的触发信号时,印加到 被测试芯片的读写速度实时变动,直到测试速度变动的触发信号消失。 本发明采用了简易的设计理念,可以方便的实现实时速度变动测试。 附图说明 下面结合附图及