技术摘要:

本发明公开了一种晶圆级芯片结构、多芯片堆叠互连结构及制备方法,其中晶圆级芯片结构,包括:贯穿晶圆的硅通孔,其第一表面包括:有源区、多层再分布线层以及凸点,其第二表面包括:绝缘介质层,以及与硅通孔相连接的锥台过渡结构。本发明实施例在晶圆背面TSV露头区域 全部

背景技术:

近年来,在利用TSV(Through Silicon Via,硅通孔)以及微凸点进行多层芯片3D 堆叠应用中,上下堆叠芯片层之间的电信号传输路径为:上层芯片层的RDL、上层芯片层内 埋垂直互连(TSV)、上下层芯片间键合微凸点、下层芯片UBM、下层芯片内埋垂直互连(TSV) 和下层芯片层的RDL。在信号传输路径上,传输线路阻抗在发生不断变化,而阻抗的变化和 波动,将会对信号传输质量产生显著影响,如高比特率信号眼图张开幅度降低、传输噪声增 大,甚至信号畸变等。 目前,随着高性能计算、AI、5G等应用对存储带宽的要求越来越高,采用多层DRAM 垂直堆叠实现的HBM模组结构,越来越成为主流解决方案。但是,在目前该领域主流供应商 提供的解决方案中,均采用DRAM堆叠层的背面TSV露头区域直接和UBM(Under bumping metallization,凸点下金属化层)互连的形式,考虑到TSV直径约6um,而UBM直径约20~ 30um,两者之间直接互连,阻抗呈现出明显的突变。另外,随着TSV直径越来越小,而UBM受限 于共晶凸点直径和节距(相邻凸点中心对中心之间的距离)缩小的困难,两者之间的阻抗失 配将越来越大,将显著影响高比特率信号传输质量。

技术实现要素:

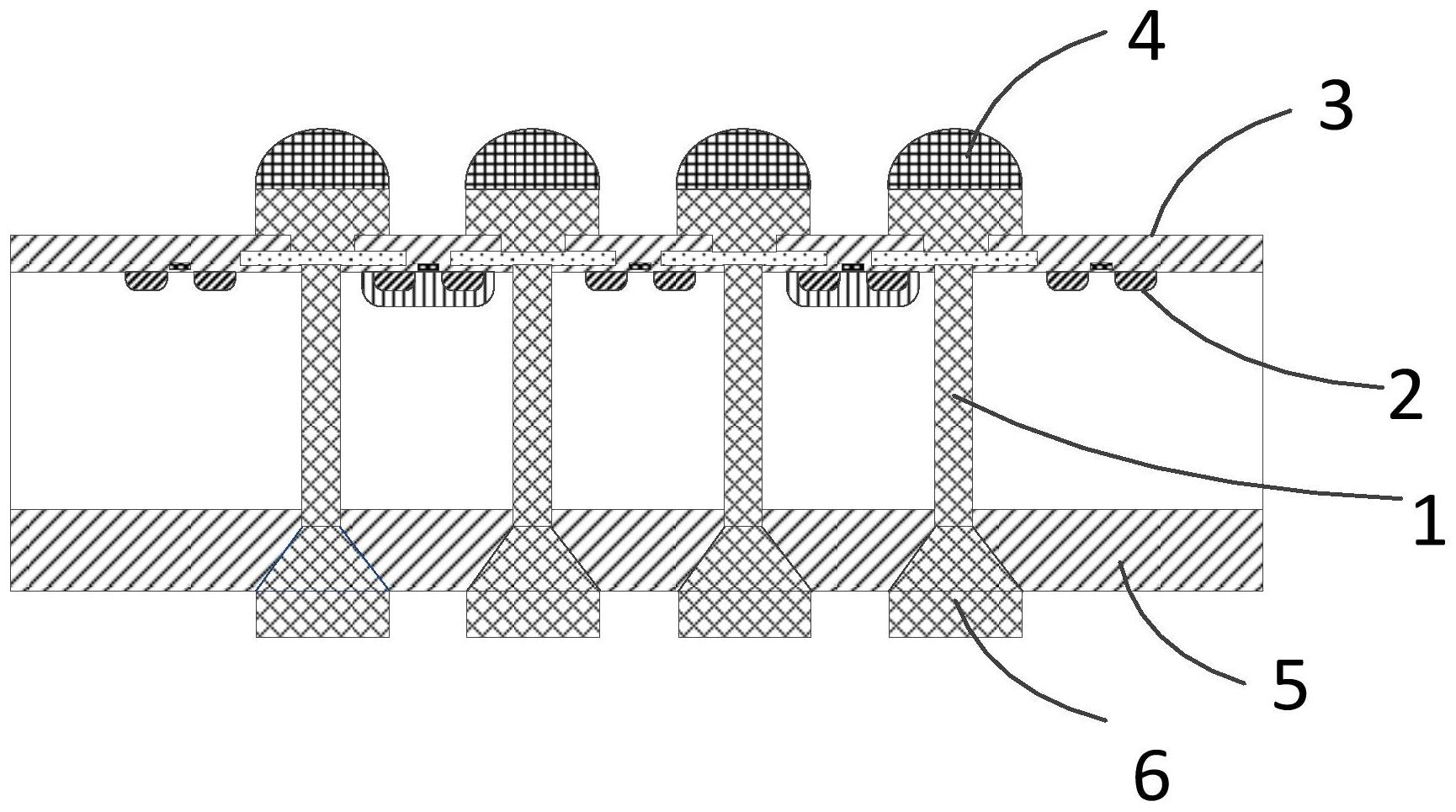

因此,本发明提供一种晶圆级芯片结构、多芯片堆叠互连结构及制备方法,克服现 有技术中的在3D芯片封装或晶圆级封装时,信号在传输路径阻抗在发生不断变化,导致对 信号传输质量产生显著影响的缺陷。 第一方面,本发明提供一种晶圆级芯片结构,包括:贯穿晶圆的硅通孔,其第一表 面包括:有源区、多层再分布线层以及凸点,其第二表面包括:绝缘介质层,以及与硅通孔相 连接的锥台过渡结构。 在一实施例中,所述锥台过渡结构一端开口直径根据与之相连的硅通孔尺寸确 定,另一端开口直径根据键合凸点尺寸确定。 第二方面,本发明实施例提供一种晶圆级多芯片堆叠互连结构,包括:芯片键合 体、基板及引出端子,所述芯片键合体转接于所述基板的第一表面,引出端子形成于所述基 板的第二表面,其中, 芯片键合体,包括堆叠设置的多个单体晶圆级芯片,多个单体晶圆级芯片直接通 过键合层连接,所述单体晶圆级芯片包括:一个第一芯片结构、一个第二芯片结构及至少一 个第三芯片结构,所述第一芯片结构和第二芯片结构分别位于所述芯片键合体的两端,所 述至少一个第三芯片结构,位于第一芯片结构和第二芯片结构之间; 所述第三芯片结构为第一方面所述的晶圆级芯片结构。 4 CN 111554647 A 说 明 书 2/6 页 在一实施例中,所述第一芯片结构,包括:未完全贯穿晶圆的硅通连接结构,其第 一表面包括:有源区、多层再分布线层以及凸点,第二表面为晶圆面; 所述第二芯片结构,包括:贯穿晶圆的硅通孔,其第一表面包括:有源区、多层再分 布线层以及凸点,其第二表面为包含多个硅通孔连接的晶圆面。 在一实施例中,第一芯片结构、第二芯片结构及第三芯片结构的第一表面均包括: 非导电胶膜层,包覆所述凸点,所述非导电胶膜层的厚度大于所述凸点的高度; 所述键合层包括:单体晶圆级芯片之间的凸点连接及包覆所述凸点连接的非导电 胶膜层。 在一实施例中,所述晶圆级多芯片堆叠互连结构还包括: 塑封层,基于基板级的包覆所述芯片键合体。 第三方面,本发明实施例提供一种晶圆级芯片结构的制备方法,包括如下步骤: 在晶圆的第一表面依次制备有源区、硅通孔、多层再分布线层及凸点; 对晶圆第二表面进行减薄抛光处理,直至所有硅通孔均露出; 利用深反应离子刻蚀工艺,在晶圆第二表面实现无掩膜刻蚀,使硅通孔相对于晶 圆第二表面整体凸起; 在晶圆第二表面实现绝缘介质层沉积,并通过刻蚀掩膜层制备以及锥台型盲孔刻 蚀; 在晶圆第二表面,依次进行阻挡层、种子层及凸点下金属化层的制备,形成所述晶 圆级芯片结构。 第四方面,本发明实施例提供一种晶圆级多芯片堆叠互连结构的制备方法,包括 如下步骤: 在晶圆的第一表面依次制备有源区、硅通孔、多层再分布线层及凸点,形成第一芯 片结构; 在第一芯片结构的基础上,对晶圆第二表面进行减薄抛光处理,直至所有硅通孔 均露出,形成第二芯片结构; 根据第三方面所述的晶圆级芯片结构的制备方法,形成第三芯片结构; 在基板第一表面依次将第二芯片结构、至少一个第三芯片结构、第一芯片结构基 于凸点连接键合堆叠; 在基板第二表面制备引出端子,形成晶圆级多芯片堆叠互连结构。 在一实施例中,在制备第一芯片结构及第二芯片结构时,在晶圆的第一表面依次 制备有源区、硅通孔、多层再分布线层及凸点的步骤之后,还包括:制备非导电胶膜层,包覆 所述凸点,所述非导电胶膜层的厚度大于所述凸点的高度; 形成第三芯片结构的步骤之后,还包括:制备非导电胶膜层,包覆所述凸点,所述 非导电胶膜层的厚度大于所述凸点的高度。 在一实施例中,将第二芯片结构、至少一个第三芯片结构、第一芯片结构基于凸点 连接键合堆叠的步骤之后,还包括:制备塑封层,对第二芯片结构、至少一个第三芯片结构、 第一芯片结构基于凸点连接键合堆叠形成的芯片键合体进行基板级塑封。 在一实施例中,所述在基板第二表面制备引出端子的步骤之后,还包括:对晶圆级 多芯片堆叠互连结构进行切割,形成单颗晶圆级芯片结构。 5 CN 111554647 A 说 明 书 3/6 页 1、本发明提供的晶圆级芯片结构及制备方法,在晶圆背面TSV露头区域与UBM之间 引入锥台型阻抗过渡结构,使TSV与UBM之间实现阻抗匹配,改善了因阻抗突变引起的信号 畸变问题,和传统方案相比,为了实现本方案的锥台型过渡结构,并未增加光罩数量,而仅 在原有工艺基础上,增加一步光刻工艺以及一步反应离子刻蚀工艺,工艺流程并不复杂。 2、本发明提供的晶圆级多芯片堆叠互连结构及制备方法,将不同结构的单体晶圆 级芯片进行堆叠键合,不同芯片键合的过渡区域引入锥台型阻抗过渡结构,改善了因阻抗 突变引起的信号畸变问题,键合层引入了非导电胶膜层可以改善单体晶圆级芯片在堆叠键 合时不同凸点之间的桥接问题。 附图说明 为了更清楚地说明本发明