技术摘要:

本发明提供了一种分栅快闪存储器及其形成方法,在所述隧穿氧化层上生长多晶硅层并在所述多晶硅层中掺杂;所述多晶硅层的顶部不掺杂,或者,在厚度方向上,所述多晶硅层的顶部的掺杂浓度小于所述多晶硅层的底部的掺杂浓度;刻蚀所述多晶硅层形成字线层。多晶硅层被刻蚀 全部

背景技术:

快闪存储器包括两种基本结构:栅极叠层(stack gate)和分栅(split gate)器 件。分栅器件在浮栅的一侧形成作为擦除栅极的字线,字线作为选择栅,在擦写性能上,分 栅器件有效的避免了叠栅器件的过擦除效应,电路设计相对简单。而且分栅结构利用源端 热电子注入进行编程,具有更高的编程效率,因而被广泛应用在各类诸如智能卡、SIM卡、微 控制器、手机等电子产品中。 在分栅快闪存储器中,字线多晶硅层的厚度和宽度影响着分栅闪存的抗干扰性 能,而字线多晶硅层的宽度又与其厚度密切相关。如果字线多晶硅层的厚度过薄,会导致分 栅快闪存储器出现编程串扰失效,例如列穿通串扰失效(column punch-through disturb)。 实际工艺中,分栅快闪存储器的晶圆边缘随机遭受编程串扰失效,失效样品如图1 所示,刻蚀多晶硅层形成字线层01,字线层01的顶部轮廓具有凹陷a,失效样品显示出较低 的凹陷a,凹陷a越低,字线层01的厚度越薄,字线层01过薄的话,字线层的阈值电压会降低, 同时,源漏离子注入时将会穿透字线层01;且字线层的厚度影响着快闪存储器的抗干扰性 能。字线01的厚度过薄,易造成分栅快闪存储器编程串扰失效问题。

技术实现要素:

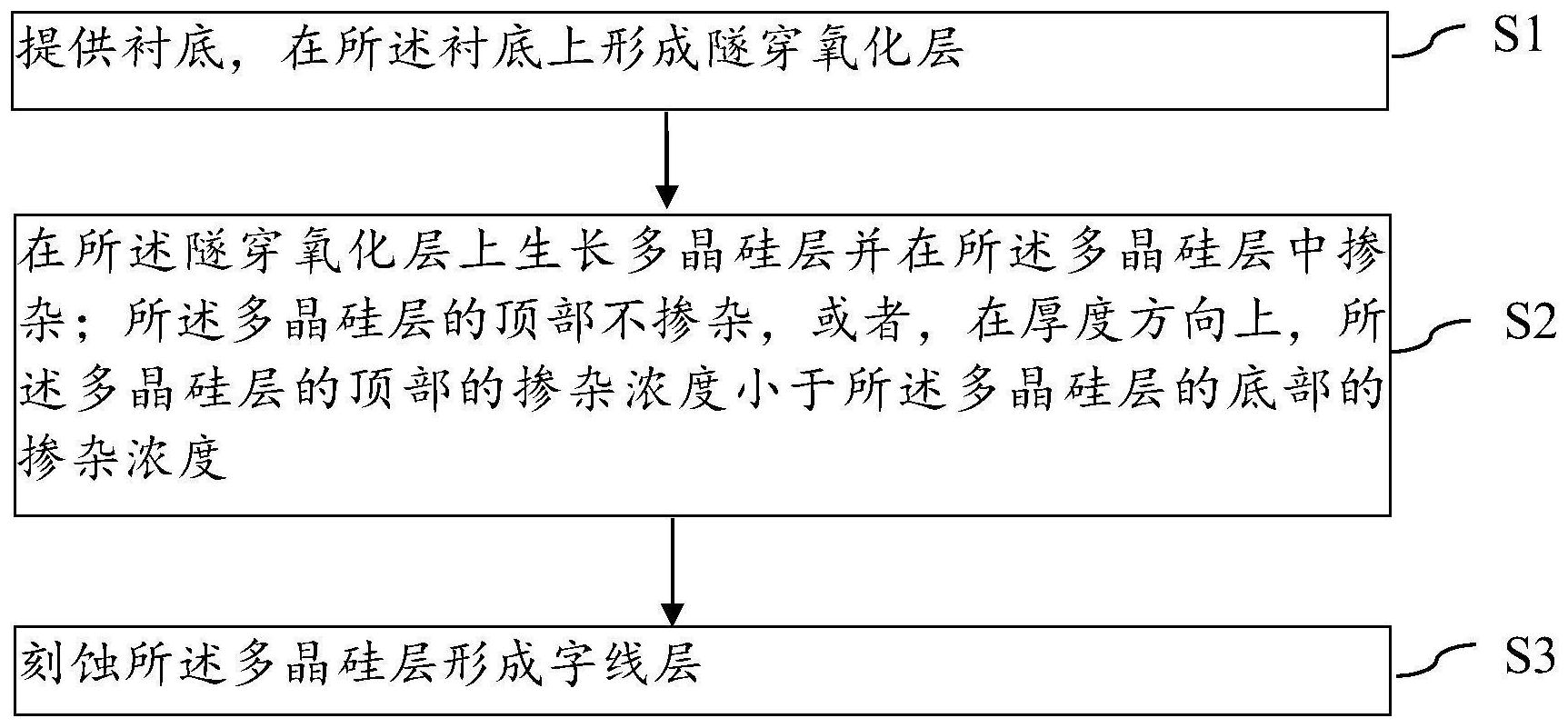

本发明的目的在于提供一种分栅快闪存储器及其形成方法,解决分栅快闪存储器 编程串扰失效问题,同时增大源漏离子注入的工艺窗口。 本发明提供一种分栅快闪存储器的形成方法,包括: 提供衬底,在所述衬底上形成隧穿氧化层; 在所述隧穿氧化层上生长多晶硅层并在所述多晶硅层中掺杂;所述多晶硅层的顶 部不掺杂,或者,在厚度方向上,所述多晶硅层的顶部的掺杂浓度小于所述多晶硅层的底部 的掺杂浓度;以及 刻蚀所述多晶硅层形成字线层。 进一步的,厚度方向上,从靠近所述隧穿氧化层一侧到远离所述隧穿氧化层一侧, 所述多晶硅层的掺杂浓度逐渐降低。 进一步的,所述多晶硅层在一次炉管中生长形成,且生长所述多晶硅层的过程中, 掺杂气体的浓度逐渐降低。 进一步的,所述多晶硅层依次在N次炉管中分段生长形成,第一次炉管中形成第一 厚度的多晶硅层,第二次炉管中形成第二厚度的多晶硅层,以此类推,第N次炉管中形成第N 厚度的多晶硅层;第一次炉管至第N次炉管中的掺杂气体的浓度逐次降低,第N次炉管中掺 3 CN 111599814 A 说 明 书 2/5 页 杂气体浓度最低或者不掺杂;第一厚度、第二厚度至第N厚度的和等于所述多晶硅层的总厚 度。 进一步的,生长所述多晶硅层的反应气体源包括:甲硅烷、二氯化硅烷、三氯化硅 烷与四氯化硅所组成的族群中任意一个或两个以上的组合。 进一步的,所述掺杂气体包括磷烷或硼烷。 进一步的,所述多晶硅层采用N型掺杂或P型掺杂。 本发明还提供一种分栅快闪存储器,包括: 衬底; 位于所述衬底上的隧穿氧化层; 位于所述隧穿氧化层上的字线层,所述字线层由多晶硅层掺杂构成,所述多晶硅 层的顶部不掺杂,或者,在厚度方向上,所述多晶硅层的顶部的掺杂浓度小于所述多晶硅层 的底部的掺杂浓度。 进一步的,厚度方向上,从靠近所述隧穿氧化层一侧到远离所述隧穿氧化层一侧, 所述多晶硅层的掺杂浓度逐渐降低。 进一步的,所述衬底上设有源线层和浮栅氧化层,所述浮栅氧化层表面沉积有浮 栅多晶硅层,所述源线层与字线层之间设有第一侧墙,所述源线层与所述浮栅氧化层和浮 栅多晶硅层之间设有第二侧墙。 与现有技术相比,本发明具有如下有益效果: 本发明提供的分栅快闪存储器及其形成方法中,在所述隧穿氧化层上生长多晶硅 层并在所述多晶硅层中掺杂;所述多晶硅层的顶部不掺杂,或者,在厚度方向上,所述多晶 硅层的顶部的掺杂浓度小于所述多晶硅层的底部的掺杂浓度;刻蚀所述多晶硅层形成字线 层。多晶硅层被刻蚀的速率与多晶硅层的掺杂浓度正相关,多晶硅层的顶部不掺杂或者多 晶硅层的顶部具有较小的掺杂浓度,如此一来,多晶硅层的顶部具有较低的刻蚀速率,这有 利于凹陷高度的提高,从而增大形成字线层的厚度。字线层的厚度增加,有效解决分栅快闪 存储器编程串扰失效问题;同时,字线层的厚度增加,源漏离子注入时将不会穿透字线层, 增大源漏离子注入的工艺窗口。 附图说明 图1为一种分栅快闪存储器字线层的顶部较低的凹陷的示意图。 图2为本发明实施例的分栅快闪存储器形成方法流程示意图。 图3至图8为本发明实施例的分栅快闪存储器形成方法各步骤示意图。 其中,附图标记如下: 11-衬底;111-源区12-源线层;13-浮栅氧化层;14-浮栅多晶硅层;15-第一侧墙; 16-第二侧墙;17-隧穿氧化层;18-多晶硅层;18’-字线层;19-多晶硅层;20-多晶硅层;21- 字线侧墙;22-漏区。