技术摘要:

本申请提供一种半导体模块封装方法及半导体模块。该半导体模块封装方法包括:将芯片、被动件贴装于DBC板的第一导电金属层上;将所述DBC板贴装于载板上;通过包封层覆盖在整个所述载板上,对所述芯片、所述被动件以及所述DBC板进行塑封形成包封结构件;在所述包封结构件 全部

背景技术:

塑封式IPM模块(IntelligentPowerModule,智能功率模块)是将IGBT(Insulated GateBipolarTransistor,绝缘栅双极型晶体管)芯片及其驱动电路、控制电路和过流、欠 压、短路、过热等保护电路集成于一体的新型控制模块。 塑封式IPM模块是一种复杂、先进的功率模块,能自动实现过流、欠压、短路和过热 等复杂保护功能,因而具有智能特征。同时它具有低成本、小型化、高可靠、易使用等优点, 广泛应用于变频家电、逆变电源、工业控制等领域,社会效益和经济效益十分可观。 对于塑封式IPM模块来说,如图1所示,其内部通常设有DBC板30’和引线框架40’, 通过将芯片11’及被动件12’固定在引线框架40’上制作封装结构,同时通过引线20’键合完 成电气连接的功能,然后将封装结构固定在DBC板30’上,DBC板30’与引线框架40’之间是通 过焊接的方式完成固定和电气连接的,最后通过引线框架40’的引脚41’实现外部电气连 接。 但是,现有技术中的IPM模块由于需要引线框架而造成散热效果不佳、体积较大, 而且由于通过引线互连封装结构内的电子元件以及引线框架,存在产出效率低、通流能力 差的问题。

技术实现要素:

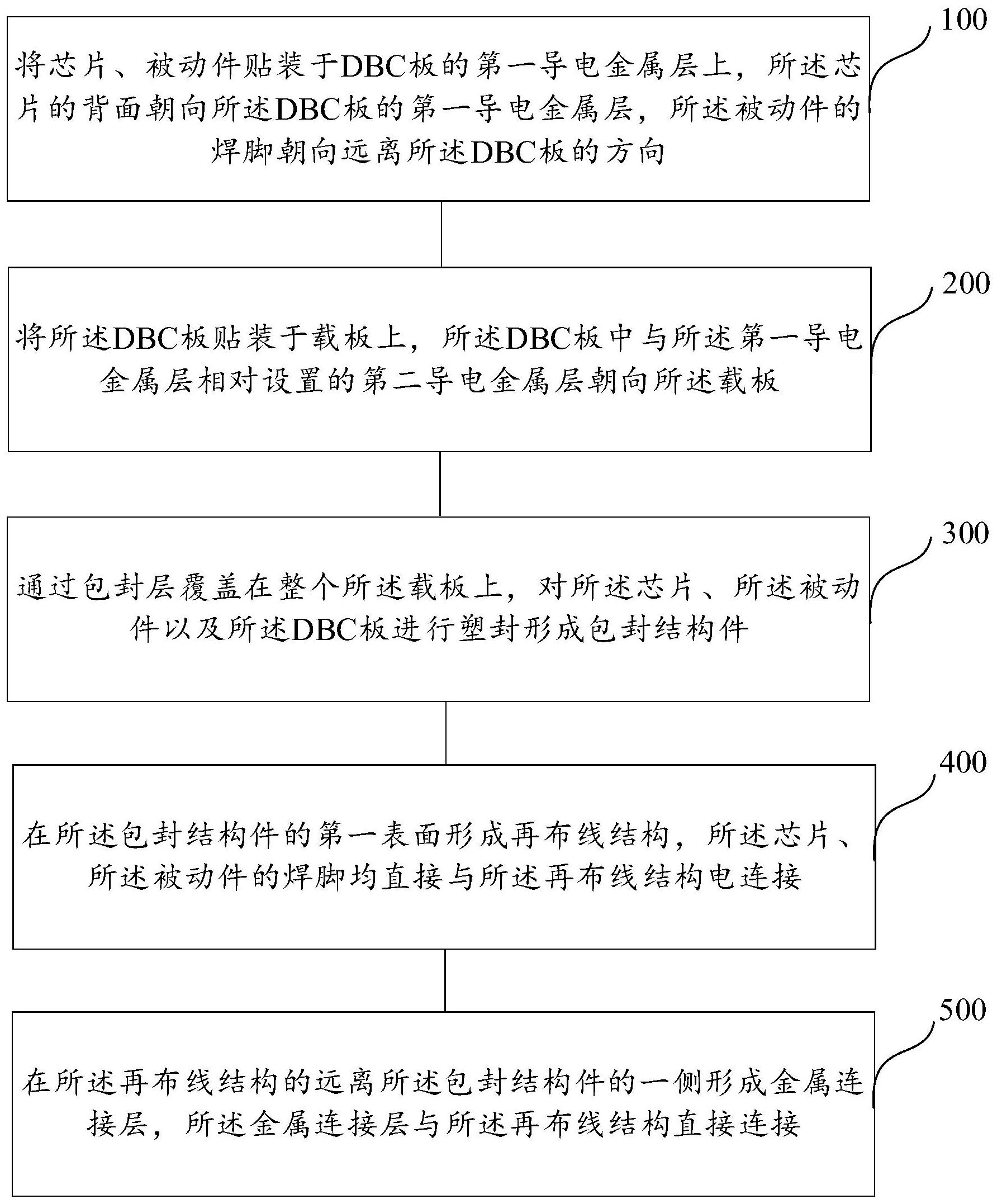

本申请的一个方面提供半导体模块封装方法,其包括: S1:将芯片、被动件贴装于DBC板的第一导电金属层上,所述芯片的背面朝向所述 DBC板的第一导电金属层; S2:将所述DBC板贴装于载板上,所述DBC板中与所述第一导电金属层相对设置的 第二导电金属层朝向所述载板; S3:通过包封层覆盖在整个所述载板上,对所述芯片、所述被动件以及所述DBC板 进行塑封形成包封结构件; S4:在所述包封结构件的第一表面形成再布线结构,所述芯片、所述被动件的焊脚 均直接与所述再布线结构电连接。 可选的,所述包封结构件包括相对设置的所述第一表面和第二表面,所述第二表 面朝向所述载板,在步骤S3中,包括: 对所述包封结构件的第一表面进行研磨,使所述被动件的焊脚露出于所述包封结 构件的第一表面。 可选的,在步骤S4中,包括: S41:在所述包封结构件的第一表面依次形成第一再布线层和导电凸柱,所述芯 4 CN 111599698 A 说 明 书 2/10 页 片、所述被动件的焊脚均与所述第一再布线层电连接; S42:在所述第一再布线层以及露出的所述包封结构件的第一表面上形成第一介 电层,并使所述导电凸柱远离所述第一再布线层的一端露出于所述第一介电层远离所述包 封结构件的一表面。 可选的,在步骤S42中包括: 在所述第一再布线层、所述导电凸柱、以及露出的所述包封结构件的第一表面上 形成第一介电层; 对所述第一介电层中远离所述包封结构件的一表面进行研磨,使所述导电凸柱远 离所述第一再布线层的一端露出于所述第一介电层远离所述包封结构件的一表面。 可选的,在步骤S42之后,还包括: S43:在所述第一介电层以及所述导电凸柱上形成第二再布线层; S44:在所述第一介电层上形成第二介电层,并使所述第二再布线层远离所述导电 凸柱的一端露出于所述第二介电层远离所述第一介电层的一表面露出。 在步骤S44中包括: 在所述第二再布线层以及露出的所述第一介电层上形成第二介电层; 对所述第二介电层中远离所述包封结构件的一表面进行研磨,使所述第二再布线 层远离所述第一再布线层的一端露出于所述第二介电层远离所述包封结构件的一表面。 可选的,在步骤S4之后还包括: S5:在所述再布线结构的远离所述包封结构件的一侧形成金属连接层,所述金属 连接层与所述再布线结构直接连接。 可选的,在步骤S5之前,还包括:剥离所述载板;或者, 在步骤S5之后,还包括:剥离所述载板。 本申请的第二个方面提供一种半导体模块,其包括: 包封结构件,包括相对的第一表面和第二表面,且设有内凹的腔体,DBC板、芯片、 被动件均位于所述腔体内,所述DBC板包括相对设置的第一导电金属层和第二导电金属层, 所述芯片、所述被动件均固定于所述DBC板的第一导电金属层,所述DBC板的第二导电金属 层露出于所述包封结构件的第二表面,所述芯片包括相对设置的正面和背面,所述芯片的 正面朝向所述腔体的底部,所述被动件的焊脚朝向远离所述DBC板的方向; 再布线结构,对应于所述芯片的正面形成于所述包封结构件的第一表面,所述芯 片、所述被动件均直接与所述再布线结构电连接。 可选的,所述半导体模块还包括金属连接层,所述金属连接层位于所述再布线结 构远离所述包封结构件的一表面,且与所述再布线结构直接连接。 可选的,沿所述半导体模块的厚度方向,所述被动件的厚度不小于所述芯片的厚 度;所述被动件的焊脚露出于所述包封结构件的第一表面。 可选的,所述再布线结构包括: 第一再布线层,形成于所述包封结构件的第一表面,所述芯片、所述被动件的焊脚 均与所述第一再布线层电连接; 导电凸柱,形成于所述第一再布线层远离所述包封结构件的一侧; 第一介电层,形成于所述第一再布线层以及露出的所述包封结构件的第一表面 5 CN 111599698 A 说 明 书 3/10 页 上,且所述导电凸柱远离所述包封结构件的一端露出于所述第一介电层远离所述包封结构 件的一表面。 可选的,所述再布线结构还包括: 第二再布线层,形成于所述第一介电层上,所述第二再布线层与所述导电凸柱电 连接; 第二介电层,形成于所述第一介电层上,且所述第二再布线层远离所述导电凸柱 的一端露出于所述第二介电层远离所述第一介电层的一表面露出。 本申请实施例提供的上述半导体模块封装方法及半导体模块,相对于现有技术, 由于半导体模块中不需要引线框架,从而大大地缩小了半导体模块的整体体积以及产品成 本,使半导体模块具有体积小、结构紧凑的优势,适合小型轻量电子设备;由于被动件的焊 脚直接与再布线结构电连接,大大地减少了线路长度,从而减少了阻抗、增加了通流能力; 通过DBC板和再布线结构实现双面散热;且由于无引线互连,能够减少阻抗、增加通流能力, 布局更自由灵活;同时产品厚度自由可控,无需独立塑封模具,产品尺寸切换自由。 附图说明 图1为现有技术中的IPM模块的剖面图。 图2是根据本申请的实施例1提出的半导体模块封装方法的流程图。 图3(a)-图3(s)是根据本申请的实施例1提出的中半导体模块封装方法的工艺流 程图。 图4是根据本申请的实施例1提出的利用上述半导体模块封装方法得到的半导体 模块的结构示意图。 图5(a)-图5(j)是根据本申请的实施例2中半导体模块封装方法的工艺流程图。 图6是根据本申请的实施例2提供的利用上述半导体模块封装方法得到的半导体 模块的结构示意图。