技术摘要:

一种阵列基板和其制作方法,以及一种显示面板,所述阵列基板包括与软性电路板相连接的侧面绑定结构,所述软性电路板包括驱动晶片,所述侧面绑定结构与所述驱动晶片通过所述软性电路板电性连接。所述侧面绑定结构包括第一区域和第二区域,所述第一区域包括衬底、多层非 全部

背景技术:

随着液晶显示屏(liquid crystal display,LCD)技术的不断发展,消费者对于轻 薄化电子产品的屏占比要求越来越高,全面屏已成为移动终端发展的主流。因此,人们开发 了各种微型组件技术,例如:覆晶玻璃(chip on glass ,COG)技术和覆晶薄膜(chip on film ,COF)技术。具体地,COG技术是将驱动晶片绑定在薄膜电晶体阵列基板(TFT array substrate)的玻璃底板之上,而COF技术是将驱动晶片绑定在软性板上,再将软性版与薄膜 电晶体阵列基板(TFT array substrate)的玻璃基板连接。然而,无论是COG技术或COF技术 均无法满足全面屏的需求,促使了侧面绑定技术的诞生。 传统侧面绑定技术受限于薄膜电晶体阵列基板(TFT array substrate)侧面金属 面积(通常仅有栅极层与软性版连接),使得导电离子个数较少,器件的导通性较差。

技术实现要素:

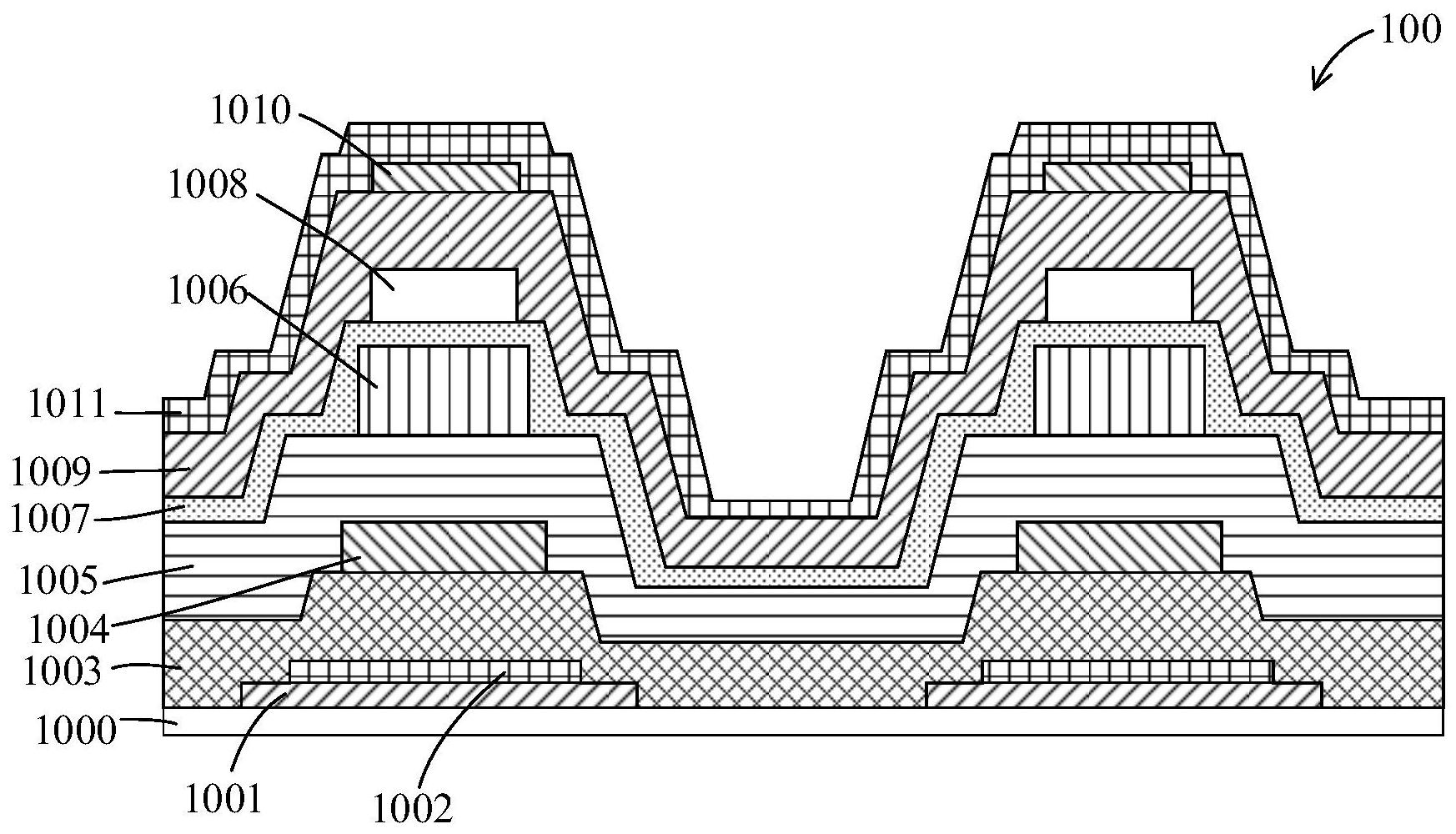

本申请的目的在于提供一种阵列基板和其制作方法,以及一种显示面板,通过掩 模板对薄膜电晶体阵列基板(TFT array substrate)的侧面膜层进行优化,大幅度提升了 绑定区域的导通面积。 本申请提供一种阵列基板,包括与软性电路板相连接的侧面绑定结构,所述软性 电路板包括驱动晶片,所述侧面绑定结构与所述驱动晶片通过所述软性电路板电性连接; 其中,所述侧面绑定结构包括第一区域和第二区域,所述第一区域包括衬底、多层 非金属膜层和多层金属膜层,所述第二区域包括所述衬底和所述多层金属膜层。 根据本发明的一个实施例,所述第一区域内之所述多层金属膜层与所述第二区域 内之所述多层金属膜层为连续的结构。 根据本发明的一个实施例,所述第一区域从下至上包括:所述衬底、复合层、栅级 绝缘层、栅级层、层间介电层、第一金属层、平坦层、第一氧化铟锡层、层间绝缘层、第二金属 层、钝化层以及第二氧化铟锡层。 根据本发明的一个实施例,所述第二区域从下至上包括:所述衬底、栅级层、第一 金属层、第一氧化铟锡层、第二金属层以及第二氧化铟锡层。 根据本发明的一个实施例,所述侧面绑定结构与所述软性电路板通过焊接的方式 相连接。 进一步地,本申请还提供一种阵列基板的制作方法,包括以下步骤: 提供衬底; 在所述衬底之上沉积复合层,在所述复合层之上沉积栅级绝缘层; 使用掩模板将第二区域内之所述复合层和所述栅级绝缘层刻蚀; 4 CN 111584518 A 说 明 书 2/5 页 在第一区域内之所述栅级绝缘层之上和所述第二区域内之所述衬底之上沉积栅 级层; 在所述栅级层之上沉积层间介电层,使用掩模板将所述第二区域内之所述层间介 电层刻蚀; 在所述第一区域内之所述层间介电层之上和所述第二区域内之所述栅极层之上 沉积第一金属层; 在所述第一金属层之上沉积平坦层,使用掩模板将所述第二区域内之所述平坦层 刻蚀; 在所述第一区域内之所述平坦层之上和所述第二区域内之所述第一金属层之上 沉积第一氧化铟锡层; 在所述第一氧化铟锡层之上沉积层间绝缘层,使用掩模板将所述第二区域内之所 述层间绝缘层刻蚀; 在所述第一区域内之所述层间绝缘层之上和所述第二区域内之所述第一氧化铟 锡层之上沉积第二金属层; 在所述第二金属层之上沉积钝化层,使用掩模板将所述第二区域内之所述钝化层 刻蚀;以及 在所述第一区域内之所述钝化层之上和所述第二区域内之所述第二金属层之上 沉积第二氧化铟锡层。 进一步地,本申请还提供一种显示面板,包括阵列基板、彩膜基板以及设置在所述 阵列基板和所述彩膜基板之间的液晶层,所述阵列基板包括与软性电路板相连接的侧面绑 定结构,所述软性电路板包括驱动晶片,所述侧面绑定结构与所述驱动晶片通过所述软性 电路板电性连接; 其中,所述侧面绑定结构包括第一区域和第二区域,所述第一区域包括衬底、多层 金属膜层和多层金属膜层,所述第二区域包括所述衬底和所述多层金属膜层。 根据本发明的一个实施例,所述第一区域内之所述多层金属膜层与所述第二区域 内之所述多层金属膜层为连续的结构。 根据本发明的一个实施例,所述第一区域从下至上包括:所述衬底、复合层、栅级 绝缘层、栅级层、层间介电层、第一金属层、平坦层、第一氧化铟锡层、层间绝缘层、第二金属 层、钝化层以及第二氧化铟锡层。 根据本发明的一个实施例,所述第二区域从下至上包括:所述衬底、栅级层、第一 金属层、第一氧化铟锡层、第二金属层以及第二氧化铟锡层。 本申请提供了一种阵列基板和其制作方法,以及一种显示面板,通过掩模板对薄 膜电晶体阵列基板(TFT array substrate)的侧面膜层进行优化,大幅度提升了绑定区域 的导通面积,解决了传统侧面绑定技术受限于薄膜电晶体阵列基板(TFT a rray substrate)侧面金属面积,使得导电离子个数较少,器件的导通性较差的问题。 附图说明 为了更清楚地说明实施例或现有技术中的技术方案,下面将对实施例或现有技术 描述中所需要使用的附图作简单介绍,显而易见地,下面描述中的附图仅仅是发明的一些 5 CN 111584518 A 说 明 书 3/5 页 实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附 图获得其他的附图。 附图中, 图1为本申请实施例所提供的阵列基板之侧面绑定结构的剖面示意图。 图2为本申请实施例所提供的阵列基板的制作方法的步骤流程图。 图3为本申请实施例所提供的显示面板的透视示意图。 图4为本申请实施例所提供的显示面板的侧视图。